# Institute of Parallel and Distributed Systems Department Simulation of Large Systems University of Stuttgart Universitätsstraße 38 D-70569 Stuttgart

Diplomarbeit Nr. 3405

# GPU-based Numerical Integration in the Partition of Unity Method

Sebastian Kanis

Course of Study: Computer Science

**Examiner:** Prof. Dr. rer. nat. Marc Alexander Schweitzer

**Supervisor:** Dipl. Inf. Patrick Diehl

Commenced: Oktober 16, 2012

Completed: April 17, 2013

**CR-Classification:** G.4, J.2

#### Abstract

In this thesis, we present a CUDA-implementation of two sub-steps of the Parallel Multilevel Partition of Unity Method (PMPUM). The PMPUM is a method for the approximation of partial differential equations (PDEs) whose main computational effort is caused by the integration of the weak formulation. Therefore, an efficient CUDA-implementation of the required steps could speed up a given PMPUM-implementation. The core of this thesis is the analysis of the applicability of CUDA in the PMPUM. To this end the required steps, the decomposition of the domain and the integration, were implemented using CUDA. The analysis showed, that the usage of CUDA can speed up the implementation and identified the limitations of the implementation. We give recommendations how to improve these limitations and expect the performance to increase further with these recommendations applied.

# Contents

| 1 | Intro | oduction                                                             | 15 |

|---|-------|----------------------------------------------------------------------|----|

| 2 | The   | Parallel Multilevel Partition of Unity Method                        | 17 |

|   | 2.1   | Model Problem                                                        | 17 |

|   | 2.2   | Partition of Unity Space                                             | 18 |

|   | 2.3   | Galerkin Discretization                                              | 19 |

|   | 2.4   | Decomposition of the Domain                                          | 20 |

|   |       | 2.4.1 Decomposition Task                                             | 20 |

|   |       | 2.4.2 Decomposers                                                    | 23 |

|   |       | 2.4.3 Comparison of the Approaches                                   | 28 |

|   | 2.5   | Complexity                                                           | 30 |

|   |       | 2.5.1 Integration                                                    | 30 |

|   |       | 2.5.2 Decomposition                                                  | 34 |

|   |       | 2.0.2 Becomposition                                                  | 01 |

| 3 | Impl  | lementation                                                          | 35 |

|   | 3.1   | CUDA                                                                 | 35 |

|   |       | 3.1.1 Execution Model                                                | 36 |

|   |       | 3.1.2 Thread Hierarchy                                               | 36 |

|   |       | 3.1.3 Memory Hierarchy                                               | 38 |

|   | 3.2   | Framework Integration                                                | 40 |

|   | 3.3   | Memory Layout                                                        | 42 |

|   | 3.4   | Kernel Design                                                        | 44 |

|   | 3.5   | Implementation Properties and Limitations                            | 45 |

|   | 0.0   |                                                                      |    |

| 4 | Resu  | ılts                                                                 | 47 |

|   | 4.1   | Hardware and Metrics                                                 | 47 |

|   |       | 4.1.1 Hardware                                                       | 47 |

|   |       | 4.1.2 Metric                                                         | 48 |

|   | 4.2   | Experiment: Overall Performance                                      | 49 |

|   | 4.3   | Experiment: Performance depending on Problem Parameters              | 51 |

|   | 4.4   | Experiment: Performance of different Steps of the GPU-Implementation | 52 |

|   | 4.5   | Experiment: Single precision Performance                             | 54 |

|   | 4.6   | Experiment: Profiler Data Analysis                                   | 56 |

|   | 4.7   | Experiment: 3D Performance                                           |    |

|   | 4.8   | Experiment: Different Hardware                                       | 60 |

|   | 4.9   | Summary of the Results                                               |    |

|   | _     | Further Improvements                                                 | 62 |

|    | 4.10.1     | GPU-based Accumulation   | 62 |

|----|------------|--------------------------|----|

|    | 4.10.2     | Improved Memory Access   | 64 |

|    | 4.10.3     | Multi Kernel Version     | 64 |

|    | 4.10.4     | Level of Parallelization | 65 |

| 5  | Conclusion |                          | 67 |

| A  | Memory La  | yout of the Result Data  | 69 |

| В  | Raw Result | Data                     | 71 |

| Bi | bliography |                          | 83 |

# List of Figures

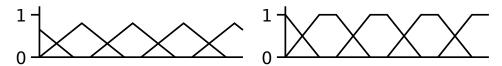

| 2.1 | The weight function $W_i$ of adjacent patches $\omega_i$ (left) and the resulting partition of unity $\varphi_i$ (right) in one space dimension  | 19 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------|----|

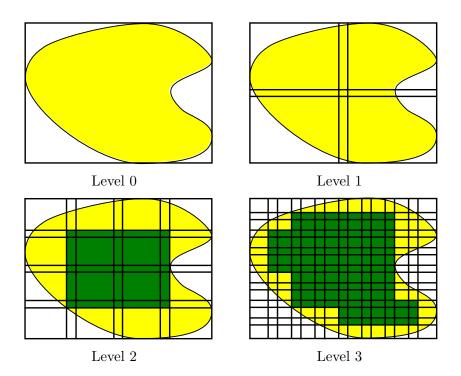

| 2.2 | The inner and boundary patches generated by an uniform refinement strategy.                                                                      | 21 |

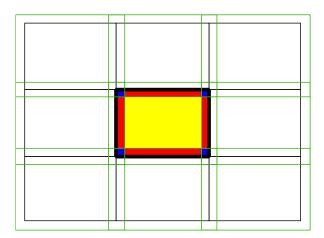

| 2.3 | The decomposition of a patch $\omega_i$ and its neighborhood $C_i$ for integration                                                               | 22 |

| 2.4 | Comparison of the decomposition of one patch $\omega_i$ and two of its neighbors $C_i$ ,                                                         |    |

|     | generated by two approaches                                                                                                                      | 29 |

| 2.5 | The cells generated by the Tree-Based Approach and Tensor-Product Approach                                                                       |    |

|     | from an uniformly refined domain.                                                                                                                | 29 |

| 2.6 | The decomposition of a patch $\omega_i$ and its neighborhood $C_i$ for integration with                                                          |    |

|     | patches on different levels                                                                                                                      | 31 |

| 2.7 | The cells generated by the Tree-Based Approach and the Tensor-Product                                                                            |    |

|     | Approach in a nonuniform case                                                                                                                    | 31 |

| 3.1 | The hardware components of a CUDA capable GPU from NVIDIA $^{\mathrm{TM}}$ with                                                                  |    |

|     | Compute Capability 2.x                                                                                                                           | 36 |

| 3.2 | The CUDA Execution Model                                                                                                                         | 37 |

| 3.3 | The CUDA Thread Hierarchy                                                                                                                        | 38 |

| 3.4 | The CUDA Memory Hierarchy                                                                                                                        | 39 |

| 3.5 | Coalesced vs. non coalesced memory access                                                                                                        | 40 |

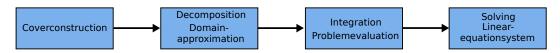

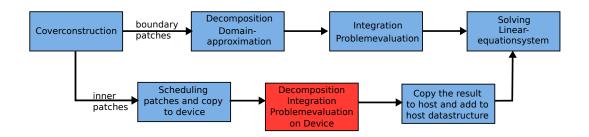

| 3.6 | The phases to solve a given BVP by the framework                                                                                                 | 40 |

| 3.7 | The phases to solve a given BVP by the framework, with the CUDA extension                                                                        | 41 |

| 3.8 | Two different memory layouts for the patches $W_i$ (2D)                                                                                          | 43 |

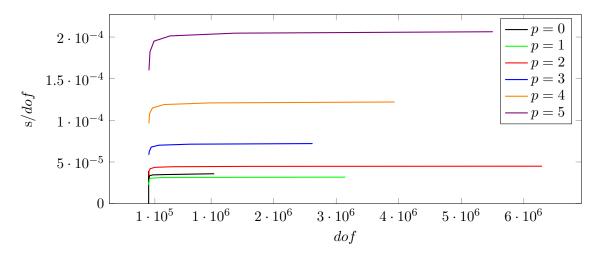

| 4.1 | The performance for the integration on $\Omega_I$ of the CPU-implementation $\mathcal{P}_{CPU}$ .                                                | 49 |

| 4.2 | The performance of the integration on $\Omega_I$ of the GPU-implementation $\mathcal{P}_{CPU}$ .                                                 | 50 |

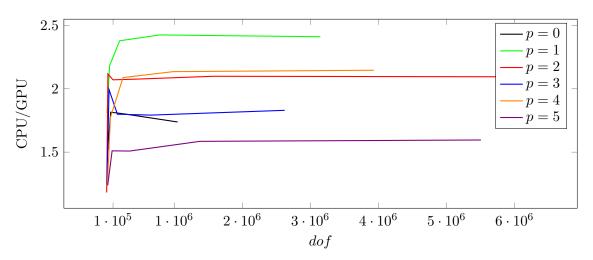

| 4.3 | The relative performance of the integration on $\Omega_I$ of the CPU and GPU-                                                                    |    |

|     | implementations $\mathcal{P}_{CPU}/\mathcal{P}_{GPU}$                                                                                            | 50 |

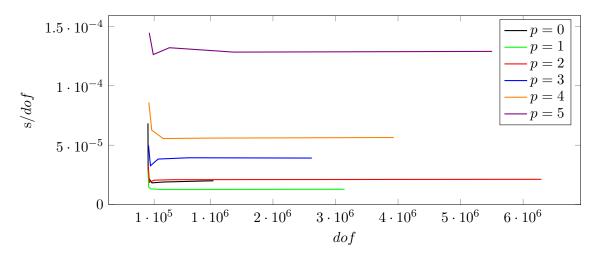

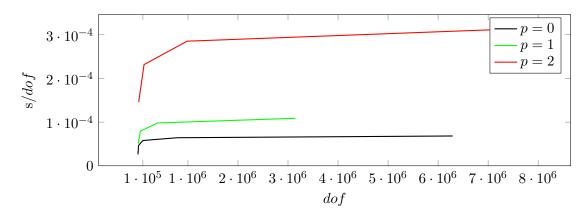

| 4.4 | The performance of the integration on $\Omega_I$ of the CPU-implementation $\mathcal{P}_{CPU}$ in                                                |    |

|     | the 3D case                                                                                                                                      | 59 |

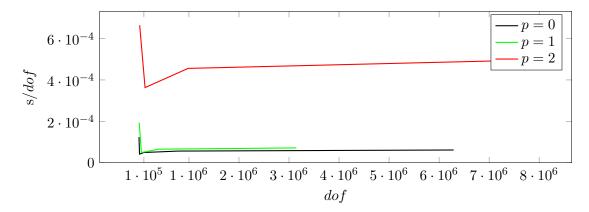

| 4.5 | The performance of the integration on $\Omega_I$ of the GPU-implementation $\mathcal{P}_{GPU}$ in                                                | F0 |

| 16  | The relative performance of the integration on O. of the CDU and CDU.                                                                            | 59 |

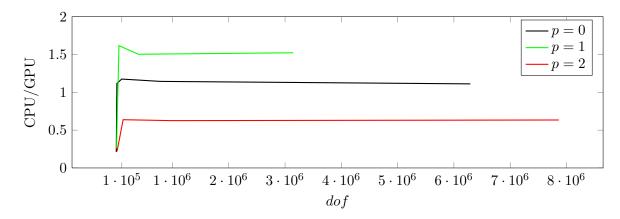

| 4.6 | The relative performance of the integration on $\Omega_I$ of the CPU and GPU-implementation $\mathcal{P}_{CPU}/\mathcal{P}_{GPU}$ in the 3D case | 60 |

| 4.7 | A possible indexing scheme for 2 adjacent neighborhoods $\dots$                                                                                  | 63 |

| 4.7 | Alternative memory layout for the parameters                                                                                                     | 63 |

| 4.0 | The charge memory layout for the parameters                                                                                                      | UJ |

| A.1 | The indexing scheme used for the results                                                                                                         | 70 |

# List of Tables

| 2.1                      | The number of cells generated by both decomposer approaches, for all inner patches of a cover of a square domain (2D) using uniform refinement The number of cells generated by both decomposer approaches, for all inner                 | 29                   |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

|                          | patches of a cover of a square domain (2D) using h-refinement at the center of the domain                                                                                                                                                 | 30                   |

| 3.1                      | The memory requirement of the base functions $\psi_i^n$ for all patches with support on a cell                                                                                                                                            | 46                   |

| 4.1<br>4.2<br>4.3<br>4.4 | Reference system configuration                                                                                                                                                                                                            | 47<br>48<br>51       |

| 4.5<br>4.6<br>4.7        | polynomial degrees                                                                                                                                                                                                                        | 52<br>53<br>53<br>54 |

| 4.7<br>4.8<br>4.9        | The ratio of the duration of the postprocessing and the whole GPU-implementation. The ratio of the duration of the kernel for SP and double precision floating point (DP)                                                                 | 55                   |

| 4.10                     | and integration of $\Omega_I$                                                                                                                                                                                                             | 56<br>57             |

|                          | degrees                                                                                                                                                                                                                                   | 57<br>58             |

|                          | The ratio of non divergent branches and all branches in the kernel for the decomposition and integration of $\Omega_I$                                                                                                                    | 58                   |

|                          | Geforce GTX 560 Ti                                                                                                                                                                                                                        | 61                   |

| B.1<br>B.2<br>B.3        | The duration required by the CPU-implementation for the integration on $\Omega$ . The duration required by the GPU-implementation for the integration on $\Omega$ . The relative duration required by the GPU-implementation and the CPU- | 71<br>71             |

| B.4                      | implementation for the integration on $\Omega$                                                                                                                                                                                            | 72<br>72             |

| B.5  | The duration required by the GPU implementation for decomposition and                             |    |

|------|---------------------------------------------------------------------------------------------------|----|

|      | integration on $\Omega_I$                                                                         | 72 |

| B.6  | The relative duration required by the GPU-implementation and the CPU-                             |    |

|      | implementation for decomposition and integration on $\Omega_I$                                    | 73 |

| B.7  | The duration required by the preprocessing of the GPU-implementation for the                      |    |

|      | decomposition and integration on $\Omega_I$                                                       | 73 |

| B.8  | The duration required by the kernel of the GPU-implementation for the decom-                      |    |

|      | position and integration on $\Omega_I$                                                            | 73 |

| B.9  | The duration required by the postprocessing of the GPU-implementation for                         |    |

|      | the decomposition and integration on $\Omega_I$                                                   | 74 |

| B.10 | The duration required by the GPU-implementation when using SP for the                             |    |

|      | integration on $\Omega_I$                                                                         | 74 |

| B.11 | The duration required by the GPU-implementation for the preprocessing when                        |    |

|      | using single precision floating point (SP) for the integration on $\Omega_I$                      | 74 |

| B.12 | The duration required by the GPU-implementation for the kernel when using                         |    |

|      | SP for the integration on $\Omega_I$                                                              | 75 |

| B.13 | The duration required by the GPU-implementation for the postprocessing when                       |    |

|      | using SP for the integration on $\Omega_I$                                                        | 75 |

| B.14 | The number of instructions issued during the kernel execution for the integration                 |    |

|      | on $\Omega_I$                                                                                     | 75 |

| B.15 | The number of L1 load misses for local memory requests in the kernel for the                      |    |

|      | integration on $\Omega_I$                                                                         | 76 |

| B.16 | The number of L1 store misses for local memory requests in the kernel for the                     |    |

|      | integration on $\Omega_I$                                                                         | 76 |

| B.17 | The number of branches in the kernel for the integration on $\Omega_I$                            | 76 |

|      | The number of divergent branches in the kernel for the integration on $\Omega_I$                  | 77 |

| B.19 | The duration required by the CPU-implementation for the integration on $\Omega_I$ in              |    |

|      | 3D                                                                                                | 77 |

| B.20 | The duration required by the GPU-implementation for the integration on $\Omega_I$ in              |    |

|      | 3D                                                                                                | 77 |

| B.21 | The ratio of the duration required by the GPU-implementation and the CPU-                         |    |

|      | implementation for decomposition and integration on $\Omega_I$ in 3D                              | 77 |

| B.22 | The relative performance of the implementation on the NVIDIA <sup>TM</sup> K20 and the            |    |

|      | Geforce GTX 560 Ti using SP                                                                       | 78 |

| B.23 | The relative performance of the implementation on the NVIDIA <sup>TM</sup> K20 using              |    |

|      | SP and DP                                                                                         | 78 |

| B.24 | The duration required by the kernel for the integration on $\Omega_I$ on the NVIDIA <sup>TM</sup> |    |

|      | K20                                                                                               | 78 |

| B.25 | The duration required by the kernel for the integration on $\Omega_I$ on the NVIDIA <sup>TM</sup> |    |

|      | K20 using SP                                                                                      | 79 |

|      |                                                                                                   |    |

# List of Algorithms

| Decomposition using the Tree-Based Approach in pseudo code                            |    |

|---------------------------------------------------------------------------------------|----|

| Scheduling of neighborhoods for computation on the GPU in pseudo code Kernel workflow | 42 |

## List of Abbreviations

arithmetic and logic unit. 55, 56, 81 ALU API application programming interface. 35, 36, 48 BVP boundary value problem. 7, 15, 17, 40, 41 CPU central processing unit. 7-9, 14, 16, 25, 28, 35-37, 39, 42, 43, 47, 49, 50, 52, 54, 58–60, 62, 64, 67, 68, 71–73, 77 **CUDA** Compute Unified Device Architecture. 3, 7, 15, 16, 35–39, 41, 45, 46, 48, 52, 54, 55, 58, 61, 67, 68, 81 DP double precision floating point. 8, 9, 47–49, 51, 54–56, 61, 71, 78 DRAM dynamic random-access memory. 35, 39 FMA fused-multiply-add instruction. 48 gflops giga floating point operations per second. 47, 48 **GPGPU** general-purpose computing on graphics processing units. 15, 20, 23, 35, 40 GPU graphics processing unit. 7-10, 14-16, 20, 21, 25, 28, 30, 35, 36, 39–44, 47, 49–54, 57, 59, 60, 62–64, 67–69, 72–75, 77, 81 MPIMessage Passing Interface. 41, 47 PDEpartial differential equation. 12, 13, 15, 17, 19, 40, 41, 67, 68 **PMPUM** Parallel Multilevel Partition of Unity Method. 3, 12, 13, 15-17, 20, 30, 40, 41, 45, 48, 67, 68 SIMT Single Instruction Multiple Threads. 37, 81 SMStreaming Multiprocessors. 8, 35, 37–39, 49, 55, 56, 60, SPsingle precision floating point. 8, 9, 47, 48, 54–56, 61, 74, 75, 78, 79

## List of Symbols

```

A

stiffness matrix in the Galerkin approach. 12, 19, 20, 41,

block entry of the stiffness matrix A. 20, 43

A_{(i,n),(j,m)}

boundary conditions of a given PDE. 17

C_i

neighbor patches of patch \omega_i. 7, 19, 20, 22, 23, 25, 29,

31, 32, 34, 43–45, 69

H^1(\Omega)

Sobolev space on \Omega. 19, 20

L

second order symmetric elliptic partial differential oper-

ator. 17, 20

M_c

the patches with support on an integration cell. 14, 32,

N

number of points card(P) in the initial point set P. 18,

21, 30, 32, 34, 48

0

upper bound for the complexity of an algorithm in the

Big O notation. 30, 32–34

P

initial set of points in the PMPUM. 12–14, 18, 19

V^{PU}

function space used in the PMPUM. 18, 20

V_i^{p_i}

function space defined on patch \omega_i. 13, 14, 18, 21, 32–34,

41, 44, 45, 69, 81

W_i

weight function defined on patch \omega_i. 7, 18–20, 22, 23, 32

Δ

Laplace operator. 19, 20

\Gamma_D

part of the domain's boundary \partial\Omega where Dirichlet bound-

ary conditions are given \Gamma_D = \partial \Omega \setminus \Gamma_N. 12, 13, 17

\Gamma_N

part of the domain's boundary \partial\Omega where Neumann

boundary conditions are given \Gamma_N = \partial \Omega \setminus \Gamma_D. 12, 13,

\Omega

domain on which the given PDE is defined. 7-9, 12-14,

17-22, 30, 44, 49, 50, 52, 56, 58-61, 71-79

The stretch factor used for \omega_i in the cover generation of

\alpha_i

the PMPUM. 20–22, 31

Ĵ

discrete right hand side of a given PDE. 13, 19, 20, 41,

coefficient vector of the discrete solution of a given PDE.

\hat{u}

19

```

```

diffusion coefficient in the reaction diffusion equation.

\kappa

17, 19, 20, 22

patch affiliated with point x_i \in P. 7, 12, 13, 18–20, 22,

\omega_i

23, 25, 29–32, 34, 42–44, 63, 65, 69, 81

\overrightarrow{n}

normal vector on the \partial\Omega. 17, 19, 20

\partial\Omega

boundary of the domain \Omega. 12, 13, 17, 19–21

n-th base function of V_i^{p_i} defined on patch \omega_i. 8, 13, 18,

\psi_i^n

20, 22, 32, 33, 41, 43, 45, 46

partition of unity function defined on patch \omega_i. 7, 18–20,

\varphi_i

22, 41, 43

a(\cdot, \cdot)

bilinear form. 14, 20, 33, 41–43, 45, 52

number of base functions card(\psi_i^n) in V_i^{p_i}. 33, 42, 44,

b_i

45, 48, 69

card()

the cardinality of a set. 12, 13, 32, 34

d

space dimension. 18, 21, 30, 32–34, 42, 48, 51, 52, 57

dof

number of degrees of freedom. 48–50, 59, 60

f

continuous right hand side of a given PDE. 17, 19, 22

block entry of the discrete right hand side \hat{f}. 20

f_{(i,n)}

boundary values of a given PDE. 17, 20

g

Dirichlet boundary values of a given PDE on \Gamma_D. 17

g_D

Neumann boundary values of a given PDE on \Gamma_N. 17

g_N

h_i

stretch of patch \omega_i. 18, 21, 30, 42, 81

level used in PMPUM. 21, 29, 30, 33, 34, 48–52, 57, 60

l

l(\cdot)

linear form. 14, 20, 33, 41, 45, 52

number of cells on a patch \omega_i. 32, 34

n_{CI}

number of nodes used by a quadrature rule. 32–34, 51,

n_{NI}

52, 57

number of patches on an integration cell. 32–34, 45

n_{\omega C}

polynomial degree. 21, 30, 32–34, 42, 45, 46, 48, 51–54,

p

57, 60–62, 67

reaction coefficient in the reaction diffusion equation. 17,

19, 20, 22

continuous solution of a given PDE. 17–19

u

continuous test function used in the variational formula-

v

tion. 19

i-th point in P. 13, 18, 42

x_i

\mathcal{C}_{EI}

costs for the evaluation of the integrand at an integration

node. 32, 34

costs for numerical integration in the PMPUM. 32, 34

\mathcal{C}_{NI}

```

costs for the evaluation of the base functions of the  $\mathcal{C}_{\mathrm{B}M_c}$ function space  $V_i^{p_i}$  on each of the patches the patches with support on an integration cell  $(M_c)$  on an integration cell. 32, 33  $\mathcal{C}_{\mathrm{W}M_c}$ costs for the evaluation of the weight functions of the patches  $M_c$  on an integration cell. 32  $\mathcal{C}_{bf}$ costs for the evaluation of the bi-linear form  $a(\cdot,\cdot)$ . 32, 33  $\mathcal{C}_{lf}$ costs for the evaluation of the linear form  $l(\cdot)$ . 32, 33  $\mathcal{P}_{CPU}$ performance of a CPU-implementation. 7, 49, 50, 59, 60  $\mathcal{P}_{GPU}$ performance of a GPU-implementation. 7, 49, 50, 59, 60  $\mathcal{W}$ the set of patches generated from P. 18, 41, 43the patches evaluated in the i-the GPU schedule. 7, 41,  $\mathcal{W}_i$ 43,62-64ttime. 48  $\Omega_I$ domain of the inner patches. 7-9, 21, 22, 44, 49, 50, 52, 56, 58-61, 72-79

## 1 Introduction

In today's society, simulation technology has not only become an integral part of society – it has become almost indispensable [2]. Simulation can be used in situations where physical, ethical or financial reasons impede experiments. Thus, simulation technology can be utilized to gain knowledge about actions or natural phenomenons that we are unable or unwilling to observe. These situations range from weather forecast, where a prediction of future events can not be reached through observation, to the design and development of automobiles, where crash tests are economized to shrink costs.

Simulation is based on domain specific models, consisting of representations of the subjects of study and the physical or other relations between them. Different methods are then applied to reproduce the results of actions or phenomenons. These methods, however, require a large amount of computations to calculate a detailed solution. Therefore, in almost every case, computers are utilized to implement these methods.

In many cases, the models for simulation employ partial differential equations (PDEs) to describe the real world [8, p. 1]. A PDE models the alteration of a given quantity in time and/or space. Examples for that are the stress of materials during crash tests or the diffusion of one chemical substance into another. When additional information on the initial situation and/or the behavior of the phenomenon at the boundary of the domain inspected is given, a so called initial or boundary value problem (BVP) results from the PDE.

For most BVPs arising from practical situations, no definite solution can be calculated with today's methods [8, p. 1]. Therefore, manifold methods exist to compute approximate solutions. Methods for the simulation of physical phenomenons can be classified into mesh-based methods and particle schemes. Both categories exhibit different strengths and weaknesses. Mesh-free methods try to merge the best of both categories. The Parallel Multilevel Partition of Unity Method (PMPUM) [8, p. 13] is a mesh-free method that is especially suitable in situations where some properties of solutions are known a priori.

The implementation of the Parallel Multilevel Partition of Unity Method (PMPUM) can be parallelized to decrease the duration for the generation of a solution. Multiple technologies can be used for that. Graphics processing units (GPUs), initially used for the display of 2D and 3D data in computer graphics, provide great parallel processing power [19]. This capability can be utilized for more general problems by technologies called general-purpose computing on graphics processing units (GPGPU). Compute Unified Device Architecture (CUDA) [19] is a technology of NVIDIA<sup>TM</sup>, that enables the usage of NVIDIA<sup>TM</sup>'s GPUs for GPGPU. However, not for all methods an increase of the performance can be reached when using CUDA.

In this thesis we present an implementation of the steps in PMPUM that account for most of the computational effort. The goal of this thesis is to analyze the potential of CUDA to increase the performance of a given CPU-based<sup>1</sup> implementation of the PMPUM.

This thesis is organized as follows:

Chapter 2 - The Parallel Multilevel Partition of Unity Method: Provides an introduction to the PMPUM. Afterwards, it focuses on the algorithm used in the GPU-implementation. Finally, we give estimates for the costs of these same.

Chapter 3 – Implementation: Introduces CUDA and based on that, gives an outline of the implementation. The explanation of properties and limitations of the implementation closes the chapter.

Chapter 4 – Results: Presents experiments performed to analyze the implementation. Therefore it provides information on the hardware and metrics used. Based on the results of the experiments, we provide recommendations for further improvements.

Chapter 5 – Conclusion: Summarizes the results of this thesis and provides an outlook to further development.

<sup>&</sup>lt;sup>1</sup>central processing unit (CPU)

## 2 The Parallel Multilevel Partition of Unity Method

Partial differential equations (PDEs) can be used to model problems in a wide range of fields. Since for many PDEs no exact solutions can be found, there exist manifold methods to generate approximate solutions. See [3] or [1] for an introduction to PDEs and approximation methods. The PMPUM is one method to approximate solutions. In this chapter we give an overview about the method, for a detailed introduction see [8]. In the following we present how a PDE is discretized in the PMPUM. The remarks on the discretization are influenced by the introduction to the PMPUM in [20, p. 3 ff.]. Then we focus on the computational task for which an implementation will be presented in the following chapter.

#### 2.1 Model Problem

BVPs, for which the PMPUM can be used for the approximation of the solution, are in general of the form:

$$Lu = f \text{ in } \Omega \subset \mathbb{R}^d$$

$$Bu = g \text{ in } \partial \Omega$$

Here L is a second order symmetric elliptic partial differential operator and B are suitable boundary conditions. The task is to find the solution u that solves the equation. We choose the reaction-diffusion equation to illustrate the discretization of a PDE in the PMPUM:

$$-\nabla \cdot (\kappa \nabla u) + r \cdot u = f \text{ in } \Omega \subset \mathbb{R}^d$$

$$u = g_D \text{ in } \Gamma_D \subset \partial \Omega$$

$$\kappa \nabla u \cdot \overrightarrow{n} = g_N \text{ in } \Gamma_N = \partial \Omega \backslash \Gamma_D$$

(2.1)

Here  $\kappa$  is the diffusion coefficient, while r is the reaction coefficient. The boundary  $\partial\Omega$  is split into  $\Gamma_D$  on which Dirichlet boundary conditions are given and  $\Gamma_N$  on which Neumann boundary conditions are given. An approximate solution should have the following two properties [8, p. 13]:

- local approximability

- inter-element continuity

Local approximability is the capability to approximate the solution u at a given point as close as possible. Inter-element continuity means that an approximate solution should be continuous in some sense.

#### 2.2 Partition of Unity Space

We introduce the partition of unity space  $V^{PU}$  that is used to find an approximate solution. We start with an arbitrarily chosen point set P with points from the domain  $\Omega$ :

$$P = \{x_i \in \mathbb{R}^d | x_i \in \Omega, i \in \{1, ..., N\}\}\$$

For each point  $x_i$  we define a patch  $\omega_i$  by a d-rectangular:

$$\omega_{i} = \bigotimes_{l=1}^{d} \{x_{i}^{l} - h_{i}^{l}, x_{i}^{l} + h_{i}^{l}\}\$$

Here  $x_i$  is the center of the patch and  $h_i$  is the stretch in each space dimension. On each patch we define a local approximation space  $V_i^{p_i} = span\langle\psi_i^n\rangle$ . This local approximation space  $V_i^{p_i}$  is used for the local approximability. We define  $\mathcal{W}$  as the set of patches generated from the initial set of points P. The global function space  $V^{PU}$ , required by the Galerkin approach, is generated by the product of the local approximation space  $V_i^{p_i}$  with suitable partition of unity functions  $\varphi_i$ :

$$V^{PU} = \sum_{i} \varphi_{i} V_{i}^{p_{i}} = \sum_{i} \varphi_{i} \langle \{\psi_{i}^{n}\} \rangle = span \langle \{\varphi_{i} \psi_{i}^{n}\} \rangle$$

The local approximation space  $V_i^{p_i}$  can be chosen independently from all other local approximation spaces  $V_j^{p_j}$ . For smooth functions polynomials exhibit good approximation properties, for more irregular functions enrichment functions can be added to the base  $\psi_i^n$  of the local approximation space  $V_i^{p_i}$ . Using a partition of unity ensures that arbitrary functions can be added to the local approximation space without violating the inter-element continuity property. The required partition of unity functions  $\varphi_i$  are defined patch-wise. On each patch  $\omega_i$  a weight function  $W_i$  is defined, where:

$$W_i(x) \neq 0 \text{ for } x \in \omega_i$$

$W_i(x) = 0 \text{ else}$

Based on these weight functions  $W_i$  we construct the partition of unity function  $\varphi_i$ :

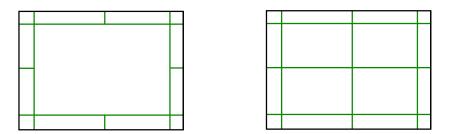

Figure 2.1: The weight function  $W_i$  of adjacent patches  $\omega_i$  (left) and the resulting partition of unity  $\varphi_i$  (right) in one space dimension

$$\varphi_i(x) = \frac{W_i(x)}{\sum_{k \in C_i} W_k(x)}$$

Here the neighborhood  $C_i$  consists of all patches  $\omega_j$  whose weight function  $W_j$  have overlapping support with the weight function  $W_i$  of  $\omega_i$ .

Figure 2.1 illustrates the weight function  $W_i$  and the resulting partition functions  $\varphi_i$  of some adjacent patches. The cover generation, presented in [8, p. 98 ff.] creates a cover of the domain from the initial point set P, so that the union  $\bigcup \omega_i$  of the patches covers the domain  $\Omega$ . The choice of the weight functions  $W_i$  and thus the overlap of the patches determines the sparsity pattern of the stiffness matrix A generated by the Galerkin approach presented in the following.

#### 2.3 Galerkin Discretization

The Galerkin approach can be used to discretize a PDE like the one given in equation 2.1. It utilizes the weak formulation of the problem to redefine the problem in a function space in which a solution can be found. See [3, p. 133 ff.] for an introduction to the weak formulation that is also called the variational formulation. In this section we only give a very short introduction into the concepts required in following. First, we define an approximate solution of a PDE:

$$A\hat{u} = \hat{f}$$

Here A is the stiffness matrix that needs to be generated,  $\hat{f}$  is the discretized right-hand side and  $\hat{u}$  is the vector of coefficients of the solution. Using a constant diffusion coefficient  $\kappa$  and reaction coefficient r in equation 2.1 results in:

$$-\kappa\Delta u + ru = f$$

Here  $\Delta$  is the Laplace operator. We generate the variational formulation by multiplying the equation with a test function v from the trial and test space  $H^1(\Omega)$  and integrating it. Afterwards we apply Green's first identity and obtain:

$$\int_{\Omega} -v(\Delta\kappa \cdot u + r \cdot u) = \int_{\Omega} \kappa \nabla u \nabla v + ruv + \int_{\partial\Omega} \kappa v(\nabla u \cdot \overrightarrow{n}) = \int_{\Omega} f \cdot v$$

Here  $\overrightarrow{n}$  is the outer normal on  $\Omega$ . Let  $a(\cdot, \cdot)$  be a continuous elliptic bilinear form induced by  $L = -\kappa \Delta + r$  on the Sobolev space  $H^1(\Omega)$  and  $l(\cdot)$  be a continuous linear form. Applying the Galerkin approach using the base and test functions from  $V^{PU}$  results in:

$$A = (A_{(i,n),(j,m)}), \text{ with } A_{(i,n),(j,m)} = a(\varphi_i \psi_i^n, \varphi_j \psi_j^m)$$

$$\hat{f} = (f_{(i,n)}), \text{ with } f_{(i,n)} = l(\varphi_i \psi_i^n)$$

Since the partition of unity-functions  $\varphi_i$  only have local support, the integrals on  $\Omega$  only must be evaluated for all  $\omega_i \cap \omega_j \cap \Omega$  and  $\omega_i \cap \omega_j \cap \partial \Omega$  respectively. We only tackle  $\Omega$  using the GPU and thus can assume g = 0 without restriction. When applying the Galerkin approach to the model problem given in equation 2.1 the resulting computational task is given by:

$$\int_{\Omega} \kappa \nabla(\varphi_i \psi_i^n) \nabla(\varphi_j \psi_j^m) + r(\varphi_i \psi_i^n) (\varphi_j \psi_j^m)$$

$$\int_{\Omega} (\varphi_i \psi_i^n)$$

(2.2)

We need to compute the integrals on all  $\omega_i \cap \omega_j \cap \Omega$ . Therefore, first the domain must be decomposed into integration domains on which the set of patches, whose weight function  $W_i$  have support, is determined. After that, the integrals must be computed for all integration domains. In the following we focus on these 2 steps since they account for a major part of the computational effort of the whole PMPUM [8, p. 153].

#### 2.4 Decomposition of the Domain

In this section we present the decomposition task described in section 2.3 from an implementation point of view. After that different approaches to solve this task are presented and discussed in terms of suitability for GPGPU.

#### 2.4.1 Decomposition Task

The Galerkin discretization requires the computation of the integrals given in formula 2.2. We assume that a cover of patches for the domain has already been generated. The algorithm used for the cover construction can be found in [8, p. 98 ff.]. The cover generation provides covers on different levels. The generated cover does not only cover the whole domain  $\Omega \subset \bigcup \omega_i$ , but assures the overlap of a patch  $\omega_i$  with all its neighbors  $C_i$ . This is reached by stretching the extent of each patch with a factor  $\alpha_i > 1$ . This is required to reach the inter-element continuity property given in section 2.1.

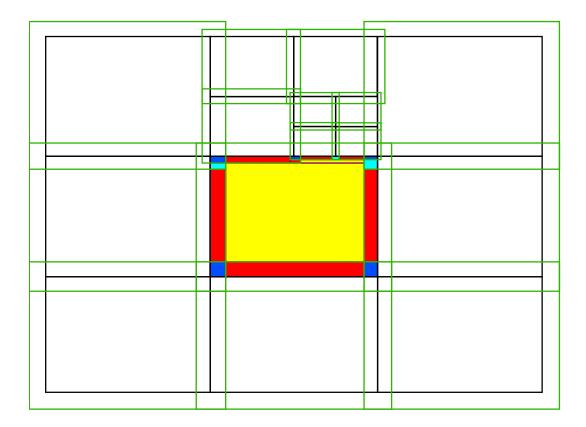

Figure 2.2: The inner (green) and boundary (yellow) patches generated by an uniform refinement strategy from level 0 to 3. The overlap of the patches (caused by  $\alpha_i$ ) was chosen to be equal on all levels for illustration. Usually it is chosen proportionately to the stretch  $h_i$  of a patch.

Figure 2.2 shows the cover generated for a domain on the levels 0-3 for an uniform-h-refinement strategy.<sup>1</sup> For uniform refinement the number of patches is  $(2^d)^l$  for d space dimensions on Level l. Patches with an overlap with the boundary of the domain  $\partial\Omega$  are called "boundary patches". The patches with no overlap are called "inner patches" and the domain they cover is denoted  $\Omega_I$  in the following. Since the boundary patches intersect the domain boundary an approximation of the domain needs to be calculated. This results in irregular patterns and hence is not suitable for computation on GPUs. Thus we focus in the following on the tasks given for the computation of the integral on the inner patches:

<sup>&</sup>lt;sup>1</sup>H-refinement is a refinement strategy which increases the number of points N on each level, in contrast to that p-refinement is the increase of the polynomial degree p, used in all  $V_i^{p_i}$  on each level.

<sup>&</sup>lt;sup>2</sup>Uniform in this context means that all patches on a given level are subdivided in every space dimension to form the next level. In contrast to that, adaptive refinement strategies only subdivide a part of the given patches.

Figure 2.3: The decomposition of a patch  $\omega_i$  and its neighborhood  $C_i$  for integration. The basic extent of the patch (bold) and its neighbors is given by the black rectangles. The green rectangles are the patches stretched by  $\alpha_i$ . The needed decomposition is given by all small rectangles in the black bold rectangle. The fill color of the rectangle shows the number of patches on the cells. Yellow stand for 1, red for 2 and blue for 4 patches with support on the cell.

$$\int_{\Omega_I} \kappa \nabla(\varphi_i \psi_i^n) \nabla(\varphi_j \psi_j^m) + r(\varphi_i \psi_i^n) (\varphi_j \psi_j^m)$$

$$\int_{\Omega_I} f(\varphi_i \psi_i^n)$$

(2.3)

Calculating these integrals requires the decomposition of the overlapping patches. This task is illustrated in figure 2.3 for a patch and its neighbors in 2 space dimensions for a cover generation which uses uniform refinement.

When using linear splines as weight functions additional cells are generated. The integration domain must be split at the patch center where the derivative of the weight function is discontinuous when more than one patch has support on a cell. In figure 2.5, which will be discussed in detail when comparing different approaches for the decomposition, these additional splits can be seen. Thus, the resulting decomposition generates at least 13 cells in 2 space dimensions and 57 cells in 3 space dimensions.

Different decomposers approaches can be benchmarked using the following metrics:

- 1. The number of cells should be minimal. Additional cells do not falsify the results, but lead to unnecessary computations.

- 2. The number of patches on the cells should be minimal. Additional patches on a cell don't influence the result since their weight function  $W_i = 0$  on the cell, but they introduce unnecessary computations.

3. The complexity in time and space should be minimal. For GPGPU the resource data structures as well should be taken into account.

#### 2.4.2 Decomposers

The requirements given in the previous section need to be met by all considered approaches for the decomposition. In the following two approaches are presented and their suitability for an implementation using GPGPU is discussed.

#### Tree-Based Approach

The first approach uses a tree to generate the required cells for integration. The basic ideas to generate a tree with the following properties:

- 1. Each node stores an geometric extent and a list of patches and references to two children.

- 2. A leaf represents a resulting cell.

- 3. The patches with support on a cell, represented by the leaf, are those in the lists of patches of all nodes on the path from the root to the leaf.

- 4. The extent stored for non-leaf nodes is the union of the extents of their children.

The algorithm 2.1 starts by adding the patch  $\omega_i$  itself to the tree. This is achieved by storing its nonstretched extent and a reference to it as the root node of the tree. After that all adjacent patches  $C_i$  are added subsequently. We start by comparing the stretched extent to that of the root node. If it is equal, we add the patch to the patch list of the node. If not, the comparison is done for all children whose extents have an intersection with the stretched extent of the patch. This is done until a leaf is reached. When the extent of the leaf is not equal to the stretched extent of the patch two children are added to the leaf, one with an intersection of the stretched extent of the patch and the node and one without. The patch is added to the new node with an intersection with the stretched extent of the patch. Figure 2.4 shows this process for the first two patches of a neighborhood. To get the cells we traverse the tree and store the patches on the path from the root to each leaf. This results in a list of cells containing the patches with support on each cell. The algorithm is adapted to the usage of linear splines as weight functions  $W_i$ . Therefore, the cells, on which more than one patch has support and the extent has an intersection with the patch center, are split at the patch center. The resulting patches are illustrated in figure 2.5. Because of the usage of the tree we call this approach Tree-based Decomposition from here on.

The key benefits of this approach are:

- It produces the minimal number of cells.

- It allows fast and random access of all cells.

The disadvantages of this approach are:

#### Algorithm 2.1 Decomposition using the Tree-Based Approach in pseudo code

```

// each node contains a box, a list of patches and a list of children

procedure DECOMPOSE(patch)

Tree.box = patch.box

TREE.PATCHLIST.APPEND(patch)

for all neighbor \in neighborhood of patch do

ADDNEIGHBOR (Tree, neighbor)

end for

return GETCELLS()

end procedure

procedure ADDNEIGHBOR(node, patch)

if ISEQUAL(patch.box, node.box) then

NODE.PATCHLIST.APPEND(patch)

else if ISLEAF(node) then

overlap = INTERSECTION(patch.box, node.box)

nonOverlap = patch.box - overlap

NODE.CHILDREN.APPEND(overlap, patch)

NODE.CHILDREN.APPEND(nonOverlap)

else

for all child \in node.children do

if INTERSECTION(patch.box, child.box) then // only descend to children having

// an overlap with the patch

ADDNEIGHBOR(child, patch)

end if

end for

end if

end procedure

procedure GETCELLS( )

// the resulting list of cells

cells

// For all leafs follow the path to the leaf and

for all leaf ∈ Tree.getleafs( )do

// collect the patches with support on the cell

cellPatches = LEAF.GETPATCHESONPATH()

cell = (leaf.box, cellPatches)

// the cells with more than one patch and intersecting the patch's center

// must be split due to the usage of linear splines as weight functions

if intersects(cell.box, patchCenter) && cellPatches.length() > 1 then

splittedCells = CELL.SPLIT(patchCenter)

CELLS.APPEND(splittedCells)

else

CELLS.APPEND(cell)

end if

end for

return cells

end procedure

```

- Under the assumption that the order of the patches in the input is unknown, the generated tree is of a priori unknown structure.

- A tree implementation requires dynamic or complex manual memory handling.

On central processing units (CPUs) these restrictions are no drawback since the loss of performance due to lot of small memory allocations is insignificant. The number of cells however and the number of patches per cell is optimal leading to a minimum number of evaluation in the following integration. Since the situation is quite different for a GPU, dynamic memory allocation is expensive and more evaluations are cheap one should consider other approaches.

#### Tensor-Product Approach

An other approach utilizes the concept of tensor products. The basic idea of this approach is to store the boundary of each intersection of patches in a list per dimension. Afterwards these points per dimension can be used to generate a grid of cells. The information stored at one point can be altered. That leads to different complexity of the algorithm and quality of the results, according to the metrics presented in section 2.4.1.

Algorithm 2.2 shows the approach, called Tensor-Product Approach in the following. In the shown variation the algorithm stores a list of points per space dimension, we will call these points "split points" in the following. Each split point consists of the coordinate and a list of splits. A split stores a reference to a patch and whether the point is the minimum, center or maximum of that patch in the given dimension. For the patch  $\omega_i$  itself we store the minimum, center and maximum to the split points in each dimension. When adding a patch of the neighborhood  $C_i$  we add the minimum, center and maximum to the split points in each dimension. If the point is outside the domain of the patch, whose neighborhood is currently decomposed, the information on minimum and maximum are stored at the boundary of that patch. The generated split points for two example patches are shown in figure 2.4 on the right.

These split points then can be used to retrieve the cells. Therefore, we start at the lowest split point for each dimension. We add the patches with a minimum at this point to a list of active patches which is stored per dimension. The generated cell has the extent from the current to the next split point in all dimensions. The patches with support on the cell are those which are currently active in all dimensions. Iterating over all split points in all dimensions generates all cells. At a split point the patches with minimum are added to the list of active patches in the current dimension. For a maximum the patch is removed, the center has no influence on the active patches and can thus be omitted for the calculation of active patches. We therefore only store the patches whose support begins or ends at a split point. Before we discuss variations of this approach the key benefits and disadvantages are listed.

The key benefit of this approach is:

```

Algorithm 2.2 Decomposition using the Tensor-Product Approach in pseudo code

SplitPoints[dim]

// a list of split-points for each dimension, each split-point stores the

// coordinate and the patches which start or end at the point

localDomain

// the box of the center patch

selectedPatches[dim]

// list of Booleans for each dimension used in getNextCell

index[dim] // multi dimensional index with number of split-points entries in each component

procedure DECOMPOSE(patch)

localDomain = patch.box

for all d \in \dim do

// Add the split points of the center patch

index[d] = 0

ADDSPLITPOINT(d, patch.box.min[d], patch, min)

ADDSPLITPOINT(d,patch.box.center[d], patch, mid)

ADDSPLITPOINT(d,patch.box.max[d], patch, max)

end for

for all neighbor \in neighborhood of patch do// Add the split points of all other patches

for all d \in \dim do

// if a patch boundary is intersecting the local domain add it to the split points,

// else add the patch to the list of splits of the min/max of the localdomain

if neighbor.box.min[d] > localDomain.min[d] then

ADDSPLITPOINT(d, neighbor.box.min[d], patch, min)

else

SPLITPOINTS[D][0].SPLITS.APPEND(patch, min)

end if

if neighbor.box.center[d] > localDomain.min[d] & neighbor.box.center[d] < local-

Domain.max[d] then

ADDSPLITPOINT(d, neighbor.box.center[d], patch, mid)

end if

if neighbor.box.max[d] < localDomain.max[d] then

ADDSPLITPOINT(d, neighbor.box.max[d], patch, max)

else

SPLITPOINTS[D][SPLITPOINTS[D].LENGTH].SPLITS.APPEND(patch, max)

end if

end for

end for

end procedure

procedure ADDSPLITPOINT(dim,coord, patch, type)

for all SplitPoint ∈ SplitPoints[dim] do

if SplitPoint.coord == coord then

SPLITPOINT.SPLITS.APPEND(patch,type)

else if SplitPoint.coord > coord then

newSplitPoint(coord, (patch,type))

SPLITPOINTS[DIM].INSERT(newSplitPoint, currentPosition)

end if

end for

newSplitPoint(coord, (patch,type))

```

end procedure

SPLITPOINTS[DIM].APPEND(newSplitPoint)

Continuation of Algorithm 2.2: Decomposition using the Tensor-Product Approach in pseudo code

```

procedure GETNUMBEROFCELLS

result = 1

for all d in dim do

result *= SplitPoints[d].length

end for

return result

end procedure

procedure GETNEXTCELL

result

// the resulting integration cell

for all d in dim do

// initialize the selected flag (non-selected) for all patches

if index[d] == 0 then

for all neighbor in neighborhood do

selectedPatches[d][neighbor] = False

end for

end if

end for

for all d in dim do

// set integration cell box

result.box.lower[dim] = splitPoints[d][index[d]].coord

result.box.upper[dim] = splitPoints[d][index[d]+1].coord

// update the selected patches

for all split in SplitPoints[d][index[d]].splits do

if split.type == min then

selectedPatches[d][split.patch] == True

else if split.type == max then

selectedPatches[d][split.patch] == False

end if

end for

end for

for all patch in patches do

// add all patches selected in all dimensions

selected = True

for all d in dim do

if not selectedPatches[d][patch] then

selected = False

end if

end for

if selected then

RESULT.PATCHES.APPEND(patch)

end if

end for

index++

return result

end procedure

```

the number of split points and maximum number of splits at a split point are known for a cover which uses uniform refinement strategy. Therefore, no dynamic allocation is needed.

The disadvantage of this approach are:

- The cells cannot be requested in arbitrary sequence.

- Only the split points for each dimension are stored and the generation of the cells is basically a tensor-product of the split points. Thus more cells are generated if a split point divides the patch completely but the neighbor, which introduced the split point, only intersects a part of the patch extent. For an example of the additional generated cells see figure 2.5.

The following modifications might be considered:

- 1. The information which patch has support on which cell can be omitted without difficulty. Hence all patches need to be evaluated on all generated cells. This leads to a remarkable simplification of the algorithm but on the other hand to a considerable amount of unnecessary evaluations.<sup>3</sup>

- 2. Storing not only the difference between 2 cells but the whole list of active patches at a split point enables random access of cells. On the other hand, the list of patches at a split point needs to contain all patches with support at a split point.

#### 2.4.3 Comparison of the Approaches

To decide which approach is most appropriate for usage on GPUs we compare their properties. For the comparison we use the variation described in algorithm 2.2 of the Tensor-Product Approach.

In terms of the data structures the tensor-product approach doesn't require dynamic memory allocations in contrast to the Tree-Based Approach. Therefore, it seem to be the better approach for the GPU-implementation. The number of patches is larger than for the Tree-Based Approach. Since only the center cell of the Tree-Based Approach is split unnecessarily in the Tensor-Product Approach, the number of resulting cells in the case of uniform refinement is not expected to be significantly higher.

See tables 2.1 and 2.2 for a comparison of the number of integration cells generated by the 2 approaches.<sup>5</sup>. As we see for the uniform case the ratio for the number of cells is constant at 1.23. Since the center cell is split into 4 cells, for each patch instead of 13 cells, 16 are generated. For the adaptive case the explanation is little more complex. When a patch is refined adaptively it is split into four patches on the next level. Thus additional split points

<sup>&</sup>lt;sup>3</sup>This variation was tested but resulted in a worse performance.

<sup>&</sup>lt;sup>4</sup>Compare the resulting decompositions in figure 2.5.

<sup>&</sup>lt;sup>5</sup>Tested with a CPU-implementation of both approaches.

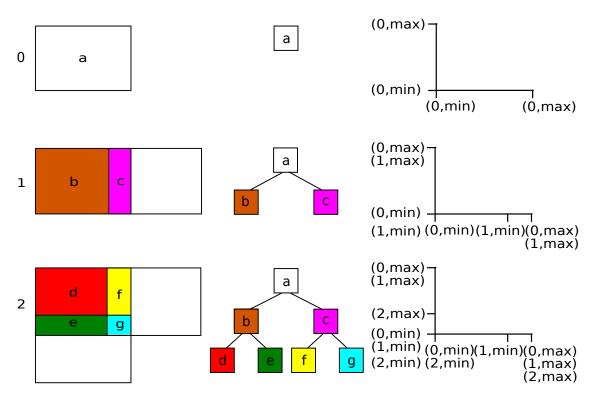

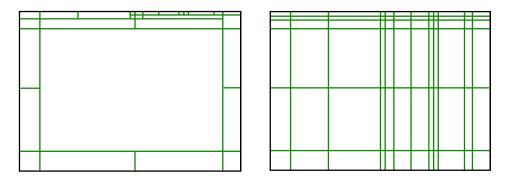

Figure 2.4: Comparison of the decomposition of one patch  $\omega_i$  and two of its neighbors  $C_i$ , generated by two approaches. On the left are the patch (0) and the neighbors (1) and (2), in the middle the tree generated by the Tree-Based Approach and on the right the split points of the Tensor-Product Approach

**Figure 2.5:** The cells generated by the Tree-Based Approach (left) and Tensor-Product Approach (right) from an uniformly refined domain as shown in figure 2.3.

**Table 2.1:** The number of cells generated by both decomposer approaches, for all inner patches of a cover of a square domain (2D) using uniform refinement

| Level $(l)$ | Tree-Based Approach | Tensor-Product Approach | Ratio |

|-------------|---------------------|-------------------------|-------|

| 2           | 52                  | 64                      | 1.23  |

| 4           | 2548                | 3136                    | 1.23  |

| 6           | 49972               | 61504                   | 1.23  |

| 8           | 838708              | 1032256                 | 1.23  |

**Table 2.2:** The number of cells generated by both decomposer approaches, for all inner patches of a cover of a square domain (2D) using h-refinement at the center of the domain

| Level $(l)$ | Tree-Based Approach | Tensor-Product Approach | Ratio |

|-------------|---------------------|-------------------------|-------|

| 2           | 52                  | 64                      | 1.23  |

| 4           | 465                 | 796                     | 1.71  |

| 6           | 949                 | 1798                    | 1.89  |

| 8           | 1433                | 2798                    | 1.95  |

are introduced. The number of additional split points depends on the refinement pattern. See figure 2.6 for an illustration of this situation.

The figure focuses on the center patch, but, as can be seen in the figure as well, all patches around a patch that is adaptively refined are affected. For nested adaptive refinements, the effect spreads for all patches that are adjacent to a refined patch. Figure 2.7 shows the generated cells from the situation shown in figure 2.6. Table 2.2 shows the case for repeated adaptive refinement steps at the center of the domain  $\Omega$ . This generates more cells from a patch, because at each refinement level 4 patches are adaptively refined. We note however that this example case the progression seems to be limited by 2. We conclude that the number of generated cells by the Tensor-Product Approach heavily depends on the refinement strategy used.

An factor of 1.23 for the number of integration cells, as given in the uniform case, will not prevent a GPU-implementation from good performance. We chose the Tensor-Product Approach for the GPU-implementation since heavy pointer usage, in the Tree-Based Approach even when implementing the tree without dynamic memory, is expected to decrease performance.

#### 2.5 Complexity

According to [9, p. 228] the optimal time and space complexity for the assembly is in  $O(Np^{2d})$ . In the following we focus on the metrics, which are relevant for the GPU-implementation. For a derivation of the complexity see [9, p. 228ff.]. Since numerical integration is applied, the optimal bound can hardly realized [9, p. 228]. First estimates for the complexity of the integration are given and afterwards the complexity of the decomposition is discussed.

#### 2.5.1 Integration

Since the PMPUM is a multilevel method, solutions on different levels are computed. We recall that for h-refinement<sup>6</sup> the number of points N is given by  $(2^d)^l$ .

<sup>&</sup>lt;sup>6</sup>H-refinement is a refinement strategy in multi level methods. It increases the number of points or elements with increasing level. This results in a decrease of  $h_i$  for each patch  $\omega_i$ .

Figure 2.6: The decomposition of a patch  $\omega_i$  and its neighborhood  $C_i$  for integration, with adaptive refinement. The basic extent of the patch (bold) and its neighbors is given by the black rectangles. The green rectangles are the patches stretched by  $\alpha_i$ . The needed decomposition is given by all small rectangles in the black bold rectangle. The fill color of the rectangle shows the number of patches on the cells. Yellow stand for 1, red for 2, turquoise for 3 and blue for 4 patches with support on the cell. We note that additional cells are introduced (2 small purple lines) to form rectangular integration cells. See figure 2.3 for the uniform case.

**Figure 2.7:** The cells generated from the situation given in figure 2.6 by the Tree-Based Approach (left) and the Tensor-Product Approach (right)

The total cost  $C_{NI}$  for the integration is:

$$C_{NI} = O(n_{CI} \cdot n_{NI} \cdot C_{EI}) \tag{2.4}$$

Here  $n_{CI}$  is the number of cells used for integration. The number of integration points on one integration cell  $n_{NI}$  depends on the polynomial degree p and the space dimension d.  $C_{EI}$  are the costs for an evaluation of the integrand at an integration point. The number of integration cells  $n_{CI}$  depends on the number of patches N and the decomposition of one patch  $\omega_i$  and its neighbors  $C_i$ .

The number of cells  $n_{CI}$  generated by the Tensor-Product Approach presented in section 2.4.2 from one neighborhood  $C_i$  depends on the space dimension d and the number of neighbors per dimension. When using uniform h-refinement, assuming 2 neighbors per space dimension and linear splines as weight function  $W_i$  the number of cells is given by:

$$n_{CI} = (3+2)^d$$

The required number of integration points  $n_{NI}$  on one cell depends on the space dimension d and the polynomial degree p is:

$$n_{NI} = \left(\frac{p+1}{2}\right)^d$$

In the framework on which the implementation is based, see [20] and [24], the number of integration points used is:

$$n_{NI} = (p+1)^d$$

The costs of the evaluation at an integration point  $C_{EI}$  are given by:

$$C_{EI} = C_{WM_c} + C_{BM_c} + C_{lf} + C_{bf}$$

Here  $\mathcal{C}_{\mathrm{W}M_c}$  denotes the costs for the evaluation of the weight functions of all patches  $M_c$  on the integration cell. The costs for the evaluation of the base functions of all local function spaces  $V_i^{p_i}$  of all patches  $M_c$ . And finally  $\mathcal{C}_{lf}$  and  $\mathcal{C}_{bf}$  are the costs for the evaluation of the linear form and bilinear form respectively. All these costs depend on the number of patches  $\omega_i$  on an integration cell, denoted  $n_{\omega C}$ . The number of patches per cell depends on the decomposer used. In general  $n_{\omega C}$  is limited by the number of neighbors  $card(C_i)$ . Applying the Tensor-Product Approach given in algorithm 2.2 the upper bound is given by 4 in the 2D case and 8 in the 3D case.

For each patch  $\omega_i$  on an integration cell the weight functions of all neighbor patches  $C_i$  need to be evaluated. Therefore, the costs for the evaluation of the weight functions at an integration point are given by:  $\mathcal{C}_{WM_c} = O(M_c)$ . For the computation of the linear and bilinear form all base function  $\psi_i^n$  of the patches  $M_c$  need to be evaluated, which accounts for most of the effort.

The costs for evaluation is given by  $C_{BM_c} = O(M_c \cdot b_i)$ , where  $b_i$  the number of base functions  $\psi_i^n$  in  $V_i^{p_i}$  is given by:

$$b_i = \sum_{i=0}^{p} \binom{d+i-1}{d-1}$$

The proof for this formula uses a combinatorial argument. The number of base functions for a polynomial space with degree p without the base function of the polynomial space with degree p-1 is equal to the number of possibilities to draw p elements from a set of d elements with replacements. Thus adding the number of possibilities for  $0 \le i \le p$  leads to the number of base functions of the polynomial space of degree p.

For the sake of completeness we note the complexity for the evaluation of the linear and bilinear forms. For the evaluation of the linear form  $l(\cdot)$  for the coefficients for all base functions  $b_i$  of all patches on the integration cell  $M_c$  need to be computed:

$$C_{lf} = O(n_{\omega C} \cdot b_i)$$

For the evaluation of the bilinear form for all combinations of patches, with support on the integration cell  $M_c$ , we need to compute the product of the base functions  $b_i$ . This results in the following costs:

$$C_{bf} = O(n_{\omega C}^2 \cdot b_i^2)$$

It is especially interesting, for the discussion of the results in chapter 4, to note the factors by which the costs grow for increased level l and polynomial degree p.

For an increase of the level l by one we can see from formula 2.4 that the effort increases by the number of patches resulting from the increased level. The factor by which the effort increases is therefore given by  $2^d$ .

For an increase of the polynomial degree p, the number of required integration points  $n_{NI}$  increases. For an increase from p-1 to p the number of integration points  $n_{NI}$  increases by the factor  $\left(\frac{\lceil \frac{p+1}{2} \rceil}{\lceil \frac{p}{2} \rceil}\right)^d$ .

When using  $n_{NI} = (p+1)^d$  integration points the resulting factor is:  $\left(\frac{p+1}{p}\right)^d$

For the same increase, some calculus leads to the factor of the number of base function  $b_i$ , that need to be evaluated:  $\frac{d+p}{p}$

The factor for the evaluation of the linear form  $l(\cdot)$  is the same. Finally, for the evaluation of the bilinear form  $a(\cdot,\cdot)$  results in the factor :  $\frac{(d+p)^2}{p^2}$ .

Since the constant for the assembly of the base function  $\psi_i^n$  is the highest, it dominates the effort of the integration for relevant polynomial degrees.

<sup>&</sup>lt;sup>7</sup>The formula for drawing an unordered sample from cover with replacement can be found in [22, p. 18f.].

We summarize, that for the integration, we expect a factor  $2^d$  for an increase of the level l by one for the complexity. For an increase of the polynomial degree p we expect a factor  $\left(\frac{\lceil \frac{p+1}{2} \rceil}{\lceil \frac{p}{2} \rceil}\right)^d \cdot \frac{d+p}{p}$ . When using  $n_{NI} = (p+1)^d$  integration points the resulting factor is  $\left(\frac{p+1}{p}\right)^d \cdot \frac{d+p}{p}$ .

#### 2.5.2 Decomposition

The complexity is influenced by the algorithm used for the decomposition in two ways:

- 1. the complexity of the algorithm itself

- 2. the influence of the number of cells  $n_{CI}$  and the number of patches on a cell  $n_{\omega C}$  generated by the decomposer, discussed in the section 2.5.1.

The algorithms described in section 2.4.2 operate on all patches  $\omega_i$  and their neighborhoods  $C_i$ . The number of neighbors of a patch  $card(C_i)$  is constant in case of uniform p-refinement.<sup>8</sup> Since the complexity of the decomposers is independent from the local approximation spaces  $V_i^{p_i}$ , the decomposition is in O(N). For the discussion of the results in chapter 4 we should note, that it may contain a large prefactor.

The number of generated cells  $n_{CI}$  and the number of patches on an integration cell  $n_{\omega C}$  correlate with the costs for the integration  $\mathcal{C}_{NI}$ .

Both approaches presented in section 2.4.2 generate the minimal number of patches per cell. And therefore the costs for the evaluation at an integration point  $C_{EI}$  are minimal in both cases. For the number of integration cells  $n_{CI}$  we recall from 2.4.3, that for the Tensor-Product Approach  $n_{CI}$  is only a constant factor<sup>9</sup> larger than that of the Tree-Based Approach.

The first modification for the Tensor-Product Approach proposed in section 2.4.2 would lead to a massive increase of the costs for the evaluations  $C_{EI}$  since it requires the evaluation of the weight and base functions of all neighbors of a patch. The complexity of the decomposer would not be affected.

We summarize, that the decomposers have a complexity of O(N), but the prefactor may be large.

<sup>&</sup>lt;sup>8</sup>In case of adaptive refinement the number of neighbors of a patch  $card(C_i)$  may be larger but in all cases the number of neighbors is a lot smaller than the number of patches  $card(C_i) \ll N$ .

<sup>&</sup>lt;sup>9</sup>Only for uniform h-refinement, for adaptive h-refinement the factor seems to converge to 2, see tables 2.1 and 2.2.

## 3 Implementation

In this chapter we present the implementation of the decomposition and the integration described in the previous chapter. Therefore, we give an overview about Compute Unified Device Architecture (CUDA) which is used for the GPGPU-implementation and the technologies used in the framework on which the implementation is based. After that we give insight into some details of the implementation. Therefore, the general workflow is presented first. Then the memory layout as well as the implementation of the algorithms presented in the previous chapter are discussed. Finally we depict the properties and limitations of the implementation.

#### 3.1 CUDA

CUDA was introduced by NVIDIA<sup>TM</sup> in 2006 as a new parallel computing platform and programming model [19]. It aims at simplifying the usage of the performance of GPUs for GPGPU. In the following relevant aspects of CUDA for the implementation are presented. For concepts not covered in this introduction one may start with CUDA C Programming Guide [13]. The CUDA API Reference Manual [11] gives a complete overview about the CUDA application programming interface (API).

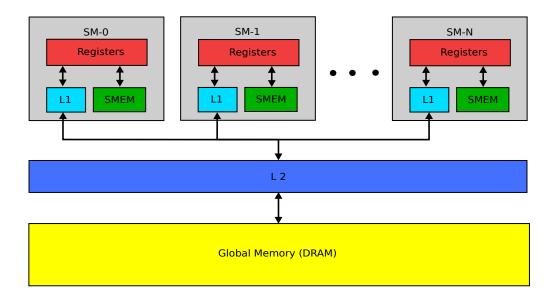

To understand how CUDA is used, some basic understanding of the hardware features of NVIDIA's GPUs is required. Figure 3.1 gives a schematic overview of the components of such a GPU which we in the following refer to as device (compared to the CPU, which we refer to as host). A device consists of multiple Streaming Multiprocessorss (SMs) and multiple memories. The number of multiprocessors varies from type to type, but the features of a single SM is defined by its Compute Capability [13, p. 12f.]. A SM can execute multiple threads in parallel which are organized in warps, that are executed at the same time while other warps on the same SM are inactive. The registers of a SM are split to the number of threads executed on it, but are local to the thread and can not be used for inter thread communication. The shared memory and L1 Cache are used by all threads of a SM where Shared Memory can be used to share data between threads of a thread block<sup>1</sup> and L1 caches access to global memory. Not shown in the figure is the read-only cache which is located in each SM for devices with Compute Capability higher than 3.0. L2 caches all these access for all SMs. The global memory is a dynamic random-access memory (DRAM) which can be accessed by all threads and is used for the communication with the host as well. For detailed specification and limitations for all these components see the CUDA C Programming Guide [13, p. 148 ff.].

<sup>&</sup>lt;sup>1</sup>The concept of thread blocks and this limitation is explained in subsection 3.1.3.

**Figure 3.1:** The hardware components of a CUDA capable GPU from NVIDIA<sup>™</sup> with Compute Capability 2.x, based on [10, p. 26]

In the following paragraphs the usage of these hardware features by the CUDA API is explained. We start with the presentation of the basic execution model. Based on that, we take a look at the thread hierarchy and the memory structure. Then we put the knowledge gained into the context of the infrastructure given by the implementation upon which we built.

#### 3.1.1 Execution Model

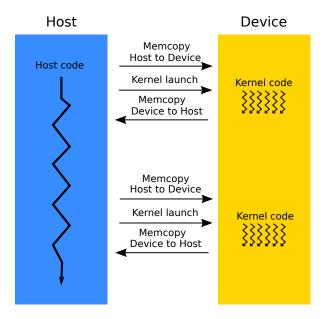

In this section we focus on how the GPU can be utilized by the host. The basic process is shown in figure 3.2. At first the parameters for execution are transferred from host to device. This is done by a memory copy from the host's main memory to the device's global memory using API functions. Then, the kernel, a special C function which is executed in parallel by a specified number of CUDA threads [13, p. 7], is launched by the host. The CUDA threads are organized in thread blocks, which are explained in subsection 3.1.2. Synchronization between host and device enables waiting for a kernel to finish. Afterwards the results are fetched from the device's global memory to host's main memory.

#### 3.1.2 Thread Hierarchy

As mentioned in the previous sections, threads<sup>2</sup> are organized in thread blocks. The grid, which holds all the threads executed in one kernel, consists of multiple thread blocks. This

<sup>&</sup>lt;sup>2</sup>A CUDA thread cannot, in contrast to an ordinary CPU thread, be scheduled independently, but has its own registers and program pointer.

Figure 3.2: The CUDA Execution Model [7, p. 14] based on [13, p. 12]

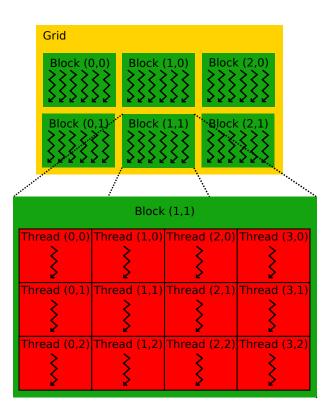

hierarchy is shown in figure 3.3. The number of threads in a thread block can be specified at kernel launch time and is limited by the Compute Capability. The number of thread blocks, which is limited as well, is normally calculated from the number of threads used in the kernel launch and the number of threads per thread block. The concept of warps is fundamental to understand how the size of a thread block should be chosen.

Multiple thread blocks are assigned to a multiprocessor. These thread blocks are partitioned into groups called warps. These warps are scheduled by the warp scheduler of a SM. They start at the same program address and execute exactly the same instructions. If a condition occurs, in which different branches are chosen, all branches are executed sequentially, which massively decreases performance.<sup>3</sup> Only the threads which do need to execute the instructions in a given branch actually execute them, the rest idles. This technique is referred to as Single Instruction Multiple Threads (SIMT) by NVIDIA [13, p. 63ff.]. To allow as many threads as possible to be scheduled in parallel on one SM the number of divergent branches in a thread block and the number of registers used by one thread should be minimized.

Threads of one thread block can wait for all other threads of a thread block to reach a specific point in the kernel.<sup>4</sup> This is needed when using shared memory which is introduced in section 3.1.3.<sup>5</sup> Synchronization of threads of the same thread block implies additional overhead. Therefore, to maximize the performance synchronization should be used well-considered.

<sup>&</sup>lt;sup>3</sup>This situation is referred to as branch divergence.

<sup>&</sup>lt;sup>4</sup>This concept is known form CPUs as "thread fence" or "memory fence".

<sup>&</sup>lt;sup>5</sup>Synchronization of threads of different thread blocks isn't supported. For cuda kernels it is always assumed, that thread blocks can be executed independently.

Figure 3.3: The CUDA Thread Hierarchy [7, p. 14] based on [13, p. 9]

#### 3.1.3 Memory Hierarchy

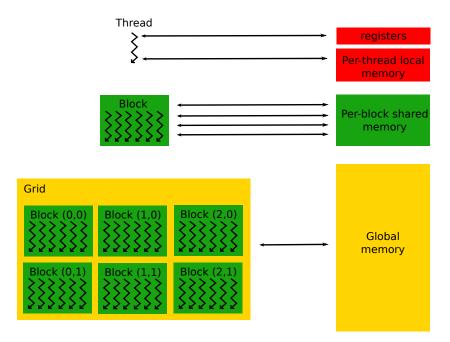

Besides the thread hierarchy the different memories provided by CUDA determine how a task should be parallelized. We present the different memories from local to global scope. See figure 3.4 for an illustration of the memory hierarchy. Each thread has registers which are only accessible by the thread itself. The registers of a SM are distributed among all threads of all active warps on a SM. Because the registers are assigned to a thread for the whole kernel, stopping and restarting a thread<sup>6</sup> can be done with minimum overhead. For devices of Compute Capability between 2.0 and 3.0 the number of registers per thread is limited by 63 and for devices of Compute Capability 3.5 by 255 [13, p. 50]. Thus, the number of registers used by a thread should be minimized to maximize the number of threads which are executed in parallel.<sup>7</sup> The number of registers used should therefore be minimized, as mentioned in

<sup>&</sup>lt;sup>6</sup>The warp scheduler does this when all threads of a thread block wait for memory and another thread block is executed in the mean while.

<sup>&</sup>lt;sup>7</sup>In [23] it is shown, that optimizing performance at instruction level can improve the performance even when this reduces the number of threads executed in parallel.

Figure 3.4: The CUDA Memory Hierarchy based on [13, p. 11]

section 3.1.2. If more memory is needed by a thread, than is available in registers, register spilling occurs. This is explained in the introduction to local memory at the end of this section [13, p. 73].

Shared memory is an on-chip memory which is accessible by all threads of a thread block [13, p. 21 ff.]. Since it is on-chip, see figure 3.1, it is very fast if employed optimally, yet it is significantly slower than registers. It has a maximum size of 48KB for devices of Compute Capability  $\geq 2.0$  and the same physical memory (64KB in total) is used as an L1 cache for global memory access. The division of the memory can be configured at kernel launch time [13, p. 21 ff.].<sup>8</sup>

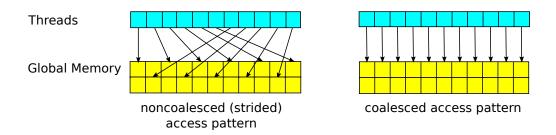

All threads of a grid can access global memory. This is the GPU's DRAM. It has a high latency and low bandwidth, compared with registers or shared memory [13, p. 73]. As described in [13, p. 71ff.], the memory throughput depends massively on access patterns. If threads of a warp are accessing memory addresses next to each other, the memory requests are merged into one transaction. To achieve access patterns which allow coalesced memory access, the memory layout often differs completely from the one used on a CPU. When adjacent threads access memory addresses which are next to each other the access are coalesced in one memory transaction. If not, multiple memory transactions are required. Figure 3.5 illustrates these two different situations. For details about coalesced and non-coalesced access see [12, p. 24 ff.]. All access from all SMs to global memory are cached by a L2 cache.

<sup>&</sup>lt;sup>8</sup>There are two possible configuration: 48KB used as cache and 16 as shared memory, or vise versa.

Figure 3.5: Coalesced vs. non coalesced memory access based on [12, p. 28]

Figure 3.6: The phases to solve a given BVP by the framework