## Fault Tolerance Infrastructure and its Reuse for Offline Testing

Synergies of a Unified Architecture to Cope with Soft Errors and Hard Faults

Von der Fakultät Informatik, Elektrotechnik und Informationstechnik der Universität Stuttgart zur Erlangung der Würde eines Doktors der Naturwissenschaften (Dr. rer. nat.) genehmigte Abhandlung

Vorgelegt von

Michael E. Imhof

aus Kirchheim unter Teck

Hauptberichter: Mitberichter: Prof. Dr. rer. nat. habil. Hans-Joachim Wunderlich Prof. Dr. rer. nat. habil. Sybille Hellebrand

Tag der mündlichen Prüfung:

15. September 2015

Institut für Technische Informatik der Universität Stuttgart 2015

To my family.

## Acknowledgments

It is my pleasure to thank those who accompanied me on my doctoral journey.

I am very grateful to my parents, Karola and Otwin Imhof, and my sister Birgit, for their enduring support and encouragement throughout my education and studies. Without them, I would not have been able to even start with a work like this.

I would like to thank Prof. Hans-Joachim Wunderlich for his professional supervision and for the constructive feedback he provided during this dissertation. He enriched my time at the institute towards becoming an independent researcher with opportunities and challenges for professional and personal development that made the past years so much more than just writing a thesis. I would also like to thank Prof. Sybille Hellebrand for her support and for accepting to be the second adviser of my thesis.

I very much enjoyed the work with colleagues and students who were at some time involved in my activities in Stuttgart. Sorry, I cannot list everyone here, you are not forgotten. I would like to acknowledge those with whom I spend a lot of time in collaborations or personally: Rafał Baranowski, Günter Bartsch, Lars Bauer, Claus Braun, Alejandro Cook, Alexander Czutro, Atefe Dalirsani, Rainer Dorsch, Marcus Eggenberger, Melanie Elm, Laura Rodríguez Gómez, Nadereh Hatami, Stefan Holst, Manuel Jerger, Rauf Salimi Khaligh, Michael Kochte, Chang Liu, Abdullah Mumtaz, Matthias Sauer, Gert Schley, Eric Schneider, Hongyan Zhang, and Christian Zöllin.

Such a work is not possible without administrative and technical assistance: Thank you Mirjam Breitling, Helmut Häfner, Lothar Hellmeier, and Wolfgang Moser.

Stuttgart, September 2015 Michael E. Imhof

### Contents

| Ac  | know   | ledgm   | ents                                              | iii   |

|-----|--------|---------|---------------------------------------------------|-------|

| Со  | ntent  | ts      |                                                   | v     |

| Lis | t of F | igures  |                                                   | xi    |

| Lis | t of T | ables   |                                                   | xv    |

| Ac  | ronyı  | ms      |                                                   | xvii  |

| No  | tatio  | n       |                                                   | xix   |

| Su  | mma    | ry      |                                                   | xxi   |

| Zu  | samn   | nenfass | sung                                              | xxiii |

| 1.  | Intr   | oductio | on                                                | 1     |

|     | 1.1.   | Failur  | e Mechanisms in Integrated Circuits               | 3     |

|     |        | 1.1.1.  |                                                   | 4     |

|     |        | 1.1.2.  | Radiation-induced Soft Errors in CMOS Transistors | 6     |

|     | 1.2.   | Test a  | nd Design for Test                                | 12    |

|     |        | 1.2.1.  | Testability and Test Infrastructure               | 13    |

|     |        | 1.2.2.  | Test Economics                                    | 14    |

|     | 1.3.   | Soft E  | rror Mitigation                                   | 15    |

|     | 1.4.   | Overv   | riew and Contributions                            | 17    |

| Part I – Formal Foundation and Related Work |                                                       |                                                                       | 21 |  |  |

|---------------------------------------------|-------------------------------------------------------|-----------------------------------------------------------------------|----|--|--|

| 2.                                          | Forr                                                  | nal Foundation                                                        | 23 |  |  |

|                                             | 2.1.                                                  | Digital Circuits                                                      | 23 |  |  |

|                                             |                                                       | 2.1.1. Modeling Levels                                                | 23 |  |  |

|                                             |                                                       | 2.1.2. Combinational Circuit                                          | 24 |  |  |

|                                             |                                                       | 2.1.3. Sequential Circuit                                             | 26 |  |  |

|                                             |                                                       | 2.1.4. Defect, Fault, Error, Failure                                  | 26 |  |  |

|                                             | 2.2.                                                  | Soft Errors                                                           | 28 |  |  |

|                                             |                                                       | 2.2.1. Used Soft Error Nomenclature                                   | 28 |  |  |

|                                             |                                                       | 2.2.2. Soft Error Quantification                                      | 29 |  |  |

|                                             |                                                       | 2.2.3. Fault Tolerance                                                | 30 |  |  |

|                                             | 2.3.                                                  | Test of Digital Circuits                                              | 33 |  |  |

|                                             |                                                       | 2.3.1. Fault Models                                                   | 33 |  |  |

|                                             |                                                       | 2.3.2. Test Access through Scan Design                                | 35 |  |  |

|                                             |                                                       | 2.3.3. Test Algorithms                                                | 37 |  |  |

|                                             | 2.4.                                                  | Boolean Satisfiability                                                | 39 |  |  |

| 3.                                          | Related Work in Soft Error Mitigation and Test Access |                                                                       |    |  |  |

|                                             | 3.1.                                                  | Soft Error Mitigation                                                 | 41 |  |  |

|                                             |                                                       | 3.1.1. Dedicated Memories                                             | 41 |  |  |

|                                             |                                                       | 3.1.2. Sequential Elements in Random Logic                            | 45 |  |  |

|                                             | 3.2.                                                  | Test Access                                                           | 51 |  |  |

|                                             |                                                       | 3.2.1. Test Data Compression and Compaction                           | 51 |  |  |

|                                             |                                                       | 3.2.2. Random Access Scan                                             | 53 |  |  |

|                                             | 3.3.                                                  | Combined Solutions                                                    | 56 |  |  |

|                                             |                                                       |                                                                       |    |  |  |

| Pa                                          | rt II                                                 | <ul> <li>Fault Tolerance Infrastructure</li> </ul>                    | 59 |  |  |

| 4.                                          | Non                                                   | -Concurrent Detection and Localization of Single Event Upsets         | 61 |  |  |

|                                             | 4.1.                                                  | Non-Concurrent Architecture                                           | 62 |  |  |

|                                             | 4.2.                                                  | Single Event Upset Detection at Gate Level                            | 63 |  |  |

|                                             |                                                       | 4.2.1. Register Parity Protection                                     | 64 |  |  |

|                                             |                                                       | 4.2.2. Area Efficient Register Parity Computation - Parity-Pair Latch | 66 |  |  |

|                                             | 4.3.                                                  | Single Event Upset Localization at Module Level                       | 68 |  |  |

|                                             |                                                       | 4.3.1. Modulo-2 Address Characteristic                                | 68 |  |  |

|                                             |                                                       | 4.3.2. Optimal Combinational Characteristic Computation               | 71 |  |  |

|                          | 4.4.                                                                                                                       | Experimental Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 74                                                                                                                                                                                                            |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                          |                                                                                                                            | 4.4.1. Experimental Setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 74                                                                                                                                                                                                            |

|                          |                                                                                                                            | 4.4.2. Single Event Upset Detection at Gate Level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 75                                                                                                                                                                                                            |

|                          |                                                                                                                            | 4.4.3. Single Event Upset Localization at Module Level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 81                                                                                                                                                                                                            |

|                          | 4.5.                                                                                                                       | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 83                                                                                                                                                                                                            |

| 5.                       | Con                                                                                                                        | current Online Correction of Single Event Upsets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 85                                                                                                                                                                                                            |

|                          | 5.1.                                                                                                                       | Concurrent Online Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 86                                                                                                                                                                                                            |

|                          | 5.2.                                                                                                                       | Single Error Detection (SED)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 87                                                                                                                                                                                                            |

|                          |                                                                                                                            | 5.2.1. Derivation of a Register Specific Error Condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 88                                                                                                                                                                                                            |

|                          |                                                                                                                            | 5.2.2. Protected Storage of the Error Condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 89                                                                                                                                                                                                            |

|                          | 5.3.                                                                                                                       | Single Error Correction (SEC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 90                                                                                                                                                                                                            |

|                          |                                                                                                                            | 5.3.1. Rapid Correction by Bit-Flipping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 90                                                                                                                                                                                                            |

|                          |                                                                                                                            | 5.3.2. Timing Behavior of the Online Correction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 92                                                                                                                                                                                                            |

|                          | 5.4.                                                                                                                       | Experimental Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 92                                                                                                                                                                                                            |

|                          |                                                                                                                            | 5.4.1. Experimental Setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 93                                                                                                                                                                                                            |

|                          |                                                                                                                            | 5.4.2. Single Error Detection (SED)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 94                                                                                                                                                                                                            |

|                          |                                                                                                                            | 5.4.3. Single Error Correction (SEC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 95                                                                                                                                                                                                            |

|                          | 5.5.                                                                                                                       | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 101                                                                                                                                                                                                           |

|                          |                                                                                                                            | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                               |

| 6.                       | Fau                                                                                                                        | It Tolerance in Presence of Multiple Bit Upsets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 103                                                                                                                                                                                                           |

| 6.                       | <b>Fau</b><br>6.1.                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                               |

| 6.                       |                                                                                                                            | It Tolerance in Presence of Multiple Bit Upsets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 103                                                                                                                                                                                                           |

| 6.                       | 6.1.                                                                                                                       | It Tolerance in Presence of Multiple Bit Upsets Preliminary Error Multiplicity Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <b>103</b><br>104                                                                                                                                                                                             |

| 6.                       | 6.1.<br>6.2.                                                                                                               | It Tolerance in Presence of Multiple Bit Upsets<br>Preliminary Error Multiplicity Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <b>103</b><br>104<br>105                                                                                                                                                                                      |

| 6.                       | 6.1.<br>6.2.<br>6.3.                                                                                                       | It Tolerance in Presence of Multiple Bit Upsets         Preliminary Error Multiplicity Considerations         Online Architecture for Double Errors         Optimal Extended Characteristic Computation                                                                                                                                                                                                                                                                                                                                                                                       | <b>103</b><br>104<br>105<br>106                                                                                                                                                                               |

| 6.                       | 6.1.<br>6.2.<br>6.3.                                                                                                       | It Tolerance in Presence of Multiple Bit Upsets         Preliminary Error Multiplicity Considerations         Online Architecture for Double Errors         Optimal Extended Characteristic Computation         Experimental Evaluation                                                                                                                                                                                                                                                                                                                                                       | <b>103</b><br>104<br>105<br>106<br>108                                                                                                                                                                        |

| 6.                       | 6.1.<br>6.2.<br>6.3.                                                                                                       | It Tolerance in Presence of Multiple Bit Upsets         Preliminary Error Multiplicity Considerations         Online Architecture for Double Errors         Optimal Extended Characteristic Computation         Experimental Evaluation         6.4.1.                                                                                                                                                                                                                                                                                                                                        | <b>103</b><br>104<br>105<br>106<br>108<br>108                                                                                                                                                                 |

| <b>6</b> .<br><b>7</b> . | <ul><li>6.1.</li><li>6.2.</li><li>6.3.</li><li>6.4.</li><li>6.5.</li></ul>                                                 | It Tolerance in Presence of Multiple Bit Upsets         Preliminary Error Multiplicity Considerations         Online Architecture for Double Errors         Optimal Extended Characteristic Computation         Experimental Evaluation         6.4.1.         Experimental Setup         6.4.2.                                                                                                                                                                                                                                                                                              | <b>103</b><br>104<br>105<br>106<br>108<br>108                                                                                                                                                                 |

|                          | <ul><li>6.1.</li><li>6.2.</li><li>6.3.</li><li>6.4.</li><li>6.5.</li></ul>                                                 | It Tolerance in Presence of Multiple Bit Upsets         Preliminary Error Multiplicity Considerations         Online Architecture for Double Errors         Optimal Extended Characteristic Computation         Experimental Evaluation         6.4.1         Experimental Setup         6.4.2         Area Overhead         Summary                                                                                                                                                                                                                                                          | <ul> <li>103</li> <li>104</li> <li>105</li> <li>106</li> <li>108</li> <li>108</li> <li>108</li> <li>110</li> </ul>                                                                                            |

|                          | <ul> <li>6.1.</li> <li>6.2.</li> <li>6.3.</li> <li>6.4.</li> <li>6.5.</li> <li>Area</li> </ul>                             | It Tolerance in Presence of Multiple Bit Upsets         Preliminary Error Multiplicity Considerations         Online Architecture for Double Errors         Optimal Extended Characteristic Computation         Experimental Evaluation         6.4.1. Experimental Setup         6.4.2. Area Overhead         Summary         A Efficient Characteristic Computation                                                                                                                                                                                                                         | <ul> <li>103</li> <li>104</li> <li>105</li> <li>106</li> <li>108</li> <li>108</li> <li>108</li> <li>110</li> <li>111</li> </ul>                                                                               |

|                          | <ul> <li>6.1.</li> <li>6.2.</li> <li>6.3.</li> <li>6.4.</li> <li>6.5.</li> <li>Area</li> <li>7.1.</li> </ul>               | It Tolerance in Presence of Multiple Bit Upsets         Preliminary Error Multiplicity Considerations         Online Architecture for Double Errors         Optimal Extended Characteristic Computation         Optimal Extended Characteristic Computation         6.4.1.         Experimental Setup         6.4.2.         Area Overhead         Summary         Detailed Analysis of the Correction Area Overhead                                                                                                                                                                          | <ul> <li>103</li> <li>104</li> <li>105</li> <li>106</li> <li>108</li> <li>108</li> <li>108</li> <li>110</li> <li>111</li> <li>112</li> </ul>                                                                  |

|                          | <ul> <li>6.1.</li> <li>6.2.</li> <li>6.3.</li> <li>6.4.</li> <li>6.5.</li> <li>Area</li> <li>7.1.</li> <li>7.2.</li> </ul> | It Tolerance in Presence of Multiple Bit Upsets         Preliminary Error Multiplicity Considerations         Online Architecture for Double Errors         Optimal Extended Characteristic Computation         Experimental Evaluation         6.4.1.         Experimental Setup         6.4.2.         Area Overhead         Area Efficient Characteristic Computation         Detailed Analysis of the Correction Area Overhead         Area Efficient Exclusive OR Trees                                                                                                                  | <ul> <li>103</li> <li>104</li> <li>105</li> <li>106</li> <li>108</li> <li>108</li> <li>108</li> <li>110</li> <li>111</li> <li>112</li> <li>112</li> </ul>                                                     |

|                          | <ul> <li>6.1.</li> <li>6.2.</li> <li>6.3.</li> <li>6.4.</li> <li>6.5.</li> <li>Area</li> <li>7.1.</li> <li>7.2.</li> </ul> | It Tolerance in Presence of Multiple Bit Upsets         Preliminary Error Multiplicity Considerations         Online Architecture for Double Errors         Optimal Extended Characteristic Computation         Experimental Evaluation         6.4.1. Experimental Setup         6.4.2. Area Overhead         Summary         Detailed Analysis of the Correction Area Overhead         Area Efficient Exclusive OR Trees         Experimental Evaluation                                                                                                                                    | <ul> <li>103</li> <li>104</li> <li>105</li> <li>106</li> <li>108</li> <li>108</li> <li>108</li> <li>110</li> <li>111</li> <li>112</li> <li>112</li> <li>112</li> <li>115</li> </ul>                           |

|                          | <ul> <li>6.1.</li> <li>6.2.</li> <li>6.3.</li> <li>6.4.</li> <li>6.5.</li> <li>Area</li> <li>7.1.</li> <li>7.2.</li> </ul> | It Tolerance in Presence of Multiple Bit Upsets         Preliminary Error Multiplicity Considerations         Online Architecture for Double Errors         Optimal Extended Characteristic Computation         Optimal Extended Characteristic Computation         Experimental Evaluation         6.4.1.         Experimental Setup         6.4.2.         Area Overhead         Summary         Detailed Analysis of the Correction Area Overhead         Area Efficient Exclusive OR Trees         Experimental Evaluation         7.3.1.         Experimental Setup                      | <ul> <li>103</li> <li>104</li> <li>105</li> <li>106</li> <li>108</li> <li>108</li> <li>108</li> <li>110</li> <li>111</li> <li>112</li> <li>112</li> <li>115</li> <li>115</li> </ul>                           |

|                          | <ul> <li>6.1.</li> <li>6.2.</li> <li>6.3.</li> <li>6.4.</li> <li>6.5.</li> <li>Area</li> <li>7.1.</li> <li>7.2.</li> </ul> | <b>At Tolerance in Presence of Multiple Bit Upsets</b> Preliminary Error Multiplicity Considerations         Online Architecture for Double Errors         Optimal Extended Characteristic Computation         Experimental Evaluation         6.4.1. Experimental Setup         6.4.2. Area Overhead         Summary <b>a Efficient Characteristic Computation</b> Detailed Analysis of the Correction Area Overhead         Area Efficient Exclusive OR Trees         Experimental Evaluation         7.3.1. Experimental Setup         7.3.2. Transmission-Gate Exclusive OR Standard Cell | <ul> <li>103</li> <li>104</li> <li>105</li> <li>106</li> <li>108</li> <li>108</li> <li>108</li> <li>110</li> <li>111</li> <li>112</li> <li>112</li> <li>115</li> <li>115</li> <li>115</li> <li>115</li> </ul> |

| Pa  | Part III – Infrastructure Reuse for Offline Testing 12 |     |

|-----|--------------------------------------------------------|-----|

| 8.  | Test Access through Infrastructure Reuse               | 125 |

|     | 8.1. Unified Architecture                              | 126 |

|     | 8.2. Test Application                                  | 127 |

|     | 8.3. Observing a Test Response                         | 128 |

|     | 8.4. Controlling a Register by Bit-Flipping            | 129 |

|     | 8.5. Test Access Efficiency                            | 130 |

|     | 8.6. Summary                                           | 130 |

| 9.  | Test Sequence Generation                               | 131 |

|     | 9.1. Modeling the Test Sequence Generation             | 132 |

|     | 9.1.1. Circuit Modeling                                | 133 |

|     | 9.1.2. Fault Modeling                                  | 133 |

|     | 9.1.3. Sequential Mapping and Modeling of Bit-Flips    | 134 |

|     | 9.2. Optimal Test Sequence                             | 135 |

|     | 9.3. Bit-Flipping Scan Test Sequence Generation        | 136 |

|     | 9.4. Summary                                           | 139 |

| 10. | Experimental Evaluation of the Offline Test Scheme     | 141 |

|     | 10.1. Experimental Setup                               | 141 |

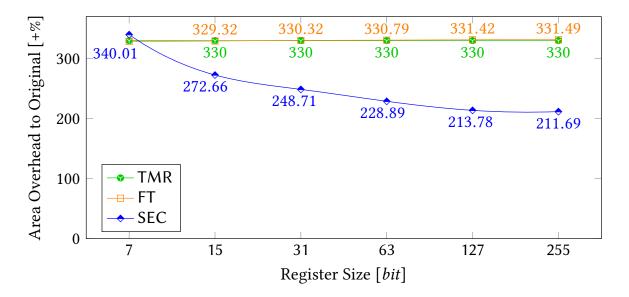

|     | 10.2. Area Overhead                                    | 143 |

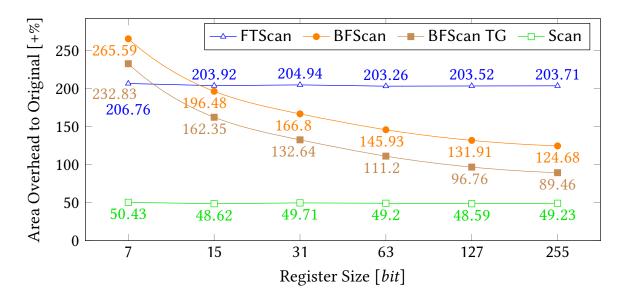

|     | 10.2.1. Dependence on Register Size                    | 143 |

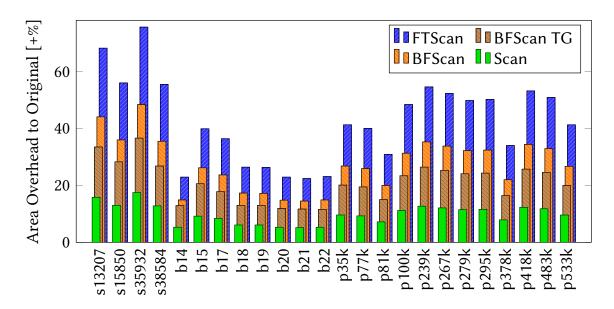

|     | 10.2.2. Application to Benchmark Circuits              | 144 |

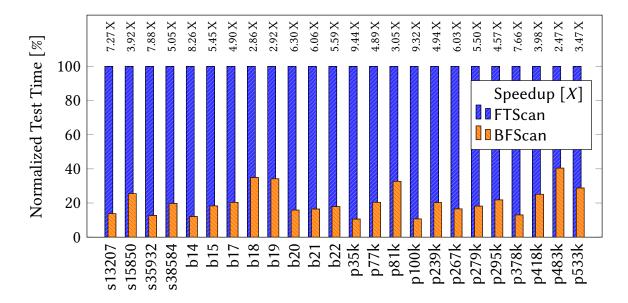

|     | 10.3. Test Application Time                            | 146 |

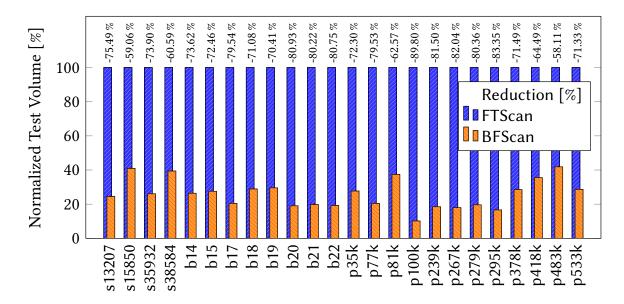

|     | 10.4. Test Data Volume                                 | 147 |

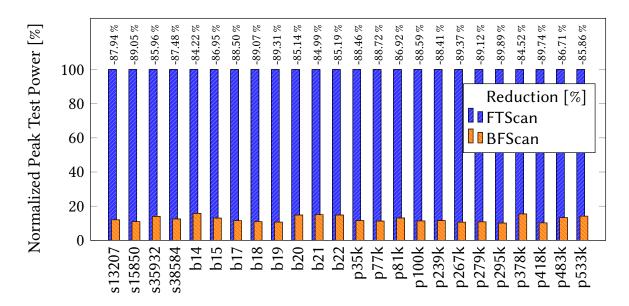

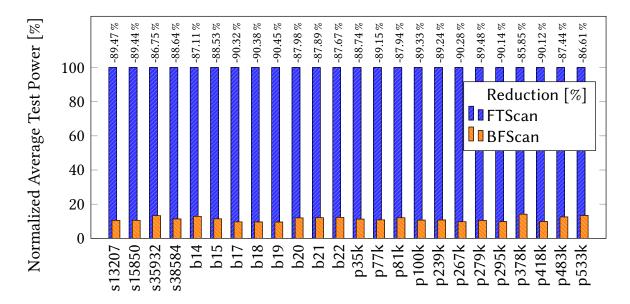

|     | 10.5. Peak and Average Test Power                      | 148 |

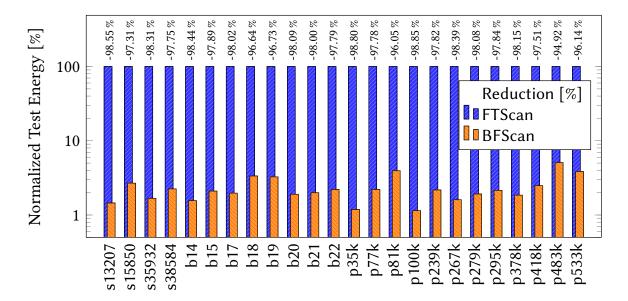

|     | 10.6. Test Energy                                      | 150 |

|     | 10.7. Summary                                          | 151 |

| Su  | mary and Discussion of Part III                        | 153 |

| 11. | Conclusions                                            | 155 |

|     | 11.1. Future Research Directions                       | 156 |

159

### Bibliography

| Part IV – Appendices 17 |        | 175                                                              |     |

|-------------------------|--------|------------------------------------------------------------------|-----|

| A.                      | Tabl   | es with Experimental Results                                     | 177 |

|                         | A.1.   | Electronic Design Automation Flow and Tools                      | 177 |

|                         | A.2.   | Benchmark Circuits                                               | 180 |

|                         | A.3.   | Results - Fault Tolerance Infrastructure                         | 182 |

|                         |        | A.3.1. Non-Concurrent Detection and Localization of Single Event |     |

|                         |        | Upsets                                                           | 182 |

|                         |        | A.3.2. Concurrent Online Correction of Single Event Upsets       | 184 |

|                         |        | A.3.3. Fault Tolerance in Presence of Multiple Bit Upsets        | 184 |

|                         |        | A.3.4. Area Efficient Characteristic Computation                 | 185 |

|                         | A.4.   | Results - Infrastructure Reuse for Offline Testing               | 188 |

|                         |        | A.4.1. Test Access through Infrastructure Reuse                  | 188 |

|                         |        | A.4.2. Test Sequence Generation                                  | 189 |

| Ind                     | lex    |                                                                  | 197 |

|                         |        |                                                                  |     |

| Cu                      | rricu  | lum Vitae of the Author                                          | 201 |

| Pu                      | blicat | ions of the Author                                               | 203 |

# **List of Figures**

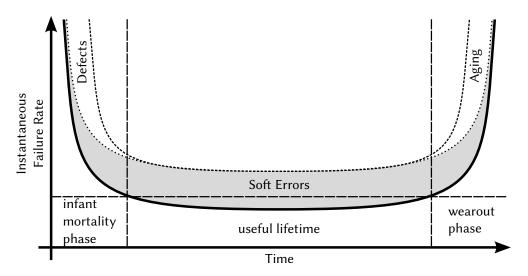

| 1.1. | Bathtub curve depicting the failure rate over time                     | 3  |

|------|------------------------------------------------------------------------|----|

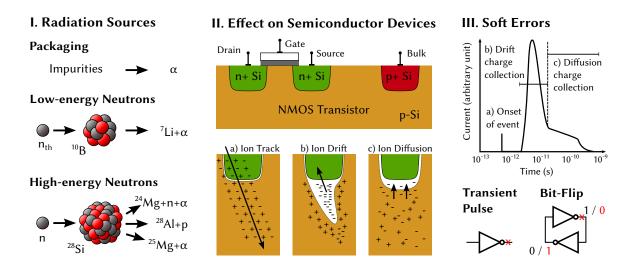

| 1.2. | Soft Errors: From radiation sources over their effect on semiconductor |    |

|      | devices to caused soft errors.                                         | 9  |

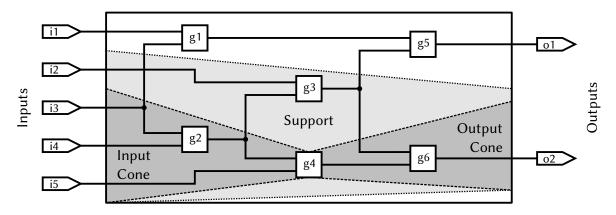

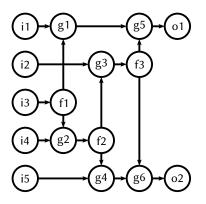

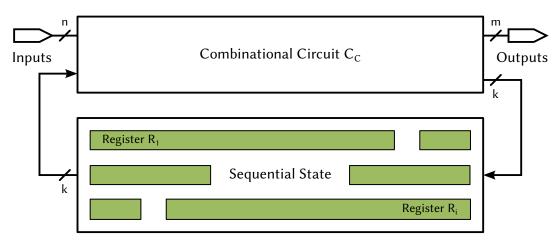

| 2.1. | Combinational Circuit $C_C$                                            | 25 |

| 2.2. | Graph of $C_C$                                                         | 25 |

| 2.3. | Sequential Circuit <i>C</i>                                            | 27 |

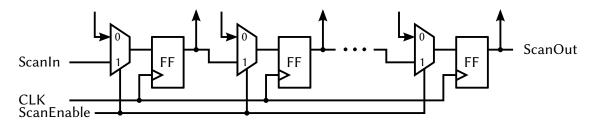

| 2.4. | Multiplexer-based Scannable Register (adopted from [BA00])             | 35 |

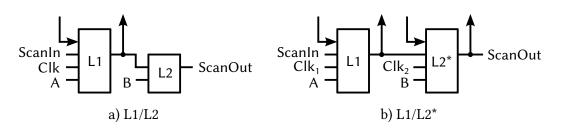

| 2.5. | Shift Register Latch                                                   | 36 |

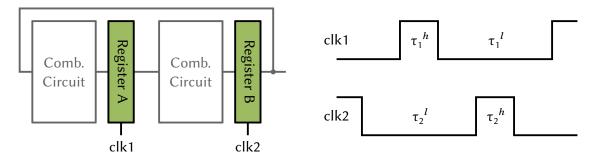

| 2.6. | Non-overlapping Clock Scheme.                                          | 36 |

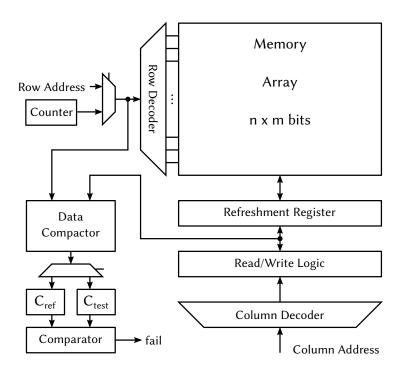

| 3.1. | Architecture of a DRAM with Error Detecting Refreshment (adopted       |    |

|      | from [HWI+02])                                                         | 45 |

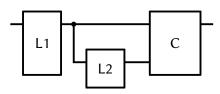

| 3.2. | Principle of Robust Latch Design.                                      | 46 |

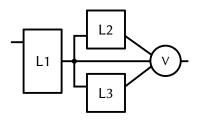

| 3.3. | RAZOR Architecture (adopted from [EKD+03]).                            | 48 |

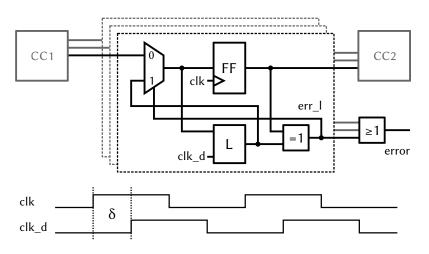

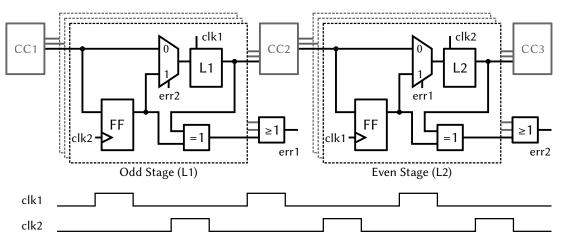

| 3.4. | GRAAL Architecture (adopted from [Nic07])                              | 49 |

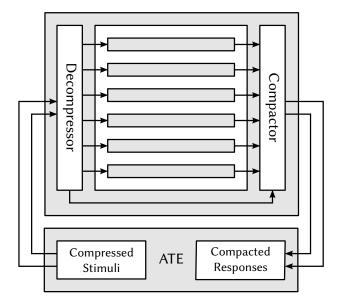

| 3.5. | General Embedded Deterministic Test (EDT) Architecture (adopted        |    |

|      | from [RTK+02])                                                         | 52 |

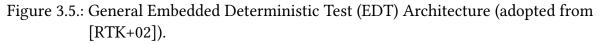

| 3.6. | General Random Access Scan Architecture                                | 54 |

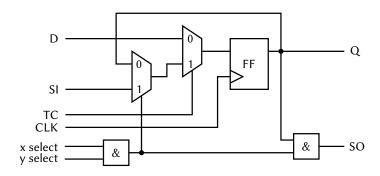

| 3.7. | Multiplexer-based Addressable Random Access Scan Cell                  | 55 |

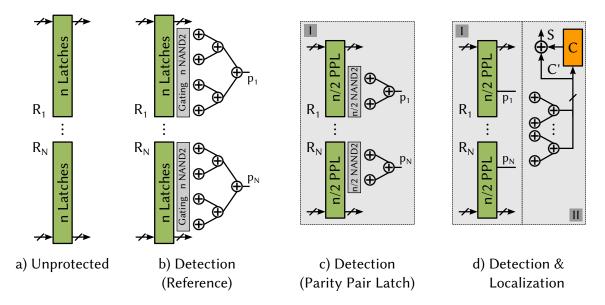

| 4.1. | Presented Non-Concurrent Configurations                                | 63 |

| 4.2. | Reference Parity Tree Implementation $(n = 4)$                         | 65 |

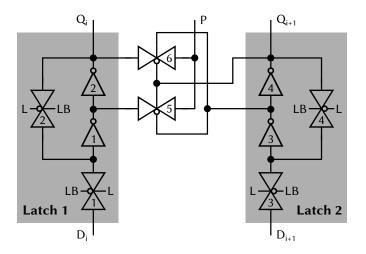

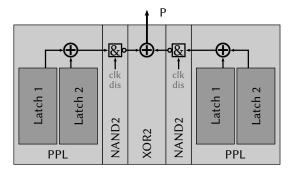

| 4.3. | Schematic of the Parity-Pair Latch (PPL).                              | 66 |

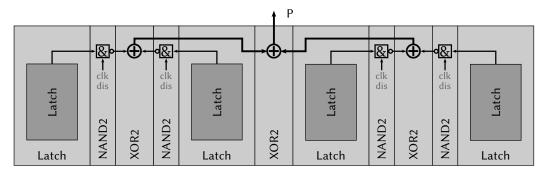

| 4.4. | Parity Tree Implementation utilizing Parity-Pair Latches (n=4)         | 67 |

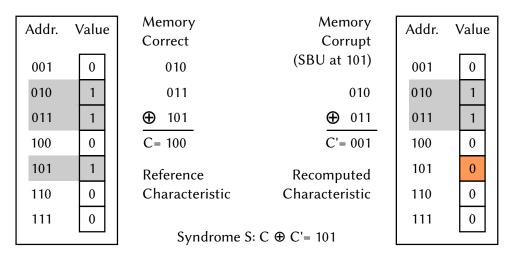

| 4.5. | Modulo-2 Address Characteristic.                                       | 69 |

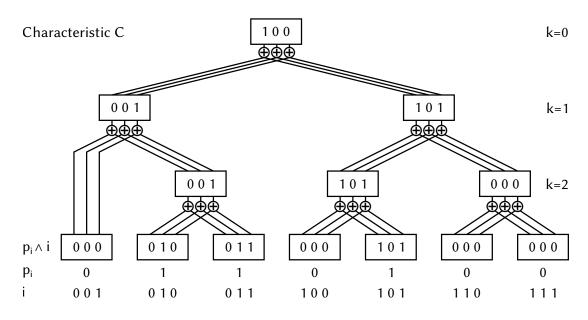

| 4.6. | Non-optimal Computation of the Modulo-2 Characteristic                 | 72 |

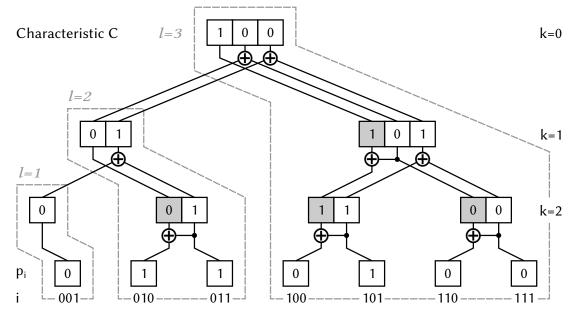

| 4.7. | Optimal Characteristic Tree Organization.                              | 73 |

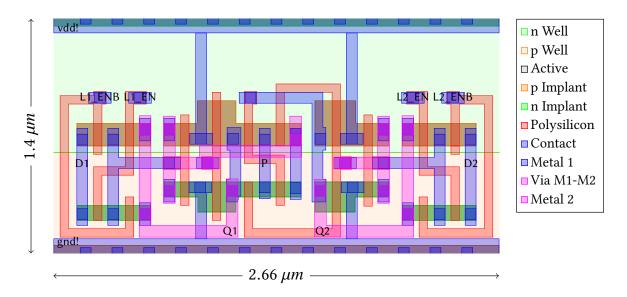

| 4.8. | Layout of the Parity-Pair Latch Standard Cell PPL_X1                   | 76 |

|      |                                                                        |    |

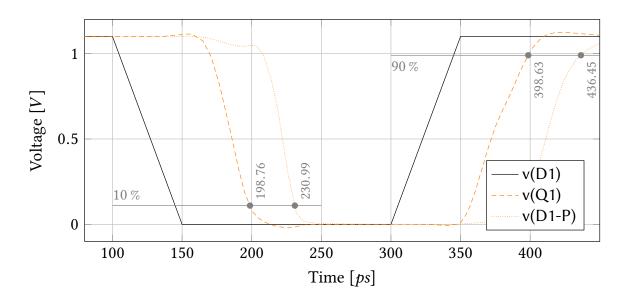

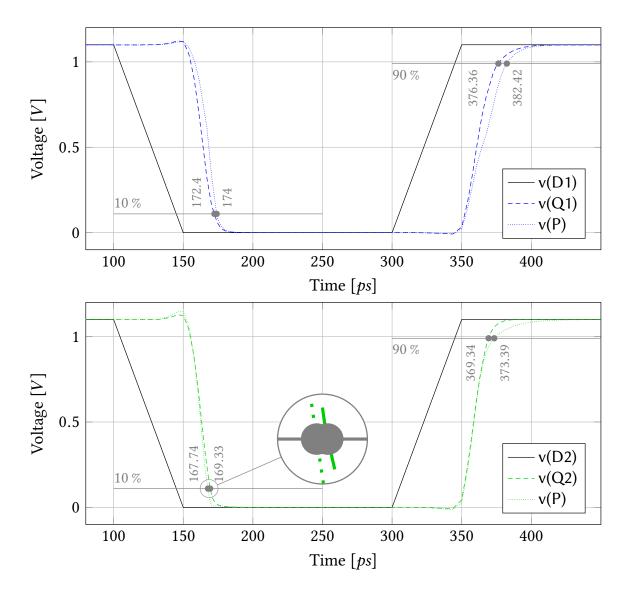

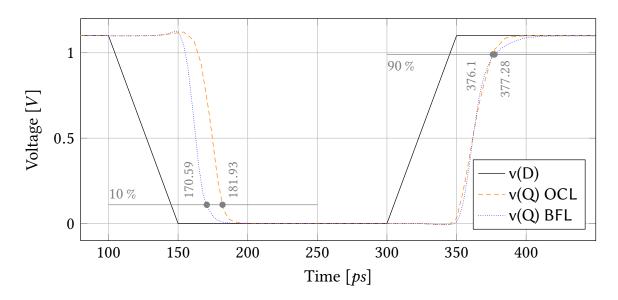

| 4.9.  | Timing Behavior of the OCL Parity-Pair Latch Reference Implemen-<br>tation (DLH_X1 and XOR2_X1): D1-to-Q1 and D1-to-P Delay                | 77    |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 4.10. | Timing Behavior of the Parity-Pair Latch (PPL_X1): D1-to-Q1, D1-to-P<br>and D2-to-Q2, D2-to-P Delay.                                       | 78    |

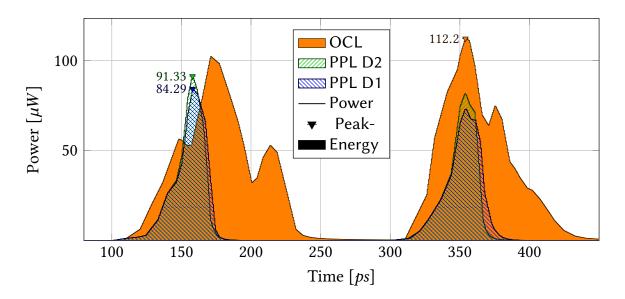

| 4.11. | Power and Energy of the OCL Parity-Pair Latch Reference Imple-                                                                             |       |

| 4 1 2 | mentation (DLH_X1 and XOR2_X1) and the Parity-Pair Latch (PPL_X1).<br>Area Overhead - Parity Computation for a Single Register - Reference | 79    |

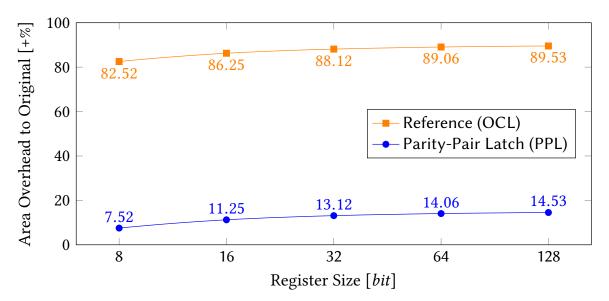

| 7.12. | Implementation (OCL) and Parity-Pair Latch (PPL).                                                                                          | 80    |

| 4.13. | Area Overhead - SEU Localization at Module Level - Reference Im-                                                                           |       |

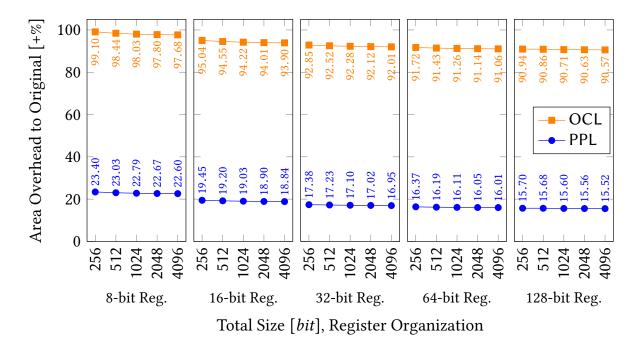

|       | plementation (OCL) and Parity-Pair Latch (PPL)                                                                                             | 82    |

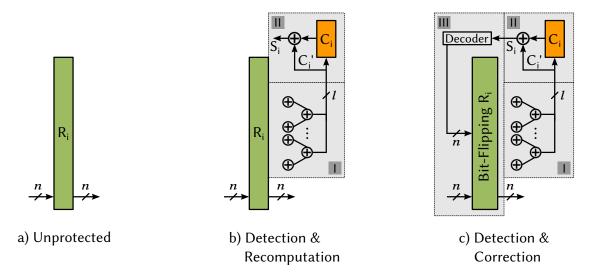

| 5.1.  | Presented Concurrent Online Configurations.                                                                                                | 87    |

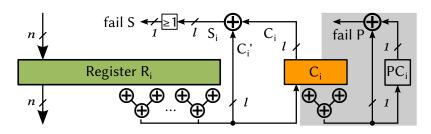

| 5.2.  | Block I and Block II: Deriving and Protecting the Error Condition                                                                          | 88    |

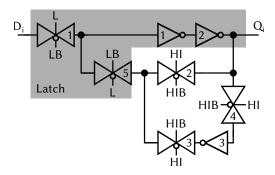

| 5.3.  | Block III: Schematic of the Bit-Flipping Latch (BFL).                                                                                      | 92    |

| 5.4.  | Timing Behavior in Presence of Soft Errors: a) Unprotected Register                                                                        |       |

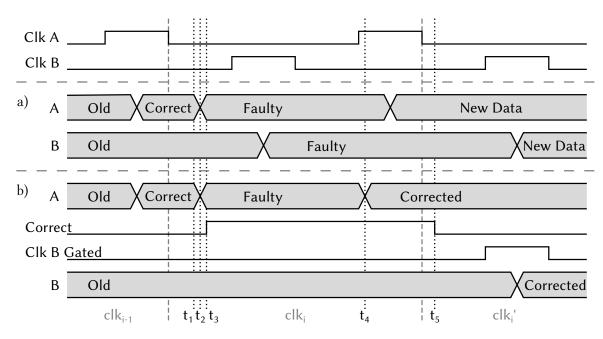

|       | (Figure 5.1-a); b) Protected Register with Correction (Figure 5.1-c).                                                                      | 93    |

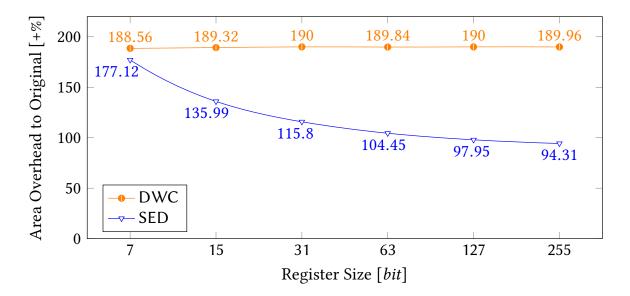

| 5.5.  | Area Overhead - Single Error Detection (SED) - Single Register                                                                             | 95    |

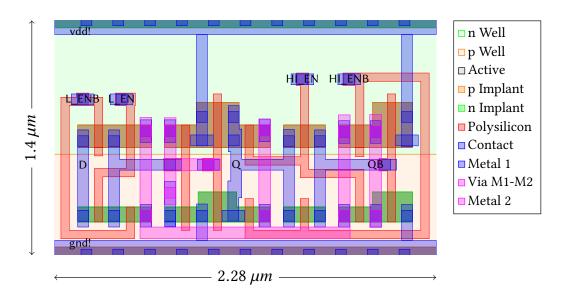

| 5.6.  | Layout of the Bit-Flipping Latch Standard Cell BFLATCH_X1                                                                                  | 96    |

| 5.7.  | Timing Behavior of the OCL Low Enable Latch (DLH_X1) and the                                                                               |       |

|       | Bit-Flipping Latch (BFLATCH_X1): D-to-Q Delay.                                                                                             | 97    |

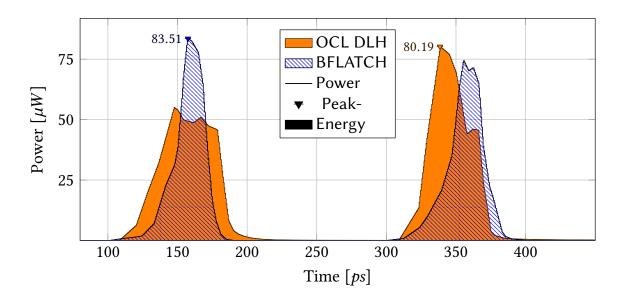

| 5.8.  | Power and Energy of the OCL Low Enable Latch (DLH_X1) and the                                                                              |       |

|       | Bit-Flipping Latch (BFLATCH_X1).                                                                                                           | 98    |

| 5.9.  | Area Overhead - Single Error Correction (SEC) - Single Register                                                                            | 99    |

| 6.1.  | Block I and Block II: Deriving and Protecting the Extended Error                                                                           |       |

|       | Condition in Presence of Double Errors                                                                                                     | 106   |

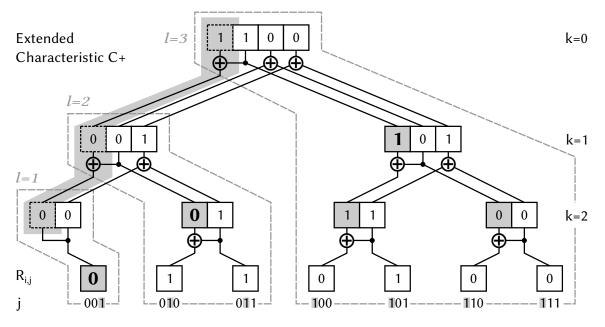

| 6.2.  | Optimal Extended Characteristic Tree Organization.                                                                                         | 107   |

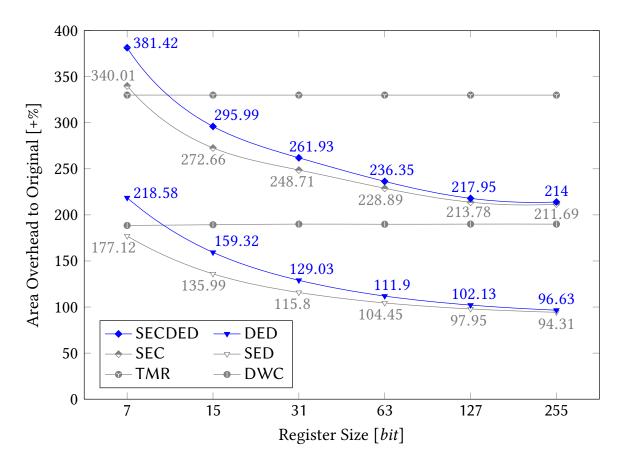

| 6.3.  | Area Overhead - Single and Double Error Detection (DED), Single                                                                            |       |

|       | Error Correction Double Error Detection (SECDED) - Single Register.                                                                        | 109   |

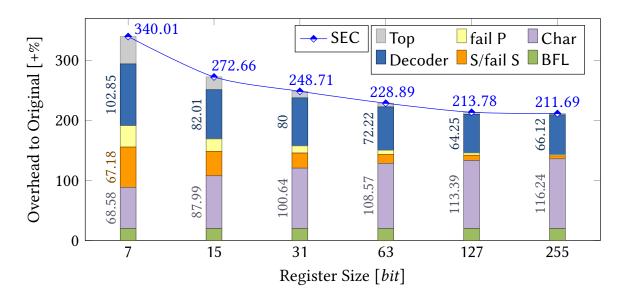

| 7.1.  | Detailed Area Overhead Analysis of the Single Error Correction (SEC)                                                                       |       |

|       | 1                                                                                                                                          | 113   |

| 7.2.  | Exclusive OR Truth Tables.                                                                                                                 | 113   |

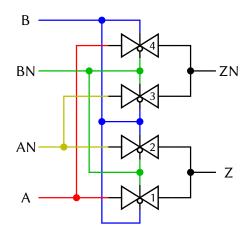

| 7.3.  |                                                                                                                                            | 114   |

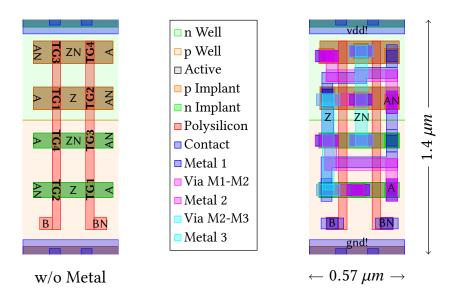

| 7.4.  | Layout of the Transmission-Gate Exclusive OR Standard Cell TGXOR_X1.                                                                       | . 116 |

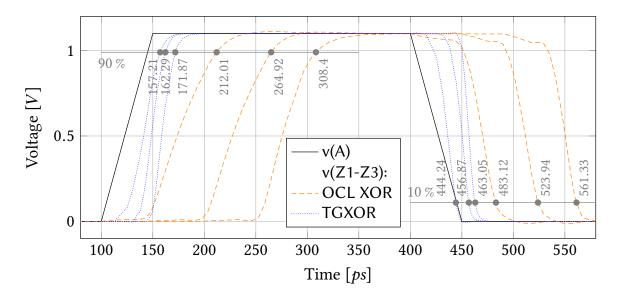

| 7.5.  | Timing Behavior of the OCL Exclusive OR (XOR2_X1) and the Transmissi                                                                       | on-   |

|       | Gate Exclusive OR (TGXOR2_X1).                                                                                                             | 117   |

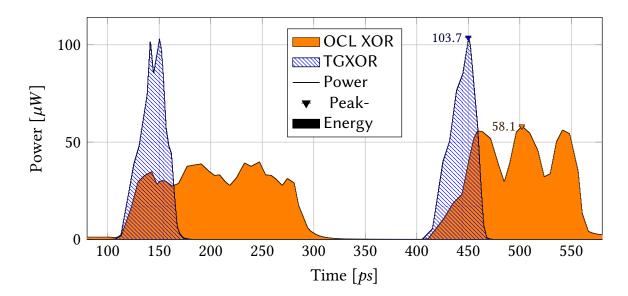

| 7.6.  | Power and Energy of the OCL Exclusive OR (XOR2_X1) and the                                       |       |

|-------|--------------------------------------------------------------------------------------------------|-------|

|       | Transmission-Gate Exclusive OR (TGXOR2_X1).                                                      | 118   |

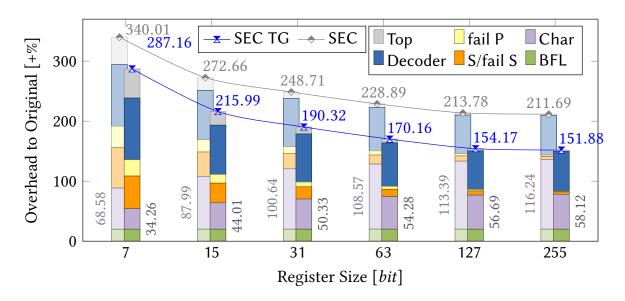

| 7.7.  | Detailed Area Overhead Analysis of the Area Efficient Single Error                               |       |

|       | Correction (SEC TG) utilizing the Transmission-Gate XOR                                          | 119   |

| 7.8.  | Area Overhead - Area Efficient Architectures (SED TG, DED TG, SEC                                |       |

|       | TG, SECDED TG) - Single Register.                                                                | 120   |

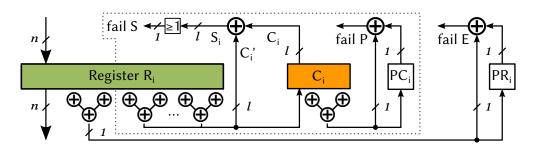

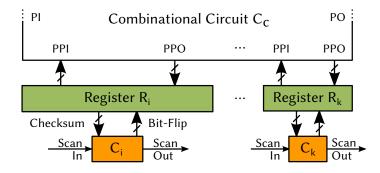

| 8.1.  | Unified Architecture.                                                                            | 126   |

| 8.2.  | Bit-Flipping Scan Test Application.                                                              | 127   |

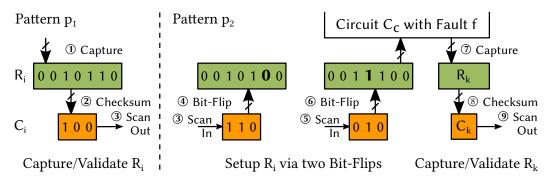

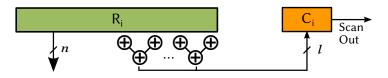

| 8.3.  | Observing the Compacted Test Response of a Register.                                             | 128   |

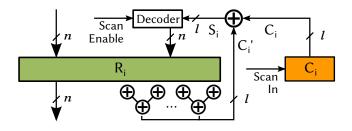

| 8.4.  | Controlling a Register by Bit-Flipping.                                                          | 129   |

|       |                                                                                                  |       |

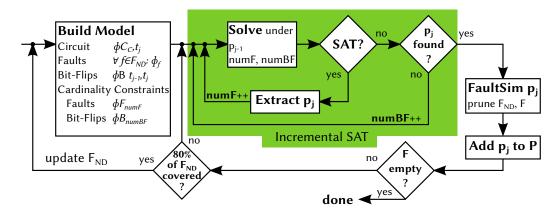

| 9.1.  | Iterative Bit-Flipping Scan Test Pattern Generation.                                             | 132   |

| 9.2.  | Model of a Combinational Circuit $\Phi C_C$ (Single Timeframe) and a                             |       |

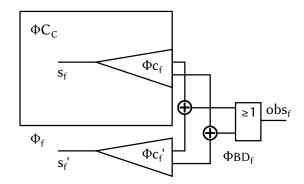

|       | Target Fault $f$ represented by $\Phi_f \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 134   |

| 9.3.  | Sequential Mapping Modeled by Unrolled Timeframes $\Phi C_C, t_{j-1}, \Phi C_C, t_{j-1}$         | $t_j$ |

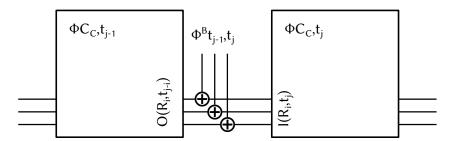

|       | and Model of Bit-Flips $\Phi^B_{t_{j-1},t_j}$ .                                                  | 135   |

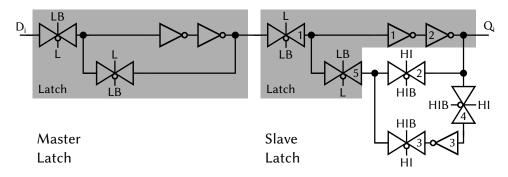

| 10.1. | Schematic of the Bit-Flipping Flip-Flop (BFFF)                                                   | 142   |

| 10.2. | Unified Architecture - Area Overhead for a Single Register                                       | 144   |

| 10.3. | Unified Architecture - Area Overhead for Benchmark Circuits                                      | 145   |

| 10.4. | Test Application Time for Benchmark Circuits                                                     | 146   |

| 10.5. | Test Data Volume for Benchmark Circuits.                                                         | 147   |

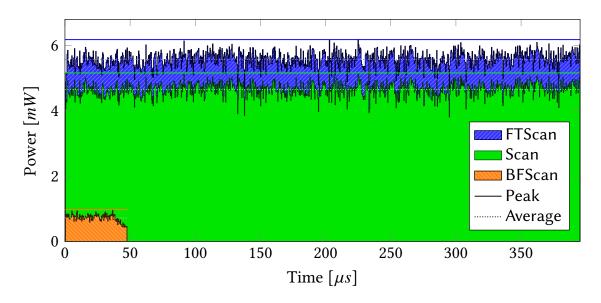

| 10.6. | Peak and Average Test Power and Test Energy for Circuit 'b14'                                    | 148   |

|       | Peak Test Power for Benchmark Circuits.                                                          | 149   |

| 10.8. | Average Test Power for Benchmark Circuits.                                                       | 150   |

| 10.9. | Test Energy for Benchmark Circuits.                                                              | 151   |

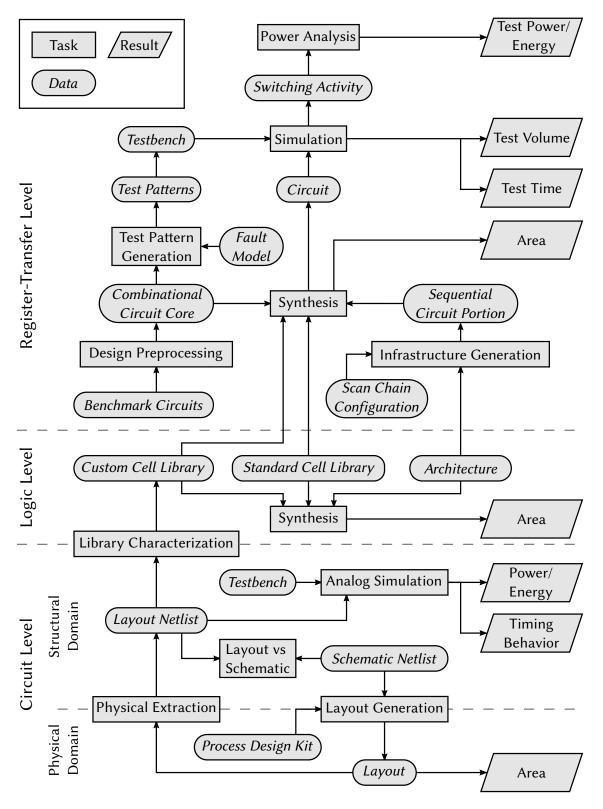

| A.1.  | Experimental Setup with EDA Tool and Data Flow.                                                  | 178   |

### **List of Tables**

| 5.1.  | Time Vulnerability: 8-bit Register with Single Error Correction (SEC).                                                                  | 100 |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.1.  | Double Error Locations - Single Error Correction (SEC, dotted part,<br>Section 5.2) and Single Error Correction, Double Error Detection |     |

|       | (SECDED)                                                                                                                                | 105 |

| A.1.  | Used Electronic Design Automation Tools and Versions                                                                                    | 179 |

| A.2.  | Properties of the used Public Benchmark Circuits                                                                                        | 180 |

| A.3.  | Properties of the used Industrial Benchmark Circuits                                                                                    | 181 |

| A.4.  | Area Overhead - Parity Computation for a Single Register - Reference                                                                    |     |

|       | Implementation (OCL) and Parity-Pair Latch (PPL).                                                                                       | 182 |

| A.5.  | Area Overhead - SEU Localization across Multiple Registers - Refer-                                                                     |     |

|       | ence Implementation (OCL) and Parity-Pair Latch (PPL)                                                                                   | 183 |

| A.6.  | Area Overhead - Single Error Detection (SED).                                                                                           | 184 |

| A.7.  | Area Overhead - Single Error Correction (SEC).                                                                                          | 185 |

| A.8.  | Area Overhead - Single and Double Error Detection (DED), Single                                                                         |     |

|       | Error Correction Double Error Detection (SECDED) - Single Register.                                                                     | 185 |

| A.9.  | Detailed Area Overhead Analysis of Single Error Correction (SEC)                                                                        |     |

|       | Components.                                                                                                                             | 186 |

| A.10. | Detailed Area Overhead Analysis of the Area Efficient Single Error                                                                      |     |

|       | Correction (SEC TG) utilizing the Transmission-Gate XOR                                                                                 | 186 |

| A.11. | Area Overhead - Area Efficient Error Detection (SED TG, DED TG).                                                                        | 187 |

| A.12. | Area Overhead - Area Efficient Error Correction (SEC TG, SECDED                                                                         |     |

|       | TG)                                                                                                                                     | 187 |

| A.13. | Unified Architecture - Area Overhead for a Single Register                                                                              | 188 |

| A.14. | Unified Architecture - Area Overhead for Public Circuits                                                                                | 190 |

| A.15. | Unified Architecture - Area Overhead for Industrial Circuits                                                                            | 191 |

| A.16. | Test Time (TAT) and Test Volume (TDV) for Public Circuits                                                                               | 192 |

| A.17. | Test Time (TAT) and Test Volume (TDV) for Industrial Circuits                                                                           | 193 |

| A.18. | Peak and Average Test Power (TP) and Test Energy (TE) for Public     |     |

|-------|----------------------------------------------------------------------|-----|

|       | Circuits.                                                            | 194 |

| A.19. | Peak and Average Test Power (TP) and Test Energy (TE) for Industrial |     |

|       | Circuits.                                                            | 195 |

## Acronyms

| ATE  | Automatic Test Equipment                |

|------|-----------------------------------------|

| ATPG | Automatic Test Pattern Generation       |

| AVF  | Architectural Vulnerability Factor      |

| CAD  | Computer Aided Design                   |

| CMOS | Complementary Metal Oxide Semiconductor |

| CUT  | Circuit Under Test                      |

| DED  | Double Error Detection                  |

| DFT  | Design For Testability                  |

| DRC  | Design Rule Check                       |

| DWC  | Duplication With Comparison             |

| ECC  | Error-Correcting Code                   |

| EDA  | Electronic Design Automation            |

| EDAC | Error Detection and Correction          |

| FIT  | Failures In Time                        |

| FSM  | Finite State Machine                    |

| FT   | Fault Tolerance                         |

| HDL  | Hardware Description Language           |

| IC   | Integrated Circuit                      |

| LSD  | Level-Sensitive Design                  |

| LSSD | Level-Sensitive Scan Design             |

| LVS  | Layout Versus Schematic                 |

| MBU  | Multiple Bit Upset                      |

| MCU  | Multiple Cell Upset                     |

| MISR | Multiple Input Shift Register           |

| MTBF | Mean Time Between Failures              |

| MTTF                                                                                                                             | Mean Time To Failure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NMR                                                                                                                              | N-Modular Redundancy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| OCL                                                                                                                              | Open Cell Library                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| PDK<br>PEX<br>PI/PO<br>PPI/PPO                                                                                                   | Process Design Kit<br>Physical EXtraction<br>Primary Input / Primary Output<br>Pseudo Primary Input / Pseudo Primary Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| $Q_{crit}$                                                                                                                       | Critical Charge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RAS<br>RPG<br>RTL                                                                                                                | Random Access Scan<br>Random Pattern Generator<br>Register Transfer Level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| SAF<br>SAT<br>SBU<br>SEC<br>SECDED<br>SED<br>SED<br>SEFI<br>SEL<br>SER<br>SET<br>SEU<br>SEU<br>SIC<br>SPICE<br>STF/STR<br>STUMPS | Stuck-At Fault<br>Boolean Satisfiability<br>Single Bit Upset<br>Single Error Correction<br>Single Error Correction, Double Error Detection<br>Single Error Detection<br>Single Event Effect<br>Single Event Effect<br>Single Event Functional Upset<br>Single Event Functional Upset<br>Single Event Latchup<br>Soft Error Rate<br>Single Event Transient<br>Single Event Upset<br>Single Event Upset<br>Single Input Change<br>Simulation Program with Integrated Circuit Emphasis<br>Slow To Fall / Slow To Rise<br>Self-Testing Using a MISR and Parallel Shift register sequence generator |

| TF<br>TG<br>TMR<br>TPG<br>TVF                                                                                                    | Transition Fault<br>Transmission Gate<br>Triple Modular Redundancy<br>Test Pattern Generation / Generator<br>Time Vulnerability Factor                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| VLSI                                                                                                                             | Very Large Scale Integration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

### Notation

#### ⊳ Sets

- Ø empty set

- $\mathbb{B}$  set of Boolean values,  $\mathbb{B} = \{\text{true}, \text{false}\}, \text{denoted as } \{0, 1\}$

- $\mathbb{N}^+$  set of positive natural numbers

- $\mathbb{N}$  set of non-negative natural numbers including 0,  $\mathbb{N} \equiv \mathbb{N}^+ \cup \{0\}$

- $\mathbb{Z}$  set of integer numbers

- $|\cdot|$  cardinality of a set

#### ▷ Set Operators

- $\cup$  union

- $\cap$  intersection

- \ difference

#### ▷ Set Relations

- ∈ element

- ⊂ subset

- $\supset$  superset

- ≡ equivalence

#### ▷ Boolean Operators

- $\overline{\cdot}, \neg$  negation

- $\wedge$  conjunction

- ∨ disjunction

- $\oplus$  exclusive disjunction

- $\Rightarrow$  implication

- $\Leftrightarrow$  equivalence

### $\triangleright$ Boolean function $f : \mathbb{B}^n \to \mathbb{B}$ , where $n \in \mathbb{N}^+$

- $\triangleright$  Vectors

- $\vec{R}$  vector of values,  $\vec{R} := \{r_n, r_{n-1}, \dots, r_1\}$  $\|\vec{R}\|_1$   $l_1$ -norm of a vector,  $\|\vec{R}\|_1 := \sum_{i=1}^n |r_i|$

If not stated otherwise, the least significant bit (lsb) of a binary vector, that is the bit position in a binary number determining whether the number is even or odd, is noted as the right-most bit.

▷ Hamming distance  $\Delta_H(\vec{x}, \vec{y})$  between two vectors  $\vec{x}, \vec{y}$  is defined as the number of coefficients in which they differ:

$$\Delta_H(\vec{x}, \vec{y}) := \sum_{j=1}^n x_j \neq y_j.$$

For binary vectors  $\vec{a}$  and  $\vec{b} \in \mathbb{B}$  the Hamming distance is equal to the number of ones in  $\vec{a} \oplus \vec{b}$ :

$$\Delta_H(\vec{a}, \vec{b}) := \|\vec{a} \oplus \vec{b}\|_1.$$

### **Summary**

The evolution of digital circuits from a few application areas to omnipresence in everyday life has been enabled by the ability to dramatically increase integration density through scaling. However, the continuation of scaling gets more difficult with every generation and poses severe challenges on reliability.

Throughout the manufacturing process the appearance of defects cannot be avoided and further deteriorates with scaling. Hence, the reliability at timepoint zero denoted by the manufacturing yield is not ideal and some defective chips will produce wrong output signals. For this reason, the presence of such *hard faults* needs to be shown prior to delivery during *test* where *automatic test equipment (ATE)* is used to apply a *test set* that covers a predefined set of modeled defects. As some potential defect locations are hard to test using the chips operational interface, additional dedicated *test infrastructure* is included on chip that provides *test access*.

Throughout the operational lifetime reliability is threatened by *soft errors* that originate from interactions of radiation with semiconductor devices and potentially manifest in sequential state corruptions. With further raising soft error rates aggravated by scaling high reliability is maintained by the inclusion of *fault tolerance infrastructure* able to detect, localize and ideally correct soft errors. Thus, the orthogonal combination of two independent infrastructures elevates the area overhead although test support and fault tolerance are never required concurrently.

This work proposes a unified architecture that employs a common infrastructure to provide fault tolerance during operation and test access during test. Similarities between both fields are successfully exploited and traced back to the combination of an efficient sequential state checksum with an effective state update by bit-flipping.

Experiments on public and industrial circuits evaluate the unified architecture in both fields and show an improved area efficiency as well as successful correction during fault tolerance. During test, the results substantiate advantages with respect to test time, test volume, peak and average test power as well as test energy.

### Zusammenfassung

Die Fähigkeit die Integrationsdichte mittels Skalierung drastisch zu steigern, hat die Evolution digitaler Schaltungen von ein paar Anwendungsgebieten zur Allgegenwart im täglichen Leben ermöglicht. Eine Fortführung der Skalierung gestaltet sich jedoch von Generation zu Generation schwieriger und stellt darüber hinaus ernste Herausforderungen an die Zuverlässigkeit.

Das Auftreten von Defekten kann während des Herstellungsprozesses nicht verhindert werden und verschlimmert sich unter Skalierung weiter. Die Zuverlässigkeit zum Zeitpunkt null, ausgedrückt durch die Produktionsausbeute, ist somit nicht ideal und einige defekte Chips erzeugen falsche Ausgangssignale. Aus diesem Grund ist es notwendig vorhandene *permanente Fehler (hard faults)* vor der Auslieferung mittels *Test* zu erkennen. Dabei wird eine vorbestimmte Menge von Defekten in einer *Testmenge* modelliert und diese durch *Testautomaten (Automatic Test Equipment, ATE)* auf jeden Chip angewendet. Da einige der potentiellen Defektstellen mittels der funktionalen Chipschnittstellen nur schwer zu testen sind, wird dem Chip zusätzlich dedizierte *Testinfrastruktur* hinzugefügt, die einen *Testzugriff* bietet.

Während des Systembetriebs wird die Zuverlässigkeit durch *transiente Fehler (soft errors)* bedroht, die durch die Interaktion von Strahlung mit den Halbleitermaterialien hervorgerufen werden. Diese manifestieren sich möglicherweise in Veränderungen des sequentiellen Schaltungszustands. Mit weiter steigenden transienten Fehlerraten, die durch Skalierung verstärkt werden, wird eine hohe Zuverlässigkeit durch das Hinzufügen von *Fehlertoleranzinfrastruktur* beibehalten, die transiente Fehler erkennen, lokalisieren und idealerweise korrigieren kann. Folglich erhöht die orthogonale Kombination zweier unabhängiger Infrastrukturen den Flächenbedarf, obwohl Testunterstützung und Fehlertoleranz nie gleichzeitig benötigt werden.