University of Stuttgart Germany

Student Research Project

# Radiation Mitigation Techniques for EIVE Satellite Mission Payload Computer

Tobias Bischof

Supervisor: Laura Manoliu, M. Sc. Prof. Dr.-Ing. Ingmar Kallfass

Period: 01.11.2021 - 23.03.2022

Stuttgart, 23.03.2022

Postanschrift: Institut für Robuste Leistungshalbleitersysteme Pfaffenwaldring 47

Tel.:

+49 (0) 711 685 68700

Fax.:

+49 (0) 711 685 58700

E-Mail:

sekretariat@ilh.uni-stuttgart.de

Web:

www.ilh.uni-stuttgart.de

D-70569 Stuttgart

# Declaration

I hereby declare that this thesis is my own work and effort and follows the regulations related to good scientific practice of the University of Stuttgart in its latest form. All sources cited or quoted are indicated and acknowledged by means of a comprehensive list of references.

Stuttgart, 23.03.2022

**Tobias Bischof**

# **Executive Abstract**

The 'Exploratory In-orbit Verification of an E/W-band link' (EIVE) satellite mission demonstrates broadband data transmission from the low earth orbit to the earth with data rates of up to 15 Gbit s<sup>-1</sup>. To ensure correct operation of the EIVE satellite and reduce the radiation impacts on EIVE's circuitry, radiation mitigation techniques are mandatory for the payload computer. Therefore, this thesis investigates the radiation mitigation techniques, mechanisms for the protection of the FPGA configuration memory and implements robust encoding mechanisms of the E/W-band validation files. The investigations and the implemented approaches are in line with the EIVE mission power budget limitations.

# Zusammenfassung

Die Satellitenmission 'Exploratory In-orbit Verification of an E/W-band link' (EIVE) demonstriert die breitbandige Datenübertragung von der niedrigen Erdumlaufbahn zur Erde mit Datenraten von bis zu 15 Gbits<sup>-1</sup>. Um den korrekten Betrieb des EIVE-Satelliten sicherzustellen und die Strahlungseinwirkungen auf die Schaltung von EIVE zu reduzieren, sind Strahlungsminderungstechniken für den Nutzlastcomputer erforderlich. Daher untersucht diese Arbeit die Strahlungsminderungstechniken, Mechanismen für den Schutz des FPGA-Konfigurationsspeichers und implementiert robuste Kodierungsmechanismen der E/W-Band-Validierungsdateien. Die Untersuchungen und die implementierten Ansätze stehen dabei im Einklang mit den Leistungsbeschränkungen der Mission.

# Contents

| 1 Motivation |      |                                                 |                                                     |    |  |  |  |

|--------------|------|-------------------------------------------------|-----------------------------------------------------|----|--|--|--|

| 2            | Rad  | Radiation Environment and Mitigation Techniques |                                                     |    |  |  |  |

|              | 2.1  | Radia                                           | tion Environment and Effects                        | 3  |  |  |  |

|              |      | 2.1.1                                           | Environment                                         | 3  |  |  |  |

|              |      | 2.1.2                                           | Radiation Effects                                   | 5  |  |  |  |

|              | 2.2  | Analy                                           | rsis of the EIVE Radiation Environment              | 9  |  |  |  |

|              | 2.3  | Mitiga                                          | ation Approaches                                    | 10 |  |  |  |

|              |      | 2.3.1                                           | Available Techniques                                | 10 |  |  |  |

|              |      | 2.3.2                                           | Possible Levels for Radiation Mitigation            | 20 |  |  |  |

| 3            | Sele | ected R                                         | adiation Mitigation Techniques for the EIVE Project | 23 |  |  |  |

|              | 3.1  | Missie                                          | on Requirements                                     | 23 |  |  |  |

|              | 3.2  | Missie                                          | on Constraints                                      | 24 |  |  |  |

|              |      | 3.2.1                                           | Global Constraints                                  | 24 |  |  |  |

|              |      | 3.2.2                                           | Constraints for Radiation Mitigation Techniques     | 24 |  |  |  |

|              |      | 3.2.3                                           | Constraints for the MPSoC                           | 25 |  |  |  |

|              | 3.3  | Consi                                           | deration of Radiation Mitigation Techniques         | 26 |  |  |  |

|              |      | 3.3.1                                           | Techniques with Information Redundancy              | 26 |  |  |  |

|              |      | 3.3.2                                           | Spatial Redundancy                                  | 27 |  |  |  |

|              |      | 3.3.3                                           | Temporal Redundancy                                 | 28 |  |  |  |

|              |      | 3.3.4                                           | No redundancy                                       | 29 |  |  |  |

|              |      | 3.3.5                                           | Implemented Radiation Mitigation Techniques in EIVE | 30 |  |  |  |

| 4            | Inte | gratior                                         | n of the SEM-IP Core into EIVE                      | 33 |  |  |  |

|              | 4.1  | Neces                                           | sity of the SEM-IP Core                             | 33 |  |  |  |

|              | 4.2  | The Se                                          | oft-Error Mitigation IP Core                        | 33 |  |  |  |

|              |      | 4.2.1                                           | Latency Times of the SEM-IP Core                    | 34 |  |  |  |

|              |      | 4.2.2                                           | Structure and Submodules                            | 37 |  |  |  |

|              |      | 4.2.3                                           | Operational Concept                                 | 39 |  |  |  |

|              | 4.3  | Hardy                                           | ware Integration                                    | 41 |  |  |  |

|              |      | 4.3.1                                           | Low-Level Integration Approach                      | 42 |  |  |  |

|              |      | 4.3.2                                           | High-Level Integration Approach                     | 44 |  |  |  |

|              |      | 4.3.3                                           | Implemented hardware                                | 45 |  |  |  |

|                                                                        | 4.4            | Softwa  | Software Integration                                               |    |  |  |  |

|------------------------------------------------------------------------|----------------|---------|--------------------------------------------------------------------|----|--|--|--|

|                                                                        | 4.5 Testing    |         |                                                                    |    |  |  |  |

|                                                                        |                | 4.5.1   | Test Scenario 1: Initialization                                    | 49 |  |  |  |

| 4.5.2 Test Scenario 2: Injection and Correction of a Correctable Error |                |         |                                                                    |    |  |  |  |

|                                                                        |                | 4.5.3   | Test Scenario 3: Injection and Correction of a Uncorrectable Error | 51 |  |  |  |

|                                                                        |                | 4.5.4   | Testing Summary                                                    | 51 |  |  |  |

| 5                                                                      | Erro           | r Detec | tion and Correction Codes for EIVE                                 | 53 |  |  |  |

|                                                                        | 5.1            | Theory  | y of EDAC                                                          | 53 |  |  |  |

|                                                                        |                | 5.1.1   | Error Detection Codes                                              | 54 |  |  |  |

|                                                                        |                | 5.1.2   | Error Correction Codes                                             | 56 |  |  |  |

|                                                                        | 5.2            | Choos   | ing EDAC Approach for EIVE                                         | 60 |  |  |  |

|                                                                        |                | 5.2.1   | Selection of Error Correction Code                                 | 60 |  |  |  |

|                                                                        |                | 5.2.2   | Selection of Coding Sequence                                       | 61 |  |  |  |

|                                                                        | 5.3            | Softwa  | are Design                                                         | 63 |  |  |  |

|                                                                        |                | 5.3.1   | Modularization                                                     | 67 |  |  |  |

|                                                                        |                | 5.3.2   | Integration                                                        | 68 |  |  |  |

| 6                                                                      | Con            | clusion | and Further Work                                                   | 71 |  |  |  |

| Bi                                                                     | Bibliography 7 |         |                                                                    |    |  |  |  |

| Lis                                                                    | st of A        | Abbrev  | iations                                                            | 75 |  |  |  |

# List of Figures

| 1.1  | Electronic subsystems and their contributors in the EIVE project.                  | 2  |

|------|------------------------------------------------------------------------------------|----|

| 2.1  | Space radiation sources and their locations.                                       | 4  |

| 2.2  | Single-event transient and its effects                                             | 7  |

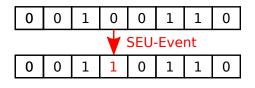

| 2.3  | Single-event upset                                                                 | 7  |

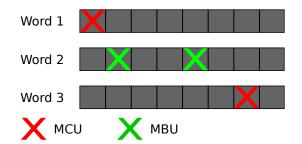

| 2.4  | Multiple-cell upsets and multiple-bit upsets                                       | 8  |

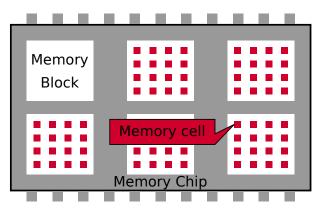

| 2.5  | Schematic structure of a memory device                                             | 12 |

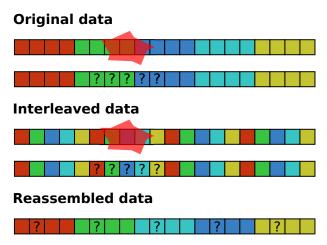

| 2.6  | SEEs in memory with and without bit interleaving.                                  | 12 |

| 2.7  | Schematic structure of a duplex architecture with comparator.                      | 14 |

| 2.8  | Schematic structure of a full TMR architecture with voter and different errors     | 14 |

| 2.9  | Schematic structure of a TTR architecture with delay elements, memories and voter. | 15 |

| 2.10 | Schematic structure of instruction-level redundancy.                               | 18 |

| 2.11 | Task-level redundancy by separating tasks into three execution stages and perform- |    |

|      | ing consistency checks.                                                            | 19 |

| 2.12 | Overview of stages, where radiation mitigation is possible                         | 21 |

| 4.1  | Configuration memory layout of the Xilinx UltraScale+ XCZU6EG                      | 34 |

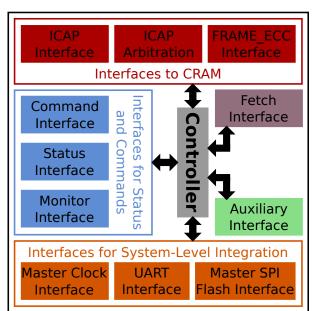

| 4.2  | Interfaces of the SEM-IP core.                                                     | 37 |

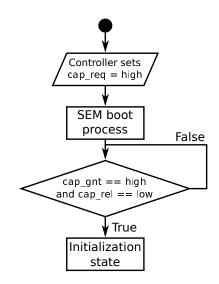

| 4.3  | Start-up procedure of the controller.                                              | 39 |

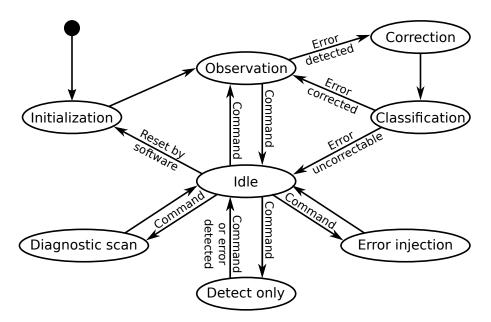

| 4.4  | State transition diagram of the SEM controller in mitigation mode.                 | 41 |

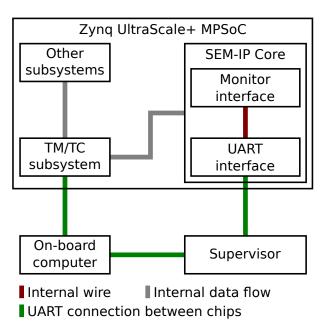

| 4.5  | Connections of the SEM-IP core together with system overview.                      | 42 |

| 4.6  | Low-level SEM-IP core integration.                                                 | 43 |

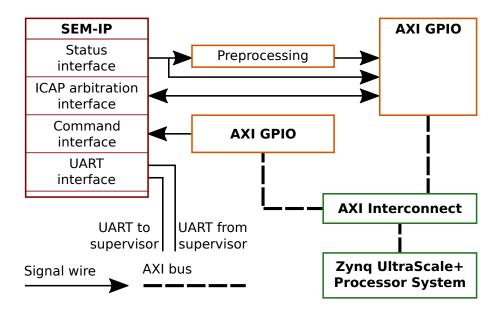

| 4.7  | Signal preprocessing block, used for low-level SEM integration.                    | 44 |

| 4.8  | High-level SEM-IP core integration.                                                | 45 |

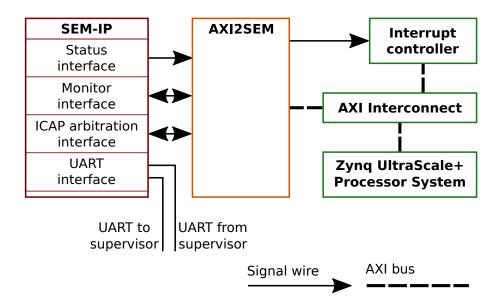

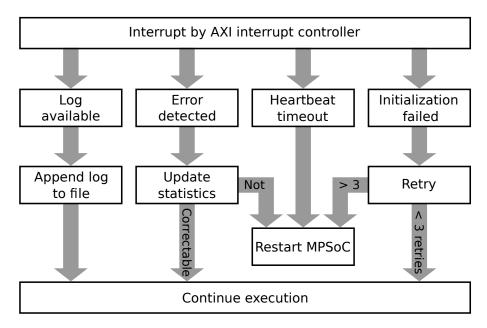

| 4.9  | Interrupt-based integration of the SEM-IP in PLOC software                         | 47 |

| 4.10 | Radiation toolbox in the EIVE test environment.                                    | 50 |

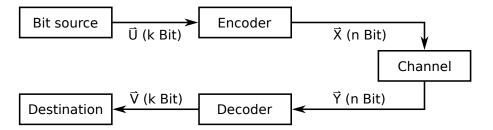

| 5.1  | Block diagram for encoding and decoding.                                           | 54 |

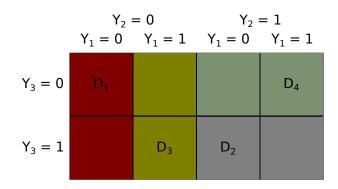

| 5.2  | Illustration of decoding regions.                                                  | 55 |

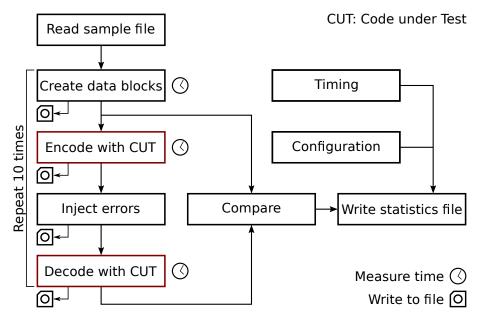

| 5.3  | Testbench to compare coding approaches                                             | 63 |

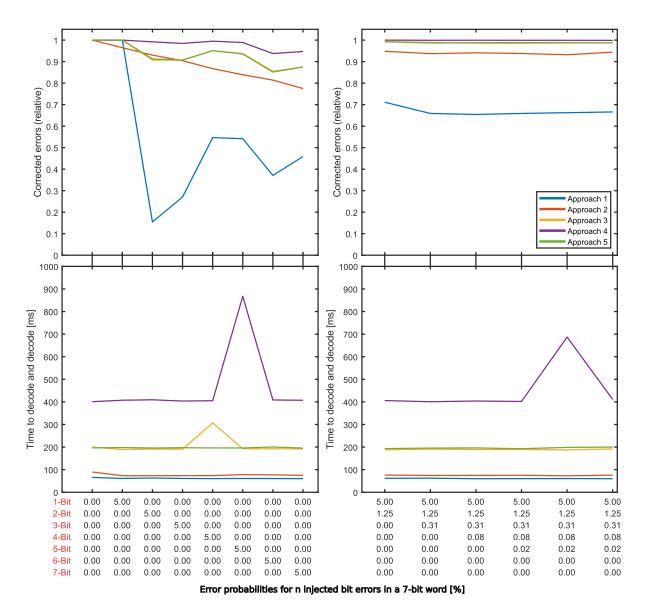

| 5.4  | Error correction capabilities against computation time at $B = 0.05$               | 64 |

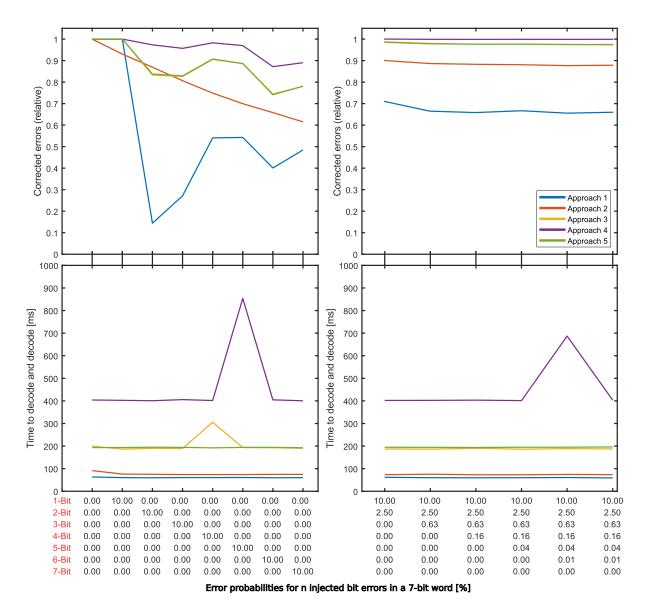

| 5.5  | Error correction capabilities against computation time at $B = 0.1$                | 65 |

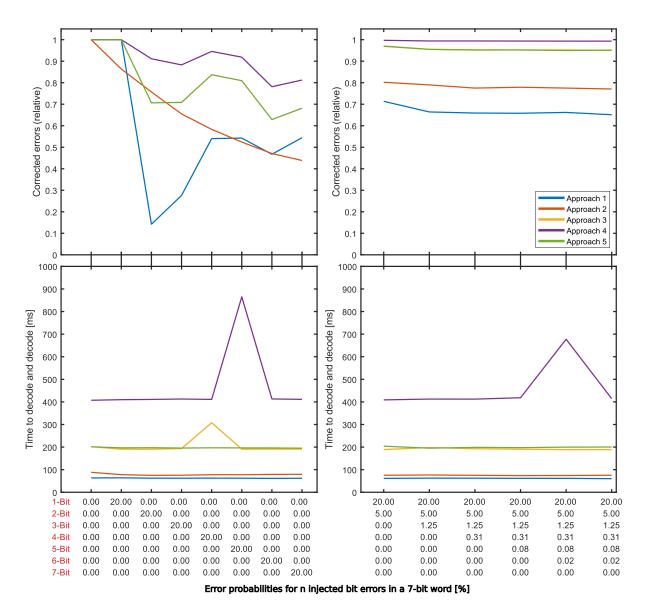

| 5.6  | Error correction capabilities against computation time at $B = 0.2$                | 66 |

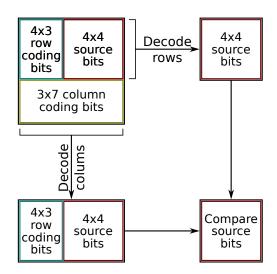

| 5.7  | Decoding of two-dimensional blocks.                                                | 67 |

# List of Tables

| 2.1 | Subdivision of single-event effects                                               | 6  |

|-----|-----------------------------------------------------------------------------------|----|

| 2.2 | Summary of single-event effects and their presence on digital electronics         | 8  |

| 2.3 | Memory types in a FPGA and their sizes for the Xilinx UltraScale+ MPSoC           |    |

|     | XCZU6EG, used in EIVE mission                                                     | 9  |

| 2.4 | Number of single-event error expected for EIVE in events per day.                 | 10 |

| 2.5 | Total ionizing doses expected for EIVE with start in Q2 2022 and sun-synchronous  |    |

|     | orbit at 490 to 520 km altitude, calculated with the OMERE tool                   | 10 |

| 2.6 | Summary of available radiation mitigation techniques.                             | 11 |

| 3.1 | Available and consumed power in the EIVE project.                                 | 24 |

| 3.2 | Available and used resources in the Xilinx UltraScale+ MPSoC for the EIVE mission |    |

|     | from Xilinx utilization report.                                                   | 25 |

| 3.3 | Summary of information-redundancy based radiation mitigation techniques           | 27 |

| 3.4 | Summary of spatial-redundancy-based radiation mitigation techniques               | 28 |

| 3.5 | Radiation mitigation techniques for EIVE                                          | 31 |

| 4.1 | Error mitigation durations for different error types and SEM-IP configurations    | 36 |

| 4.2 | Configurations of the SEM-IP core.                                                | 40 |

| 4.3 | Telecommands and telemetry packages used for system-level testing of the SEM      |    |

|     | integration                                                                       | 48 |

| 4.4 | Commands for the SEM controller.                                                  | 49 |

| 4.5 | SEM initialization report                                                         | 49 |

| 4.6 | SEM correction report for exactly one correctable error.                          | 50 |

| 4.7 | SEM correction report for an uncorrectable CRC error.                             | 51 |

| 5.1 | Example codebook for a code with $k = 2$ and $n = 3$                              | 54 |

| 5.2 | Syndrome-coset-leader table of $d_{min} = 3$ , $n = 7$ and $k = 4$                | 59 |

| 5.3 | Comparison of relative amount of correctable errors                               | 60 |

| 5.4 | Hamming code based coding approaches for E/W-band sample protection               | 62 |

| 5.5 | Needed matrix operations for the coding subsystem.                                | 68 |

# 1 Motivation

The project 'Exploratory In-orbit Verification of an E/W-band link' (EIVE) explores broadband satellite communication from the low earth orbit (LEO) to the earth by transmitting data in the frequency band between 71 GHz and 76 GHz with a data rate of up to 15 GBits<sup>-1</sup>. During transmission, atmospheric effects will alter the sent data. For this reason, a key task of the EIVE project is to send known pseudo-random bit sequences (PRBS) in order to analyze the transmission quality under different weather conditions and demonstrate the feasibility of the desired radio downlink throughput. Furthermore, it is possible to take and transmit full-HD pictures and 4K-livestreams with the on-board high resolution camera to showcase real-world scenarios with the need of high data rate transmissions [1].

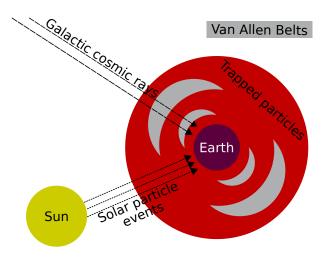

The EIVE satellite represents the joint work of multiple project partners. Figure 1.1 shows a simplified overview of the subsystems, relevant for this work, as well as the responsible division. The Institut für Raumfahrtsysteme (IRS) is responsible for the on-board computer (OBC), which acts as a master circuitry for the multiMIND board and the companion boards. Therefore, the OBC controls the functionality of all subsystems in the satellite, depending on the satellites position and scheduled missions. The OBC receives commands and transmits execution log reports and current state information through a S-band link [2].

In order to execute commands, the on-board computer has to communicate with multiMIND, which is designed by Thales Alenia Space (TAS) and consists of two separate boards. The processing board consist of a Xilinx UltraScale+ MPSoC, where user-defined logic and software can be placed. To ensure the MPSoCs functionality, the processing board also contains a supervision circuitry. This processing board is designed in a way, that users of the multiMIND solution are able to do computational tasks, such as processing data and interacting with different parts on one or more companion boards, for instance an E/W-band link or a 4K-camera in the case of EIVE. Also, the processing board has components which are not accessible by the user. These components are dealing with supervisory tasks like storing and updating boot images, monitoring power lines, booting and shutting down the MPSoC, protecting it from latch-up events and observing the MPSoC with watchdogs. As an interface between processing core, OBC, companion boards and other electronic components, the mission interface board is an essential part of multiMIND. Compared to the processing core, it is a mission specific board, because the companion boards and other used electronic components strongly vary [3], [4].

As a last part of the electronic systems in the EIVE project, there are the already mentioned companion boards. For EIVE, the companion board is an evaluation board for a digital to analogue converter. It receives digital data from the FPGA and puts analogue data directly to the E/W-band

Figure 1.1: Electronic subsystems and their contributors in the EIVE project.

link and is part of the research of the Institute of Robust Power Semiconductor Systems (ILH) [2]. It is well established, that radiation present in space may have destructive effects on electronic components. The effects can differ in severity, since flipped bits may have no effects or can result in data corruption. There is also a chance to result in more severe injuries, for example degradation of microelectronics, biasing of instrument reads and damage of the physical circuits. The consequences of these effects can be wrong calculation results, altered program flows, data loss, unreliable measurements and total, non-recoverable device failures, which implies the loss of the mission. Even if some errors are negligible and have no effect at all, they should be found and fixed because they might have some impact at a later point in time [5]. Since all mentioned incidents can occur in the EIVE project, a stable radiation mitigation concept is needed. Therefore, this thesis investigates radiation impacts and basic mitigation techniques, before a solid radiation mitigation concept is proposed and implemented in order to increase the lifetime and robustness of the EIVE CubeSat.

# 2 Radiation Environment and Mitigation Techniques

This chapter starts with a short, but general overview about radiation environments, followed by EIVE-specific radiation challenges. Afterwards, radiation impacts on electronic devices, especially CMOS-based digital circuits and memories, are discussed. Based on this knowledge, techniques for radiation effects mitigation are investigated.

# 2.1 Radiation Environment and Effects

Before proceeding to radiation mitigation techniques, the radiation environment must be explained in a general way, starting from the definition of radiation over an outline of origins until characterization of different radiation types.

# 2.1.1 Environment

Before discussing the radiation environment, it is worth to point out that radiation is defined as any form of energy, emitted or transmitted by or between energetic sources [6]. For space radiation, which is considered here, the type of energy is limited to highly energetic particles, almost moving with light speed, and their corresponding wavelength. In general, this radiation can be found everywhere on earth. Apart from radiation sources in space, the earth itself is emitting radiation through natural radiation sources like radioactive elements, and human made ones like mobile phone networks. In comparison, radiation fluxes from earth sources are magnitudes of order smaller than from space ones. Additionally, through the existence and shielding functionality of the each magnetic field, radiation with its origin on earth is negligible in space [6], [7].

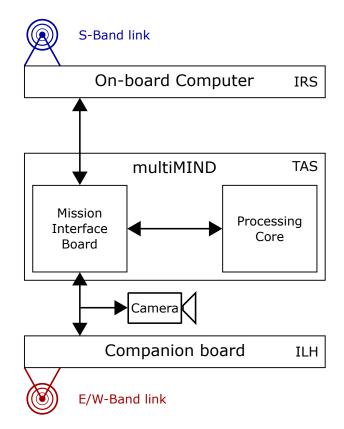

Radiation is emitted by sources, which are either galactic cosmic rays (GCR), solar particle events (SPE) or trapped particles. For a better understanding, these three categories along with their sphere of influence are schematically depicted in figure 2.1.

**Galactic cosmic rays** originate from outside the solar system and are typically found in free space [5]. GCRs consist of nucleus, travelling with nearly the speed of light. These nucleus are namely 85% protons, 14% helium nucleons and 1% highly charged ions (HZE particles), for instance highly charged carbon or iron ions [6]. The particle energies are below  $LET_{th} < 15 \,\text{MeV}\,\text{cm}^2\,\text{mg}^{-1}$  for protons, where  $LET_{th}$  is the minimum linear transferred energy to cause a particle flux of

Figure 2.1: Space radiation sources and their locations.

$1 \cdot 10^7$  ions cm<sup>-2</sup>. For larger particles, the linear energy transfer threshold is within the range of  $15 \,\text{MeV}\,\text{cm}^2\,\text{mg}^{-1} < LET_{th} < 100 \,\text{MeV}\,\text{cm}^2\,\text{mg}^{-1}$ , which makes it difficult to shield against such events [5]. Nevertheless, especially HZE particles are able to produce huge damages which can yield to problems in electronic components and diseases for humans [8]. Furthermore, the quantity of galactic cosmic rays varies with solar cycles in an inverted manner: During solar maximum, the period when more solar flares occur, less GCRs can be observed and vice versa [5], [6].

Another radiation source are **solar particle events**, which can be coronal mass ejections, where a billion tons of solar particles are blasted into space, or solar flares. The latter ones eject some protons and lots of heavy ions which have a comparable amount of energy to corresponding particles, emitted by GCRs [5]. Therefore, their impact to humans and electronic devices is similar to those of GCRs. However, since solar flares are temporal events, which are emitting particles, their particles can just be measured during short periods of time, ranging from a few hours to some days [8]. Apart from these short-term fluxes, the overall frequentness of SPEs depends strongly on the current solar cycle. Instead of occurring more frequently during solar minimum like GCRs, SPEs are more frequent during solar maximum and less frequent during solar minimum [5], [6]. Furthermore, their abundance is correlated with the distance to the sun and decreasing with higher removal from the sun [5].

As third member of space radiation sources, **trapped particles** are the least dangerous ones for missions in the lower earth orbit. They consist of protons and electrons at energy levels below  $LET_{th} < 15 \,\text{MeV}\,\text{cm}^2\,\text{mg}^{-1}$ , which are trapped by the earth magnetic field. These low-energy particles can mainly be observed in the inner Van Allen belts at altitudes between several hundred to approximately 6000 kilometres. At altitudes until 60000 kilometres, especially within the outer Van Allen belt, their energies can raise up to  $LET_{th} < 100 \,\text{MeV}\,\text{cm}^2\,\text{mg}^{-1}$ . Apart from the measured height, there is one cluster with high amounts of trapped particles above the southern Atlantic region, which is called the south Atlantic anomaly. In there, even low energetic particles at small altitudes can have impacts to electronic devices due to their quantity [5], [9].

Radiation, emitted by the three sources can be split up into two different groups. Even though they all emit electrons, protons, neutrons and ions, the origin of these particles can be entirely different. On the one hand, they can be sent out directly by a radiation source, which is then referred to as primary radiation. This case applies for galactic cosmic rays and solar particle events. On the other hand, primary radiation can hit some other matter and ionize it. Then, electrons are emitted as secondary radiation in succession. This secondary radiation yields to large radiation doses in electrical components and can be found in LEO [7], [8].

#### 2.1.2 Radiation Effects

Apart from their origins and particle energies, radiation can be characterized in terms of impacts, which can concern living organisms, human beings and electronic components. Effects on humans can be tissue damages and a higher risk to develop cancer [6]. But as the EIVE mission is not crewed, these effects are not further investigated. Nevertheless, impacts on electronic components are very important to consider and therefore specified in the remainder of this section. The investigation is mainly based on [5], [6], [7] and [10]. Wherever additional resources are referenced, they explicitly denoted.

In a first step, effects on electronic devices can be split up into two separate categories. The first one are cumulative effects, where long-term changes are considered. They can be observed as non-reversible degradation and long-term changes of device characteristics. Secondly, there are short-term effects caused by a single particle, called single-event effects (SEE). On the one hand, SEEs can be destructive an result in permanent damages of devices. On the other hand, SEEs can also be non-destructive, yielding from no effects at all, over bit errors in stored data until modification in operational procedures.

#### 2.1.2.1 Cumulative Effects

Both, single-event effects and cumulative effects, can be split into various subcategories. Cumulative effects are subdivided according to the amount of energy per particle. On the one hand, if the energy amount is high enough, it can take out electrons from matters' atoms and molecules. This process is called ionization, coming from ionizing radiation. The resulting effects are measured in terms of a total ionizing dose (TID) with the unit of radiation absorbed dose (1 rad). This is an amount of energy absorbed by a unit mass, defined as  $1 \text{ rad} = 0.01 \text{ Jkg}^{-1}$ . Typically, electronic components for radiation environments are designed to operate properly until a specified total ionizing dose. If the actual TID exceeds this specified value, the device is not guaranteed to work properly. Typical observed effects with rising TID are leakage currents in transistors, timing skews and threshold voltage shifts.

On the other hand, there is also non-ionizing radiation. It is not able to remove electrons due to its insufficient amount of energy. Non-ionizing radiation can be emitted from natural and ordinary sources like radio frequencies, visible light, infrared and UV-light. It is measured in terms of

total non-ionizing dose (TNID), also named displacement damage (DD), with the unit 1 rad. Nonionizing radiation can create electrical defects in semiconductors crystal lattice. This affects bipolar devices, but not CMOS devices like FPGAs or ASICs. Furthermore, it is easy to shield against.

### 2.1.2.2 Single-Event Effects

For single-event effects, there is a larger space for subdivision. First of all, SEEs can be grouped by their severity and secondly, they can be characterized by their impact. As shown in table 2.1, the severity can be either destructive for long-lasting or non-reversible effects, or non-destructive for errors, which can be repaired. Below, the different types of SEEs are described.

| Destructive                            | Non-destructive                          |  |  |  |  |

|----------------------------------------|------------------------------------------|--|--|--|--|

| Single-event latch-up (SEL)            | Single-event transient (SET)             |  |  |  |  |

| Single-event snap back (SESB)          | Single-event upset (SEU)                 |  |  |  |  |

| Single-event hard error (SEHE)         | Multiple-cell upset (MCU)                |  |  |  |  |

| Single-event burnout (SEB)             | Multiple-bit upset (MBU)                 |  |  |  |  |

| Single-event gate rupture (SEGR)       | Single-event functional interrupt (SEFI) |  |  |  |  |

| Single-event dielectric rupture (SEDR) |                                          |  |  |  |  |

Table 2.1: Subdivision of single-event effects

## **Destructive Single-Error Effects**

**Single-event latch-ups** are the most likely destructive single event effects for modern CMOS-based electronics. They occur when a single particle triggers a parasitic thyristor, which results in a high current flow and therefore, an increase in temperature. After some time, the device or some of its parts can be destroyed by the thermal effects. The only way to protect from SEL events is a power-reset of the circuit, before thermal damages can occur.

Very similar to SELs, **single-event snap backs** also yield to high current flows. They just differ by the underlying semiconductor structure: While SELs need parasitic thyristors to occur, a parasitic bipolar structure like PNP or NPN is mandatory for SESBs.

Apart from those parasitic structures in devices, radiation is also able to corrupt memories in nonreversible ways. In this case, charged particles affect the memory structure and damage one or more cells. Observed effects are stuck bits, whose values cannot be changed any more. Therefore, this type of radiation impact is called **single-event hard error**.

Another type of high current flow is called **single-event burnout**. It occurs when a power transistor is triggered, which yields to a high current flow and thus a thermal damage of components and devices. Fortunately, this effect is not common to FPGAs and ASICs.

Finally, there are **single-event gate ruptures** and **single-event dielectric ruptures**. For these events, a single particle strike ruptures a gate oxide or a dielectric layer, respectively. Thus, biases and leakage currents can be measured. For digital circuits, possible results are stuck bits. Up to now, there is no possibility to protect against such events, since they occur in a picosecond timescale.

Figure 2.2: Single-event transient and its effects

Figure 2.3: Single-event upset

#### **Non-Destructive Single-Error Effects**

Unlike destructive SEEs, non-destructive SEEs, also referred to as soft errors, don't have potential to destruct electronic devices, since non-destructive SEEs can just lead to flipped bits. Nevertheless, they are a concern in terms of device functionality and operational safety, depending on the kind of affected bits. Soft errors can have various impacts, which are briefly described below.

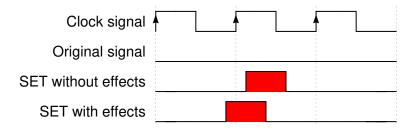

The first non-destructive SEEs are **single-event transients**, shown in figure 2.2. They are the most frequent type of SEEs in FPGAs, inferred by particles, hitting a connection wire at a combinatorial path between two registers. As an effect, a voltage spike on the hit line can be observed. Resulting effects in the circuit can be wrong data if the SET is captured by a memory, loosely speaking, then the SET becomes a SEU [11]. Other effects can be wrong signals or SEFIs, if the particle hits the clock distribution tree or a reset line. But it is also possible, that no effects will occur, especially when the voltage spike is not captured by a memory element [10].

SETs are not the only way to store wrong data, because particles can affect memories directly. These events are called **single-event upsets**. As shown in figure 2.3, SEUs induce single bit errors. They can have lots of effects, from wrong results in calculations to operational failures, depending on which memory is affected and the design of the circuit. Fortunately, they can be detected and corrected by error correction codes. Also, it is important to note that SEUs are more likely for small technologies and circuits with lower supply voltage, since they have smaller critical charges [11].

Furthermore, SEUs can appear multiple times in parallel. For most devices, the pattern, how bit errors are aligned, is essential. One possibility is to have multiple SEUs, but at maximum one per physical memory word. This type is called **multiple-cell upset**. As most error correction codes are able to correct one bit error per word, they could be completely recovered.

For multiple upsets in one word, namely **multiple-bit upsets**, it may not be possible to restore a fault-free state and the error may distribute across the device. Both of multiple upset effects are visualized in figure 2.4. With use of smaller technology, multiple upsets are becoming more likely. As a last type of soft errors, **single-event functional interrupts** are caused by the same effects than

Figure 2.4: Multiple-cell upsets and multiple-bit upsets

SETs. The key difference between them are the hit wires. While SETs allow any wires to be affected, SEFIs require particles to hit either the clock distribution tree or reset lines. Therefore, they can result in complete or partially resets of the circuit or violation of setup and hold times. SEFIs can be corrected by a reset of the whole device, either by software or by power cycling.

Since this thesis is only about mitigation of radiation effects in digital devices, table 2.2 briefly reviles which single-event effects can have influences to different devices. As there is clearly visible, just SELs, SESBs and SEHEs are possible destructive events for digital devices. SEBs, SEGRs and SEDRs can be completely ignored in the radiation mitigation process, as they will not occur. For non-destructive events, any devices with some kind of internal memory can be affected by upsets and most of them also by multiple upsets and functional interrupts. Furthermore, both computational parts, FPGAs and microprocessors, are sensitive to transient events as they have more internal connection lines, where particles may strike.

| Device category | Destructive |      |     |            | Non-destructive |     |         |      |  |

|-----------------|-------------|------|-----|------------|-----------------|-----|---------|------|--|

| Device category | SEL, SESB   | SEHE | SEB | SEGR, SEDR | SET             | SEU | MCU/MBU | SEFI |  |

| SDRAM           | X           | X    |     |            |                 | Х   | Х       |      |  |

| DRAM            | X           | X    |     |            |                 | X   | X       | X    |  |

| FPGA            | X           | X    |     |            | X               | X   | X       | X    |  |

| Flash EEPROM    | X           | X    |     |            |                 | X   |         | X    |  |

| Microprocessor  | X           |      |     |            | X               | X   | X       | X    |  |

Table 2.2: Summary of single-event effects and their presence on digital electronics.

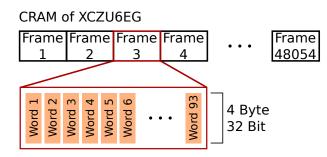

Finally, some general effects of soft errors in FPGA devices are discussed, as they are the most important for EIVE. As stated above, all soft errors may yield to flipped bits in storage elements, but the effects of them are not only dependent on their count. It is relevant, in which type of storage a bit is flipped. In general, FPGAs consist of five different kinds of memories, shown in table 2.3. If an error exists inside block memories, distributed memory or flip-flops, wrong data can be read by following hardware, which then can produce other wrong calculation results. As a result, this error does not change the device behaviour or circuitry. On the other hand, when

device control registers are affected, there may be impacts on the whole device, like thus, expected by a SEFI. In the remaining case, when an error is in the CRAM, the consequences are completely different. Since all internal routing and combinatorial output tables are stored in there, a bit error can possibly result in rerouted wires, altered functionality or failures in operation [12].

**Table 2.3:** Memory types in a FPGA and their sizes for the Xilinx UltraScale+ MPSoC XCZU6EG, used in EIVE mission.

| Name                        | Size (from [12], [13]) |

|-----------------------------|------------------------|

| Configuration memory (CRAM) | 17.0 Mb, 48054 frames  |

| Block memory (BRAM)         | 25.1 Mb, 714 blocks    |

| Distributed memory          | 6.9 Mb                 |

| Flip-Flops                  | 0.429 Mb               |

| Device control registers    | Few kb                 |

## 2.2 Analysis of the EIVE Radiation Environment

In this section, the radiation environment of EIVE is briefly summarized in order to provide facts about the planned mission. At the point this thesis was written, it was clear, that EIVE will be launched in the end of September 2022. Furthermore, the orbit was specified as LEO, with an altitude of 450 to 550 km [14]. For comparison purposes, it is worth mentioning that the International Space Station ISS circles around the earth at 400 km, which is about the same altitude [15]. In general, the low earth orbit is characterized by high-energy trapped protons, mainly created by effects of the South Atlantic anomaly. Because the earth magnetic field is able to shield from space radiation at these altitudes, high energetic particles from galactic cosmic rays or solar particle events play a minor role for EIVE [8].

For planning and implementing radiation mitigation strategies, it is mandatory to know, how often single events occur in the targeted orbit during the mission. This makes it possible to decide, which parts of a design must be protected in a certain way. Such statistics could be calculated with commercial tools like OMERE. In case of EIVE, these calculations were done by experts from TAS the IRS for single-event effects and for cumulative doses. Unfortunately, they are not quite up to date, because the launch date has been postponed.

In a first step, TAS' data for single-event effects, shown in table 2.4, is discussed. It is grouped into columns, depending on the type of events. Negligible soft-error types were removed by TAS. In summary, there will be 11.5 soft-error events per day, whereof 7 ones can be identified as latch-ups and 4.5 as upsets. However, EIVE's uptime is limited to ten minutes per day, due to power consumption limits. Since these soft-errors are able to damage devices, some kind of protection against them is mandatory. In terms of error effects, there is one event per day which may alter the MPSoCs functionality and the remaining 10.5 events can alter stored data. Therefore, protection of important, mission-specific data is essential [14], [16].

Apart from single-event effects, total radiation doses are very important in order to choose electric

| 0 1                | 1                                |

|--------------------|----------------------------------|

| Single-event upset | Single-event latch-up            |

| 0.04               | N/A                              |

| 0.02               | N/A                              |

| 0.0003             | N/A                              |

| 0.0603             | 1                                |

| 0.5                | 0.0003                           |

| 4                  | 6                                |

| [                  | 0.04<br>0.02<br>0.0003<br>0.0603 |

Table 2.4: Number of single-event error expected for EIVE in events per day.

components in such a way, that they will outlive the missions duration. The results of this calculation is evinces in table 2.5. Briefly worded, for a satellite, launched in quarter two in 2022 into an orbit between 490 to 520 km altitude and a mission duration of one year, electric devices must be radiation tolerant up to a total radiation exposure of 12.6 krad or 5.2 krad, when shielded by 1 mm or 2 mm aluminium, respectively [14].

**Table 2.5:** Total ionizing doses expected for EIVE with start in Q2 2022 and sun-synchronous orbitat 490 to 520 km altitude, calculated with the OMERE tool.

| Shielding      | Mission duration | Radiation exposure |

|----------------|------------------|--------------------|

| 1 mm aluminium | 1 year           | 12.6 krad          |

| 2 mm aluminium | 1 year           | 5.2 krad           |

# 2.3 Mitigation Approaches

One more general example to underline the need for radiation mitigation is based on metrics, called failure in time (FIT) and mean time between failures (MTBF). FIT is defined by the counted number of failures occurring in a time interval of  $1 \cdot 10^9$  hours and MTBF is the average time, in which one failure is expected. As an example, a part may have a FIT rate of 600 at sea level and 370000 at an altitude of 12 km. Thus, the MTBF can be calculated by  $MTBF = \frac{1e9years}{numberof failures}$  as 190 years and 0.31 years, respectively [17]. Since EIVE is orbiting the earth at significant higher altitudes, the FIT can be expected even higher and therefore, the MTBF will decrease. In order to complete the EIVE mission successfully, failures during the mission must be reduced by implementing appropriate radiation mitigation techniques at a suitable level, described in this section.

## 2.3.1 Available Techniques

In order to ease the discussion about the integration of radiation mitigation techniques, the most popular radiation mitigation techniques are described in this section. Therefore, mitigation methods are summarized in table 2.6 in advance, before they are described in the remainder of this section. All investigated techniques are limited to the scope of digital electronics, which means that mitigation techniques for analogue or mixed-signal circuits are skipped.

| Table 2.0. Summary of available faulation |                    |     | Radiation effects |     |     |     |  |

|-------------------------------------------|--------------------|-----|-------------------|-----|-----|-----|--|

| Name                                      | Protected elements | SET | SEU               | MBU | MCU | SEL |  |

| Information redundancy                    |                    |     |                   |     |     |     |  |

| Error correction codes                    | Memory, SoC        |     | X                 |     |     |     |  |

| Error detection codes                     | SoC                |     | X                 |     |     |     |  |

| Spatial redundancy                        |                    |     |                   |     |     |     |  |

| Duplex architectures                      | DCs, FPGA          | X   |                   |     |     |     |  |

| Triple modular redundancy (TMR)           | DCs, SoC, FPGA     | X   | X                 |     |     |     |  |

| Lockstep                                  | System             | X   | X                 |     |     |     |  |

| Reliability-oriented place and route      | FPGA               | X   | X                 |     |     |     |  |

| Temporal redundancy                       |                    |     |                   |     |     |     |  |

| Triple temporal redundancy                | Digital circuits   | X   | X                 |     |     |     |  |

| Minimal level sensitive latch             | Digital circuits   | X   | X                 |     |     |     |  |

| Redundancy in software                    | Software           | X   | X                 | X   | X   |     |  |

| No redundancy                             |                    |     |                   |     |     |     |  |

| Use of radiation hardened parts           | Memory             |     | X                 |     |     |     |  |

| Bit interleaving                          | Memory             |     |                   | Х   |     |     |  |

| Memory Scrubbing                          | Memory, FPGA       |     | X                 | Х   |     |     |  |

| Hardened finite state machines            | Digital circuits   |     | X                 |     |     |     |  |

| Selective use of resources                | Digital circuits   | X   | X                 |     |     |     |  |

| Watchdog timers                           | SoC                | X   | X                 |     |     |     |  |

| SET filtering in data path                | SoC                | X   |                   |     |     |     |  |

| Partial reconfiguration                   | FPGA               |     | X                 |     |     |     |  |

| Shielding                                 | System             | X   | X                 |     |     | X   |  |

| Power cycling                             | System             |     | X                 |     |     | X   |  |

| Current monitoring                        | System             | X   |                   |     |     | X   |  |

Table 2.6: Summary of available radiation mitigation techniques.

## 2.3.1.1 Embedded Memories

As a basic element, almost any digital circuit contains embedded memories to store data. Hence, a protection mechanism for memories can improve the radiation tolerance for a wide range of electronic systems. In general, each memory device, as shown in figure 2.5, consists of memory blocks, which are built out of base units, named memory cells. Each cell is made up of basic electric components and has the ability to store one bit of information. When a cell is irradiated, the stored bit could flip and change its value from 0 into 1 or vice-versa. Therefore, the most effective way in terms of radiation resistance is to harden each single cell. This could be done by adding resistors or capacitances in a way to increase the critical charge. The drawbacks of this approach are penalties in used area and speed [7].

Another way to harden cells is to add extra transistors, such that each cell can restore itself if the data is corrupted. Due to the extra transistors, the drawbacks of this approach are an power- and area overhead, which varies with the used cell topology. However, in most cells, the overhead in power consumption is negligible compared to standard COTS-cells [7].

Beside protecting each cell, there are advantages of protecting memories at a block basis. In general,

Figure 2.5: Schematic structure of a memory device.

Figure 2.6: SEEs in memory with and without bit interleaving.

block protection is cheaper in production and has the ability to operate on more than one bit of data. Thus, the concepts of error correction codes (ECC) and bit interleaving can be applied either in hardware or software. Error correction codes add redundant data to original information in a way, that correction and detection of a specified amount of bit errors is possible. ECC have the disadvantage of overhead in used memory and computation time, because the redundant bits must be calculated and checked at each time, when a write or read operation is performed. For bit interleaving, shown in figure 2.6, the property of locality of radiation strikes is used: Because cells are small enough, a single radiation strike will likely affect more than one of them. Since adjacent data mostly belongs to a single data word, the injected particles will have large impacts to small numbers of words. Especially when error correction codes are used, many bit errors in a few words are worse than single bit errors in many words, because they can yield to MBUs. Therefore, bit interleaving can be used to distribute originally adjacent data across the device to make neighbouring cells containing data of different words. The only downside of bit interleaving is an increase in access time, because different memory regions must be activated in order to read previously cohesive data [7], [18].

The last approach to protect memory cells is called data scrubbing, which periodically rewrites cor-

rupted memory bits with bits from a golden data location. Scrubbing prevents from accumulation of erroneous bits and ensures that error correction codes are working properly. As disadvantage, a secondary memory is needed to store the golden data. The pitfall is, that the golden data must be stored on a much more radiation hardened memory device. Otherwise, the golden data can also contain errors and wrong data is scrubbed into the used storage element [7], [18].

#### 2.3.1.2 Digital circuits

In this section, radiation mitigation techniques, related to digital circuits, are investigated. Because the underlying semiconductor technology is already chosen, all mentioned techniques cannot mitigate permanent errors, caused by the total ionizing dose. However, almost all of the mitigation techniques are capable to weaken the effects, caused by transients and upsets. To keep it tidy, the mitigation methods are grouped in terms of redundancy. Firstly, duplex architectures and triple modular redundancy (TMR) are belonging to spatial redundancy, i. e. processing the same task multiple times in parallel and comparing the results by a voting circuitry. Secondly, the group of temporal redundancy contains triple temporal redundancy and minimal level sensitive latch approaches. Temporal redundancy is characterized by multiple processing operations, which are executed at different points in time, but not in parallel. As known from spatial approaches, temporal redundancy also requires voting logic in order to detect and correct wrong results. The third group is different, because no redundancy is necessary. Therefore, this last group contains general designing guidelines to design radiation hardened digital circuits.

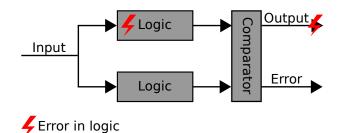

**Duplex architectures** architectures consist of two identical logic blocks and one comparator. As depicted in figure 2.7, the input data is split up into two separate paths, such that the bottom and the top module will receive the same data. When both redundant modules are done with their processing tasks, both results are forwarded to a comparing logic. In the comparator, one of its input lines is directly connected to the data output signal and the error signal will be set to an error state, if a mismatch between both input ports is detected. When a mismatch is detected, no assertion about the correctness of the output signal can be made, since either input one or input two can be erroneous. Therefore, a reprocessing with the same input data is required to get a valid result. Apart from weak error correction capabilities, duplex architectures are characterized by doubling the used area and thus the power consumption. Furthermore, meeting timing requirements can be difficult, because the total number of recomputation is not determined.

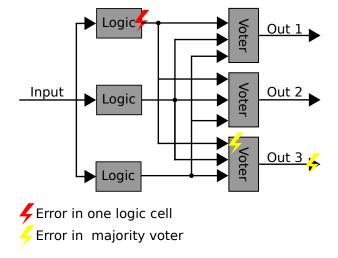

**Triple modular redundancy** can be seen as an extension of duplex architectures. Instead of two identical logic blocks, TMR uses three copies of logic. Therefore, the comparator needs to change into a majority voter. This means, if one of the three voter input signals is changed, the other two ones will likely remain the same and are therefore valid. The only remaining context to perform a recomputation is denoted by three disjoint voter inputs. Nevertheless, the voter is a single point of failure and the output data will be wrong, if the voting logic is affected by radiation. With the

Figure 2.7: Schematic structure of a duplex architecture with comparator.

Figure 2.8: Schematic structure of a full TMR architecture with voter and different errors.

additional triplication of the voter, a basic TMR is transformed into a full TMR with three voters and the single point of failure is removed. When using full TMR, single event effects can now occur on computational logic, connection signals and voters, as depicted in figure 2.8. Apart from strong error detection and correction capabilities, both kinds of TMR come with an area overhead of factor three and a comparable overhead in power consumption.

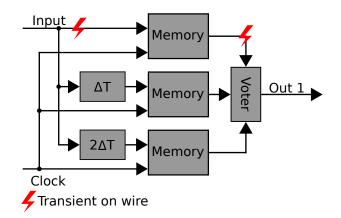

**Triple temporal redundancy** (TTR) is efficient to filter out transient effects from signal lines. Since transients are short voltage spikes on connection lines, this is done by sampling the processing blocks output signals at different time instances and storing them into flip-flops. As a final step, the flip-flops' values are compared by a majority voter to determine the correct values. A schematic TTR is given in figure 2.9. On the one hand, TTR needs significantly less space and therefore, the power consumption is reduced, when compared to duplex architectures or TMR. On the other hand, flipped bits during data processing cannot be identified.

**Minimal level sensitive latch** (MLSL) is another technique of temporal redundancy. It consists of the same ports as TTR-blocks, but MLSL uses latches to store sampled signal data instead of flip-flops. Unlikely, an instantiation of latches is harder than an instantiation of flip-flops. Therefore, MLSL is less often used. In summary, MLSLs have the same space usage and power consumption

Figure 2.9: Schematic structure of a TTR architecture with delay elements, memories and voter.

than triple temporal redundancy.

**Radiation hardened finite state machines** are ordinary finite state machines (FSM) with more carefully designed properties. As a first property, state variables are designed in a way, which prevents accidentally state changes as result of a single flipped bit. The second property makes sure, that no illegal states can be reached from a valid state, or at least, illegal states will transition to a valid safe state immediately. Often, synthesis tools can fulfil both of this properties automatically. When lots of upset events are expected, for example when operating the circuit in interplanetary space, state coding with additional error correction codes can be considered to maintain the FSMs functionality. The downsides of radiation hardened FSMs are slightly more consumption of power and a small overhead in area.

**Selective use of resources** deals with different types of hardware, used for different tasks. For instance, some cells or wires in a digital circuit can be more hardened and should therefore be used for tasks with high reliabilities. More hardened resources could be cells with higher drive strength, radiation hardened flip-flops or memories, cells synchronous reset and set signals or cells with larger transistors. The drawbacks of this technique are dependent on the used cells, but it tends to have an overhead in area and power consumption.

## 2.3.1.3 System on a Chip

A System on a Chip (SoC) consists of many parts, placed on a single silicon chip. Thus, they can contain small elements like logic gates, medium sized elements like transceivers and large elements like processors. Since all parts together form a complex system, error mitigation techniques can also be applied in SoCs. Two possible techniques are already known from preceding sections. The first one is error correction coding, briefly described in section 2.3.1.1 and more precisely investigated in chapter 5. In contrast to error correction codes in memory, ECCs can now be applied to interconnection wires between parts. The second one is called triple modular redundancy, known

from section 2.3.1.2. From a SoCs' perspective, TMR is applied in larger scales, namely at part level. Because SoCs are at a higher abstraction levels than digital circuits, two new concepts are made possible. These are watchdog timers and filtering of single-event transients.

**Watchdog timers** are external or internal timers, which are used to indicate liveness of whole system or single parts. Once the timer is started, the task for the observed system is to reset the timer before it expires. As long as the timer is running, the system or part is assumed to be alive. On the other side, if the timer is expired, an error inside the system or part is assumed. In the latter case, the watchdog timer will either perform a hard reset on the affected circuitry, or it will raise error signals in a way, that other external or internal resets can be performed. The only disadvantage is a small area overhead for the watchdog circuitry.

**SET filtering** is a set of three techniques to break long transient propagation paths. While all three techniques can be found in any digital design, they are worth investigating further. The first technique is called logic masking. There, transient effects are filtered out by logical gates. For instance, an and-gate's output will always be low if one input is low. In this case, the second input can change between low and high arbitrarily or transients can occur there, but the output signal will not change. The other way around, for or-gates, the output will always stay high if one input is high. The second technique is called electrical masking. It is based on the transients attenuation, as it passes through electrical gates. If the electrical path is long enough, SETs will decrease in voltage amplitude until the voltage is too low to change the digital electric level. The third technique is temporal masking, which deals with sample intervals of flip-flops: Whenever a transient is at a flip-flops' input during a sensitive edge, it will be captured. The other way around, when a SET affects the input data wire of a flip-flop outside of the capturing interval, the inputs value will not be stored. Therefore, the transients has no effect.

#### 2.3.1.4 Field Programmable Gate Arrays

Field programmable gate arrays (FPGAs) are chips, containing configurable logic. They are built from configurable logic blocks (CLBs), which consist of lookup tables and flip-flops, external pins, internal wires, routing blocks for internal connections and hard-wired components like processors or cells for digital signal processing (DSP). FPGAs are available in three different variants: Anti-fuse, flash-based and SRAM-based. In anti-fuse-FPGAs, the programmed logic and routing information is stored within anti-fuse cells. These are cells with initially high resistance, where electrically conductive paths are created during configuration. Whilst anti-fuse-FPGAs are highly radiation tolerant, since their configuration is not stored in a memory, they can only be configured once. On the other side, flash-based FPGAs store their configuration inside a non-volatile flash memory. Therefore, the FPGA starts its tasks whenever it is connected to a power supply. Although flash-based FPGAs are reprogrammable, they have less configuration cycles than SRAM-based FPGAs, which are the third variant. As the name suggests, SRAM-based FPGAs store their configuration in a volatile SRAM-memory. While SRAM-FPGAs can be configured almost an infinite number of times, they need to be reconfigured anytime they receive power. Thus, a secondary memory is mandatory in order to provide the configuration bitstream. Because nowadays, almost all FPGAs are SRAM-based, the term FPGA will refer to those SRAM-based FPGAs in the remainder of this thesis [10].

The main concerns of radiation strikes hitting an FPGA are injuries of the configuration memory (CRAM). Because the CRAM contains all information about cell functionalities and routing resources, a flipped bit in there is potentially able to affect the functionality. On the one hand, malfunctions can occur when wires are rerouted or cut and thus, logic blocks are not connected any more or electric shorts are created. On the other hand, the functionality can be affected if bits of lookup tables are flipped. The latter case results in wrong calculation results. Therefore, reliable mitigation techniques are needed to protect FPGAs [10].

**CRAM protection** can be achieved in three different ways. Since CRAM is equivalent to any other memory devices in terms of radiation protection, memory scrubbing can be applied. This protects the configuration memory from accumulation of errors. A slightly different approach of CRAM scrubbing is called partial reconfiguration. The main purpose of partial reconfiguration is to exchange parts of the devices functionality during operation. Therefore, some tasks can be done faster or with less power consumption. However, partial configuration can also be seen as an approach of partial CRAM scrubbing. Compared to complete scrubbing approaches, where the whole memory is scrubbed, partial reconfiguration has the same effects within a defined CRAM region. The third approach to protect the configuration memory are ECC codes. Error correction codes can be used to correct single or multiple bit errors. In order to improve their efficiency, bit interleaving becomes reasonable.

**Spatial redundancy,** especially triple modular redundancy, is also a popular radiation mitigation technique when protecting FPGAs. TMR can be applied at different granularities. On small scales, flip-flops can be triplicated and their output signals can be voted locally. This prevents wrong data at the input of combinatorial paths and thus wrong calculation results. However, local TMR can just mitigate upset events in flip-flops, no transient errors in combinatorics. At a global scale, TMR can triplicate the functionality, including pins, reset lines and clock distribution trees. Since pins are also triplicated, an external voter is needed. The disadvantage of global TMR is, that replicas of internal logic are not placed into distinct areas of the FPGA.

The reliability oriented place and route algorithm (RoRA) can be used to fill the gap of global TMR. RoRA routes the replicas of configured logic into distinct areas of the chip with no interconnections, except for the input signals. Thus, radiation strikes are only able to impact one out of three logic structures. As a result, the external voter is always able to find a majority. Another advantage of RoRA is, that the algorithm prefers short connection wires, because they are less likely to be affected by transient effects. As the only disadvantage, the constraint of distinct area

| Original Instructions |               |               |  |  |  |

|-----------------------|---------------|---------------|--|--|--|

| Instruction 1         |               |               |  |  |  |

| Instruction 2         | <b>~</b>      |               |  |  |  |

| • • •                 |               |               |  |  |  |

| Instruction N         | -             |               |  |  |  |

| Instruction Red       | dundancy      |               |  |  |  |

|                       |               | ••• Compare 1 |  |  |  |

| Instruction 2         | Instruction 2 | ••• Compare 2 |  |  |  |

| • • •                 | • • •         | • • •         |  |  |  |

| Instruction N         | Instruction N | ••• Compare 3 |  |  |  |

Figure 2.10: Schematic structure of instruction-level redundancy.

prevents the routing algorithm from optimum routing. Thus, the overall performance is reduced [19].

## 2.3.1.5 Software

Apart from hardware-based radiation mitigation approaches, software can also be designed in a radiation tolerant way. In all cases, software-based techniques are using temporal redundancy as a basis. In general, three approaches are possible, based on the abstraction level.

**Instruction redundancy** is at the lowest abstraction level. As shown in figure 2.10, any instruction is executed multiple times in sequence, but each instruction execution has its own distinct set of variables. Thereafter, all results are compared by a majority voter. Apart from a massive overhead in computation time and RAM usage, instruction redundancy is not transparent for software developers. During software development, the programmer is in charge of caring about data copies and multiplication of instructions. Furthermore, this approach is not applicable when interrupts are used, because an interrupt service routine is just called once. On the other side, instruction redundancy has nearly 100 % coverage for data and execution flow faults.

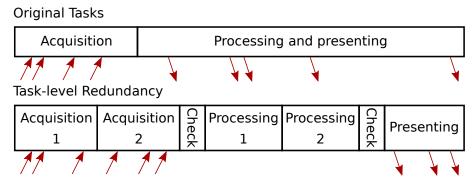

**Task-level redundancy** works on a higher abstraction level. Instead of re-executing each instruction separately, tasks are split up into three execution stages and consistency checks, during software design. As seen in figure 2.11, each task starts with data acquisition, where input data is collected (red incoming arrows). Afterwards, computations are separated into a data processing stage. Finally, during data presentation, computation results are emitted to other tasks, depicted by red outgoing arrows. In order to check for errors, data consistency checks are applied after acquisition and processing of data. The error detection and correction rate of task-level redundancy is, as for instruction redundancy, nearly 100%. However, drawbacks are impairments in system architecture design, compatibility issues with available libraries and loss of performance.

**Figure 2.11:** Task-level redundancy by separating tasks into three execution stages and performing consistency checks.

**Redundancy at application level** uses the concept of hypervisors, which are also used for virtual machines on personal computers. By using hypervisors, a whole application can be executed multiple times in parallel. The functionality of application is ensured by watchdogs and monitoring of memory interfaces. Application-level redundancy is therefore completely transparent for software engineers, but the error detection and correction capabilities are below 100%. As for all software-based approaches, hypervisor-based techniques have high overheads in computation time.

## 2.3.1.6 System Protection

In contrast to software- or hardware-based radiation mitigation techniques, there are also strategies on system architectural level. System-based mitigation techniques can contain redundancy approaches, internal or external supervisions, or physical protection from radiation. For redundancy approaches, duplex architectures, TMRs, temporal- and software-bases redundancies and mixtures of them are possible. Supervisions can be realized as watchdogs at system or component level or by placing current monitoring circuits.

**Shielding** is the most simple technique. It can not only protect electronic components from latch-ups, transients and upsets, but also improve their lifetime by increasing the total ionizing dose. Suitable materials are aluminium or hydrogenous materials for light shielding and tungsten for heavy shielding. Their use and thickness are highly dependent on the expected radiation environment. If more radiation is expected, mainly materials for heavy shielding will be used with an increase in thickness. On the other hand, for less irradiated environments, a thin aluminium layer can be used. Apart from putting the whole system into a shielded box, more vulnerable components can have extra shields. In any case, an increase in weight can be denoted as the only disadvantage [14].

**Watchdog timers,** as known from 2.3.1.3, can also be used on system level. Additionally, the entire system or system parts can be power cycled, when a corresponding watchdog timer exceeds.

**Power cycling** has the ability to remove malfunctions, induced by single-event effects by withdrawing the power sources. At the moment, when power lines are cut, all volatile memories will be erased.When turning the power back on, the system is restarted in a defined initial state. In case of FPGAs, power cycling yields to erasure of the CRAM, and therefore, the logic must be reconfigured.

**Current monitoring** is used to protect from latch-up events. When single-event latch-ups are induced into a circuit, high current flows occur. High currents need to be mitigated, since they yield to thermal effects, which can destroy the device. As high current flows can be detected by current monitoring circuits, mitigation can be done by immediately removing all power supplies [3].

**Lockstep architectures** are a special kind of software redundancy, which is applied at system level. As advantages, all software-based faults are detected without constraints on software design. Thus, software needs no modification and usage of third-party libraries and interrupts is possible. Instead, the error detection is based on a second processor, called backup processor, and a consistency checker. Each processor has read access to the memory and runs the same software, but just the main CPU is allowed to write data. Thus, the consistency check will compare memory addresses and data at both memory buses. The disadvantages of lockstep architectures are area and power overhead of one CPU and one checker and a small overhead in processing time.

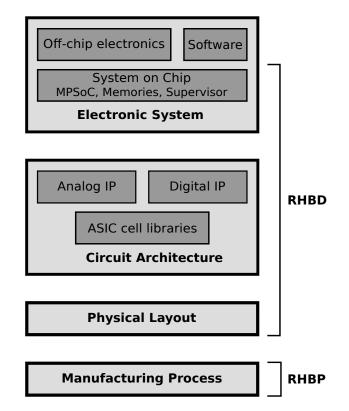

## 2.3.2 Possible Levels for Radiation Mitigation

A newly created system goes through several stages of development and production, before it can fulfil its desired purpose. During this development and production process, radiation mitigation techniques can be applied at almost all stages. In figure 2.12, these stages are denoted together with more specific resources for these stages and an overall radiation hardening manner. The latter one can either be radiation hardening by process (RHBP), where special techniques are applied at manufacturing process level, or radiation hardening by design (RHBD), where other techniques are used during the design process [7], [18].

During manufacturing process, radiation can be mitigated by selection of process parameters. This includes modifications of doping profiles, usage of specific materials and optimization of deposition processes. Changes of the manufacturing process refereed to the RHBP group.

At the lowest level of electronics design, the physical layout level, radiation hardening can be achieved in two ways. On the one hand, the physical layout of transistors can be changed in order to mitigate selected effects. On the other hand, the transistor's placement can be changed to reduce radiation sensitivity. For instance, less transient events will be observed, as the total wire length becomes smaller. Since physical layout is optimized during circuit designing, layout optimization belongs to the group of RHBD [7].

Figure 2.12: Overview of stages, where radiation mitigation is possible.

One level higher, at the circuit architecture level, radiation mitigation techniques are specific to the circuits nature or family. The nature can be either digital, analogue or mixed signal, while ASIC, FPGA and memory are values for the family property. At the architecture level, intellectual property (IP) is used to ease the design process. The majority of mitigation approaches for the architecture level make use of error detection and correction (EDAC) and redundancy [7].

The electronic system level is the highest level, where radiation mitigation can take place. Mitigation techniques for electronic systems are mostly applied at component level, unit level or software level. Even across multiple chips, radiation mitigation techniques can be applied. Most approaches at the electronic system level are based on spatial redundancy. It is also possible to apply current monitors, power cycling and watchdog timers.

# **3** Selected Radiation Mitigation Techniques for the EIVE Project

The EIVE mission has specific requirements towards radiation tolerance, leading to mission-specific constraints. These requirements and constraints are investigated in this chapter. Thereafter, known radiation mitigation techniques from section 2.3 are assessed due to those requirements and constraints.

# 3.1 Mission Requirements

The operational duration for satellites is mainly governed by battery recharging cycles and radiation effects. Especially the total ionizing dose limits the total lifetime, because unrecoverable effects are induced by the TID. Furthermore, since batteries will slowly use their capacity and in some cases their functionality, they also have an impact on EIVE's lifetime. By regarding both limitations, EIVE is designed to be operative for one year in LEO and will hopefully operate for a longer time. In any case, the EIVE PLOC shall remain operative at least during the planned satellite lifetime of one year.

Because received data will be compared to known sent data, the correctness of downlink sample data and accurate functionality of the payload computer must be guaranteed. For the case, that incorrect data is sent through E/W-band link, a comparison to original data on ground will not be meaningful. Therefore, error correction and indication of data corruption is required for EIVE. Due to this argument and additional possible destruction of electronic devices, the case of inaccurate functionality must be completely avoided. Therefore, an error-free operation during uptime is desired.

Another functional requirement deals with single-event error observation. All errors in the MPSoC, induced by SEEs, should be logged into the housekeeping report and written to a file in the eMMC-memory. This requirement is proposed by TAS, because the multiMIND-platform in the satellite was recently developed and therefore, no in-space radiation data is available. Thus, error logging will enable product improvements and can additionally be evaluated to regard transmission errors.

# 3.2 Mission Constraints

Beside mission requirements, constraints must be fulfilled, when contributing to the EIVE payload computer. These constraints are divided up into three groups. The first group contains global constraints, which are important for any contributor. Secondly, there are constraints for radiation mitigation techniques, which are important for developers of the radiation subsystem. The third group contains MPSoC-specific constraints.

# 3.2.1 Global Constraints

The first global constraint deals with lifetime. As EIVE is designed to operate for one year, no missions tasks at later points in time can be reliably scheduled. Loosely spoken, any component may have been damaged after this duration. Of course, if EIVE is still able to operate, it can perform tasks after the expected lifetime.

Secondly, mission and system planning need to take care of the overall power budget. Since one battery charge is needed to perform one E/W-band transmission, other tasks during the same time are very limited in terms of power consumption. Therefore, it must be carefully considered, which tasks are necessary during an E/W-band downlink. Power characteristics are briefly summarized in table 3.1.

| 1                                   | 1 )                                                                                                                 |

|-------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Available power                     | Source                                                                                                              |

| 6.4 W (0.8 W static, 5.6 W dynamic) | Xilinx power report                                                                                                 |

| approximately 5 W                   | Measurements                                                                                                        |

| approximately 10 W                  | Measurements                                                                                                        |

| 19.1 W at –20 °C, 22.5 W at 50 °C   | Measurements                                                                                                        |

| 25 W                                | Fixed by IRS                                                                                                        |

|                                     | 6.4 W (0.8 W static, 5.6 W dynamic)<br>approximately 5 W<br>approximately 10 W<br>19.1 W at -20 °C, 22.5 W at 50 °C |

Table 3.1: Available and consumed power in the EIVE project.