#### Institut für Parallele und Verteilte Systeme

Universität Stuttgart Universitätsstraße 38 D-70569 Stuttgart

#### Bachelorarbeit

## Lösen riesiger linearer Gleichungssysteme mit einer Multi-GPU beschleunigten CG-Implementierung

Paul Arlt

**Studiengang:** Informatik

Prüfer/in: Prof. Dr. rer. nat. Dirk Pflüger

**Betreuer/in:** M.Sc. Marcel Breyer

Beginn am: 1. Dezember 2022

Beendet am: 1. Juni 2023

### Kurzfassung

Das Lösen von linearen Gleichungssystemen (LGS) ist ein zentrales Problem, dass es bei wissenschaftlichen Simulationen zu berechnen gilt. Zum Lösen von LGS mit positiv, symmetrischer Koeffizientenmatrix wird häufig das Verfahren der konjugierten Gradienten (engl. Conjugate Gradient (CG)) verwendet. Moderne Systeme, auf denen wissenschaftliche Simulationen durchgeführt werden, machen häufig sich die überlegene Rechenleistung von Grafikkarten zunutze. So sollte das Conjugate Gradient (CG)-Verfahren ebenfalls auf Grafikkarten gerechnet werden.

Ein weiterer Trend der heutigen Zeit ist, dass wissenschaftlicher Simulationen immer größer werden, sodass die zu lösenden LGS ebenfalls an Größe zunehmen. So reicht für große LGS der Speicher von Grafikkarten nicht mehr aus, um alle relevanten Daten zum Lösen des LGS im Speicher zu halten. Die daraus resultierenden regelmäßigen Kopiervorgänge von Daten auf die Grafikkarte verlangsamen die Berechnung erheblich. Mehrere Grafikkarten, mit ihrem kombinierten Speicher können diesem Problem entgegenwirken.

In dieser Arbeit wird das CG-Verfahren für mehrere Grafikkarten implementiert. Die Berechnungen des CG-Verfahrens werden in der Implementierung auf alle Grafikkarten verteilt. So kann die kombinierten Rechenleistung, zusätzlich zur erhöhten Speicherkapazität genutzt werden kann.

Dadurch ist das Rechnen auf mehreren Grafikkarten erheblich schneller als das Rechnen auf nur einer Grafikkarte. Im Extremfall ist die Laufzeit beim Rechnen auf vier NVIDIA A100-SXM4 über 100-mal geringer als die Laufzeit beim rechnen auf einer NVIDIA A100-SXM4. Beim Rechnen auf einer NVIDIA GTX 1080 Ti ist die Laufzeit im Extremfall über 50-mal größer, als beim Rechnen auf acht NVIDIA GTX 1080 Ti.

## Inhaltsverzeichnis

| 1 | Einl                            | eitung                                                                                                                                                                                                                                                                                                                                                                            | 17                                                                         |

|---|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| 2 | Verv                            | vandte Arbeiten                                                                                                                                                                                                                                                                                                                                                                   | 19                                                                         |

| 3 | <b>Verf</b> 3.1 3.2             | ahren der konjugierten Gradienten  Die Vorgehensweise des CG-Verfahrens                                                                                                                                                                                                                                                                                                           |                                                                            |

| 4 | 4.1<br>4.2<br>4.3<br>4.4        | CUDA-Grundlagen 4.1.1 Kernels 4.1.2 Hardwareumsetzung 4.1.3 Aufruf von Kernels 4.1.4 Speicherhierarchie Asynchrone Operationen Registrierter Speicher Multiple Grafikkarten                                                                                                                                                                                                       | 27<br>27<br>29<br>29<br>31<br>32<br>34<br>34                               |

| 5 | 5.1<br>5.2<br>5.3<br>5.4<br>5.5 | Allgemeine CG-Struktur Sequenzielle Implementierung Mehrkernprozessor Implementierung CPU-Implementierung mit Speicherbegrenzung GPU-Implementierung 5.5.1 Speichereinteilung des VRAM 5.5.2 Matrix-Vektor-Multiplikation 5.5.3 Vektor-Vektor-Operationen Multi-GPU-Implementierung 5.6.1 Matrix-Vektor-Multiplikation 5.6.2 Vektor-Vektor-Operationen Generierung der Datensätze | 37<br>37<br>39<br>40<br>41<br>42<br>43<br>44<br>48<br>51<br>51<br>53<br>53 |

| 6 | 6.1                             | ebnisse  Verwendete Hardware  Verwendete Compiler                                                                                                                                                                                                                                                                                                                                 |                                                                            |

| Lit | iteraturverzeichnis 73 |         |                                                                  |    |  |

|-----|------------------------|---------|------------------------------------------------------------------|----|--|

| 7   | Fazi                   | t und A | Ausblick                                                         | 71 |  |

|     |                        | 6.4.4   | Erreichte Leistung                                               | 68 |  |

|     |                        | 6.4.3   | Multi-GPU-Implementierung                                        |    |  |

|     |                        | 6.4.2   | Einzel-GPU-Implementierung                                       | 65 |  |

|     |                        | 6.4.1   | CPU-Implementierungen                                            | 62 |  |

|     | 6.4                    | Laufze  | eiten einer Iteration                                            | 62 |  |

|     |                        | 6.3.2   | Ermittlung der Thread-Block-Größen der GPU-Implementierungen     | 61 |  |

|     |                        | 6.3.1   | Ermittlung der Blockgrößen der sequenziellen CPU-Implementierung | 59 |  |

|     | 6.3                    | Versuc  | chsaufbau                                                        | 59 |  |

# Abbildungsverzeichnis

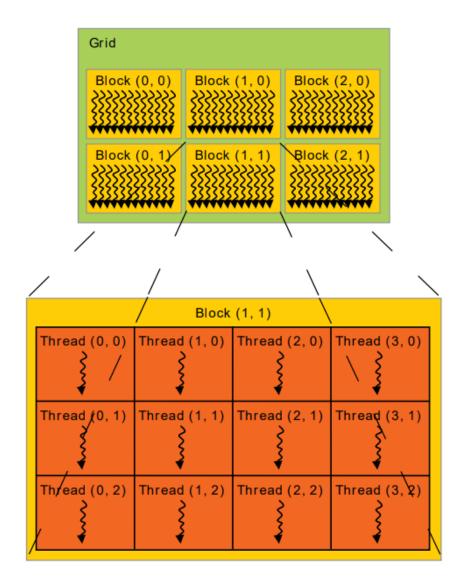

| <ul><li>4.1</li><li>4.2</li></ul> | Hierarchische Struktur von Threads in CUDA Quelle: CUDA Programming Guide [NVI23], Kapitel 2.2                                                                                                                             | 28<br>34   |

|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

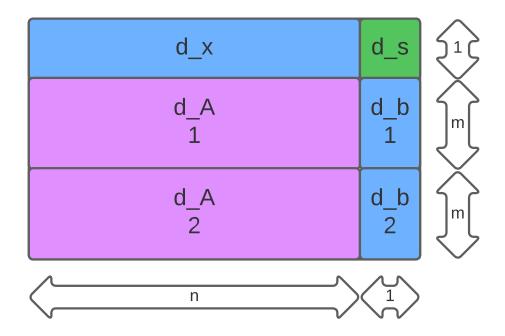

| 5.1                               | Speichereinteilung des VRAM einer Grafikkarte                                                                                                                                                                              | 43         |

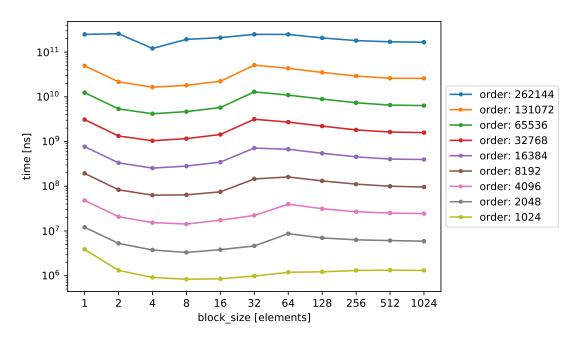

| 6.1                               | Laufzeit einer Iteration der sequenziellen CPU-Implementierung in Abhängigkeit der Blockgröße, für verschiedene LGS-Ordnungen gerechnet mit dual-Socket Intel Xeon Gold 5120 Die optimale Blockgröße für große LGS beträgt |            |

|                                   | vier                                                                                                                                                                                                                       | 60         |

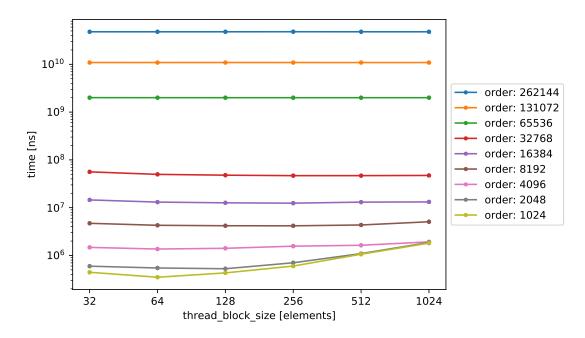

| 6.2                               | Laufzeit einer Iteration der GPU-Implementierung, in Abhängigkeit der Thread-Block-Größe, für unterschiedliche LGS-Größen Gerechnet mit einer NVIDIA GTX 1080 Ti 11GB Zu große Thread-Block-Größen hemmen die Aus-         |            |

|                                   | führungsgeschwindigkeit des Kernels                                                                                                                                                                                        | 62         |

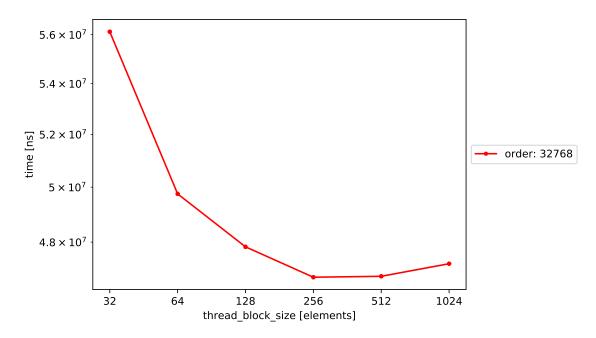

| 6.3                               | Laufzeit einer Iteration der GPU-Implementierung, in Abhängigkeit der Thread-Block-Größe, für ein LGS mit Ordnung 32768 gerechnet mit einer NVIDIA GTX 1080 Ti 11GB Die optimale Thread-Block-Größe für die Kernels        |            |

|                                   | beträgt 256                                                                                                                                                                                                                | 63         |

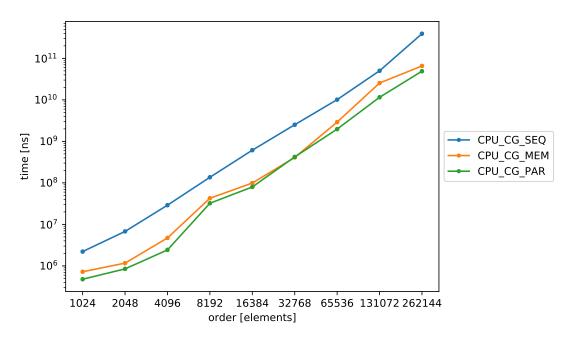

| 6.4                               | Laufzeit einer Iteration der CPU-Implementierungen, in Abhängigkeit der                                                                                                                                                    |            |

|                                   | Ordnung der LGS gerechnet mit dual-Socket Intel Xeon Gold 5120                                                                                                                                                             | 64         |

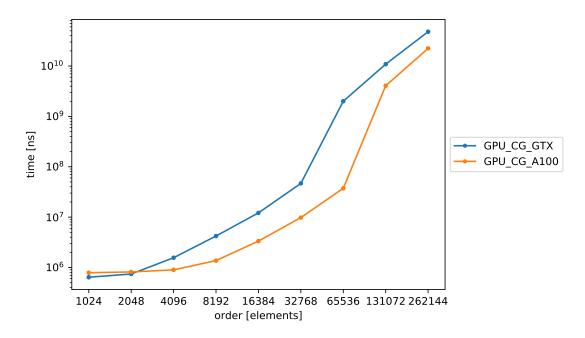

| 6.5                               | Laufzeit einer Iteration der Einzel-GPU-Implementierungen, in Abhängig-                                                                                                                                                    |            |

|                                   | keit der Ordnung der LGS blau wurde mit einer NVIDIA GTX 1080 Ti 11GB                                                                                                                                                      | <b>(</b> E |

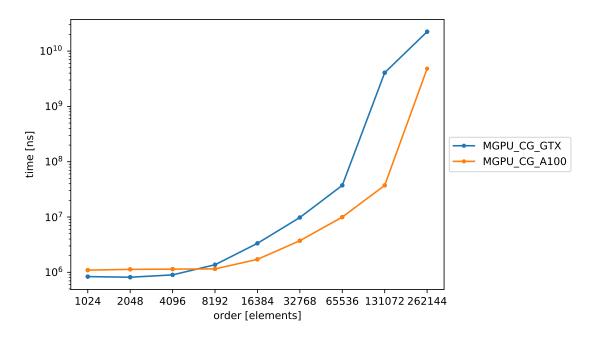

| 6 6                               | gerechnet gelb wurde mit einer NVIDIA A100-SXM4 40GB gerechnet Laufzeit einer Iteration der Multi-GPU-Implementierungen, in Abhängigkeit                                                                                   | 65         |

| 6.6                               | der Ordnung der LGS blau wurde mit acht NVIDIA GTX 1080 Ti 11GB gerechnet                                                                                                                                                  |            |

|                                   | gelb wurde mit vier NVIDIA A100-SXM4 40GB gerechnet                                                                                                                                                                        | 67         |

|                                   | geno wanae nini viel ivviidili lituu diniit tuod geneeniele                                                                                                                                                                | U/         |

## **Tabellenverzeichnis**

| 6.1 | Spezifikation eines Intel Xeon Gold 5120 Prozessors Quelle: [Int]        | 57 |

|-----|--------------------------------------------------------------------------|----|

| 6.2 | Spezifikation einer NVIDIA GTX 1080 Ti Quellen: [NVIb] [NVIc]            | 58 |

| 6.3 | Spezifikation eines AMD EPYC 7763 Prozessors Quelle: [Adv]               | 58 |

| 6.4 | Spezifikation einer NVIDIA A100-SXM4 Quelle: [NVIa]                      | 59 |

| 6.5 | Durchschnittlich gemessene Laufzeiten der Multi-GPU-Implementierung, für |    |

|     | LGS massiver Größe                                                       | 68 |

# Verzeichnis der Listings

| 4.1  | Beispiel eines CUDA-Kernels zum Aufsummieren eines Arrays                   | 29  |

|------|-----------------------------------------------------------------------------|-----|

| 4.2  | Beispiel eines CUDA-Programms zum Aufsummieren eines Arrays                 | 30  |

| 4.3  | Beispiel eines CUDA-Programms mit Asynchronen Funktionen, Speicherregis-    |     |

|      | trierung auf dem Host und freier Wahl des Devices                           | 33  |

| 5.1  | Auszug aus der sequenziellen CG-Implementierung: Explizite Berechnung des   |     |

|      | Residuums                                                                   | 39  |

| 5.2  | Auszug aus der Mehrkernprozessor Implementierung: Explizite Berechnung      |     |

|      | des Residuums                                                               | 40  |

| 5.3  | Auszug aus der CPU-Implementierung mit Speicherbegrenzung: Explizite Be-    |     |

|      | rechnung des Residuums                                                      | 41  |

| 5.4  | Auszug aus der CPU-Implementierung mit Speicherbegrenzung: Herleitung       |     |

|      | der Blockgrößen                                                             | 42  |

| 5.5  | Auszug aus der GPU-Implementierung: Host-Funktion zum Berechnen des         |     |

|      | Matrix-Vektor-Produkts                                                      | 45  |

| 5.6  | Auszug aus der GPU-Implementierung: Kernel zum Berechnen des Matrix-        |     |

|      | Vektor-Produkts                                                             | 47  |

| 5.7  | Auszug aus der GPU-Implementierung: Host-Funktion zum Berechnen des         |     |

|      | Skalarprodukts                                                              | 49  |

| 5.8  | Auszug aus der GPU-Implementierung: Kernel zum Berechnen des Skalarprodukts | 50  |

| 5.9  | Auszug aus der GPU-Implementierung: Kernel zum Berechnen der Vektoraddition | 51  |

| 5.10 | Auszug aus der Multi-GPU-Implementierung: Host-Funktion zum Berechnen       |     |

|      | des Matrix-Vektor-Produkts                                                  | 52  |

| 5.11 | Auszug aus der Multi-GPU-Implementierung: Schleife zum Berechnen der        | ~ - |

|      | Teilrechnungen                                                              | 54  |

|      | icincomunicon                                                               | JI  |

## Verzeichnis der Algorithmen

| 3.1 | Algorithmus des CG-Verfahrens                | 26 |

|-----|----------------------------------------------|----|

| 5.1 | Allgemeine Struktur der CG-Implementierungen | 38 |

## Abkürzungsverzeichnis

**API** Programmierschnittstelle. 27

**CG** Conjugate Gradient. 3, 17, 19, 21, 57

**CUDA** Compute Unified Device Architecture. 27, 58

**FIFO** first in - first out. 32

**GPU** Graphics Processing Unit. 17, 19, 29, 37, 57

LGS Lineares Gleichungssystem. 17, 19, 21, 37, 60

RAM Hauptspeicher. 34, 37, 57

SM Streaming Multiprozessor. 29, 61

VRAM Grafikspeicher. 19, 31, 37, 61

## 1 Einleitung

Ein zentrales Problem bei wissenschaftlichen Simulationen ist das Lösen von Lineares Gleichungssystem (LGS). Zum Lösen von LGS, deren Koeffizientenmatrix A sowohl symmetrisch als auch positiv definit ist, kann das Verfahren der konjugierten Gradienten (engl. Conjugate Gradient (CG)) [She+94] verwendet werden. Im CG-Verfahren sind mehrfach Vektor-und Matrix-Vektor-Operationen vertreten, für deren Berechnung sich Grafikkarten (engl. Graphics Processing Units (GPUs)) besonders eignen.

Wenn ein LGS auf einer GPU vom CG-Verfahren gelöst werden soll, dann müssen sich die Daten, für die Berechnung im Speicher der GPU befinden. Das schließt den Vektor b und insbesondere die Matrix A des LGS Ax = b ein. In der heutigen Zeit nimmt die Größe von wissenschaftlichen Simulationen jedoch rapide zu, was vor allem an der Menge der verfügbaren Daten liegt, die von verteilten Systemen, smart Devices o.ä. erfasst werden. Deshalb steigt auch die Größe der LGS an, die es in den entsprechenden Simulationen zu lösen gilt. Infolge dessen reicht der Speicher einer GPU nicht mehr aus, um alle Daten für die Berechnung des CG-Algorithmus zeitgleich im Speicher zu halten. Deshalb müssen beim Lösen von zu großen LGS, mehrfach neue Daten auf die GPU kopiert werden, was die Laufzeit der Berechnung negativ beeinflusst.

Eine offensichtliche Lösung zum Mindern dieses Problems ist es, mehrere GPUs zu verwenden. Die kombinierte Speicherkapazität der GPUs ermöglicht es, mehr Daten auf den GPUs verteilt zu hinterlegen, sodass weniger Daten regelmäßig kopiert werden müssen. Zudem ist die Rechenleistung von mehreren GPUs um ein vielfaches größer als die einer einfachen GPUs, was die Rechengeschwindigkeit zusätzlich erhöht.

Ziel dieser Arbeit ist es deshalb, den CG-Algorithmus für mehrere Grafikkarten implementiert, sodass die Probleme, die beim Rechnen auf einzelnen GPU auftreten, zu minimieren. Die Programmierplatform CUDA [NVI23] wurde verwendet, um Berechnungen auf den GPUs auszuführen. Die Matrix-Vektor-Multiplikation ist die mit Abstand aufwändigste Rechenoperation, die bei der Ausführung des CG-Verfahrens zu berechnen ist. Deshalb wurde ein besonderer Fokus auf die effiziente Ausführung der Matrix-Vektor-Multiplikation gelegt.

Im folgenden Kapitel 2 werden verwandte Arbeiten vorgestellt, in denen ebenfalls das CG-Verfahren auf GPUs implementiert wird. Danach wird in Kapitel 3 die Theorie hinter dem CG-Verfahren vorgestellt. In Kapitel 4 wird die Programmierplatform CUDA vorgestellt, die im Rahmen dieser Arbeit verwendet wurde, um auf Grafikkarten zu rechnen. Das CG-Verfahren wurde für mehrere Umgebungen implementiert, um sich der Multi-GPU-Implementierung

anzunähern. Die einzelnen Implementierungen werden in Kapitel 5 vorgestellt. In Kapitel 6 werden die Ergebnisse vorgestellt, die im Rahmen dieser Arbeit erzielt wurden. Zuletzt wird in Kapitel 7 ein Fazit geschlossen und es wird ein Ausblick auf potentielle Erweiterungen der Implementierung gegeben.

## 2 Verwandte Arbeiten

Ursprünglich wurde das Verfahren der konjugierten Gradienten (engl. Conjugate Gradient (CG)) 1952 von Hestenes und Stiefel [HS+52] als eine Methode zum Lösen linearer Gleichungssysteme (LGS) vorgestellt. Als effizientes Verfahren zum Lösen von LGS ist das CG-Verfahren in mehreren CPU-Programmbibliotheken vertreten, wie z.B. in NumPy [Oli–] oder EIGEN [GJ+10].

Zahlreiche Veröffentlichungen befassen sich mit der effizienten Implementierung des CG-Verfahrens auf mehreren Graphics Processing Unit (GPU)s. Im Folgenden werden einige dieser Veröffentlichungen vorgestellt.

Cevahir et al. stellen 2009 in ihrer Arbeit [CNM09] eine Implementierung des CG-Verfahrens vor, das mehrere GPUs zum Rechnen verwendet. In ihrer Arbeit liegt der Schwerpunkt darauf mit GPUs, die nur einfache Präzision unterstützen, doppelte Präzision zu erzielen. In einer späteren Arbeit [CNM10] vertiefen Cevahir et al. ihre Forschung, indem sie die Berechnung auf mehrere Knoten verteilen, die ihrerseits mehrere GPUs zum Rechnen verwenden. Der Schwerpunkt dieser Arbeit liegt auf der Koordinierung der Knoten und deren Kommunikation untereinander.

2010 veröffentlichten Ament et al. [AKWS10] eine Implementierung des vorkonditionierten CG-Verfahrens auf mehreren GPUs. Die Implementierung überlagert die Kopiervorgänge zwischen den einzelnen GPUs mit Rechenvorgängen, um ein hohes Maß an Parallelität zu erzielen. Die Technik der überlagerten Kopiervorgänge wird in dieser Arbeit adaptiert.

In den Arbeiten von Li et al. [LL14], Müller et al. [MGSS13] und Labutin et al. [LS13] wird das CG-Verfahren jeweils mit einem Vorkonditionierer auf ein bestimmtes Problem spezialisiert. Dabei ist der jeweilige Vorkonditionerer der Schwerpunkt der Arbeit.

In allen hier vorgestellten Arbeiten werden für die Matrix des Lineares Gleichungssystem (LGS) Speicherformate verwendet, die für dünnbesetzte Matrizen geeignet sind. Zudem gehen sie davon aus, dass das gesammte LGS in den Grafikspeicher (VRAM) der GPUs kopiert werden kann. Diese Annahmen grenzen sie von dieser Arbeit ab.

## 3 Verfahren der konjugierten Gradienten

Das Verfahren der konjugierten Gradienten (engl. Conjugate Gradient (CG)) ist ein iteratives Verfahren zum Lösen eines Lineares Gleichungssystem (LGS) der Form Ax = b. Dabei ist das CG-Verfahren nur auf solche LGS anwendbar, bei denen die Koeffizientenmatrix A sowohl symmetrisch als auch positiv definit (d.h. alle Eigenwerte von A sind positiv) ist. Erstmals vorgestellt wurde das CG-Verfahren von Hestenes und Stiefel [HS+52] als eine Verfeinerung des Conjugate Direction Verfahrens. Eine modernere Publikation ist von Shewchuk et al. [She+94], in der das CG-Verfahren ausführlich hergeleitet, beschrieben und analysiert wird. Die Informationen dieses Kapitels bezüglich des CG-Verfahrens sind aus Shewchuk et al. [She+94] entnommen.

Bei exaktem Rechnen benötigt das CG-Verfahren maximal n Iterationen, wobei n der Ordnung des LGS entspricht, ähnlich wie direkte Löser. Tatsächlich benötigt das CG-Verfahren jedoch nur m < n Iterationen, um eine gut approximierte Lösung zu finden. Dies ist dem Konvergenzverhalten CG-Verfahrens geschuldet. Frühe Iterationen nähern die Lösung schneller an, als spätere Iterationen. Wenn das CG-Verfahren nach m < n Schritten terminiert, dann würden die letzten n-m Iterationen die Lösung in so geringem Maße verbessern, dass diese Iterationen vernachlässigt werden können.

Bei iterativen Verfahren ist der aktuelle Fehler einer Iteration beschrieben durch  $e_i = x_i - x$ , wobei  $x_i$  die Lösung der aktuellen Iteration ist und x die tatsächliche Lösung. Für ein iteratives Verfahren kann die Konvergenz des Fehlers beschrieben werden durch  $||e_i|| \le c(f(\kappa(A)))^i||e_0||$ . Hier ist c eine Konstante,  $||\cdot||$  die Betragsnorm und  $f(\kappa(A))$  eine inhärente Funktion des Verfahrens, die von der Konditionszahl  $\kappa(A) = \frac{\lambda_{max}}{\lambda_{min}}$  der Matrix A abhängt. Je kleiner  $f(\kappa(A))$  ist, desto schneller konvergiert der Fehler gegen 0, ist  $f(\kappa(A)) >= 1$ , so konvergiert ein Verfahren nicht.

Für das CG-Verfahren gilt

$$f_{CG}(\kappa(A)) = \frac{\sqrt{\kappa(A)} - 1}{\sqrt{\kappa(A)} + 1} = 1 - \frac{2}{\sqrt{\kappa(A)} + 1}$$

[She+94]. Damit konvergiert das CG-Verfahren schneller als andere iterative Verfahren, wie z.B. das Jacobi-Verfahren mit

$$f_{Jacobi}(\kappa(A)) = \frac{\kappa(A) - 1}{\kappa(A) + 1} = 2 - \frac{1}{\kappa(A)}$$

[Saa03].

Da das CG-Verfahren für kleineres  $\kappa(A)$  schneller konvergiert, wird das es häufig in Kombination mit Vorkonditionierern verwendet. Das vorkonditionierte CG-Verfahren ist jedoch nicht Teil dieser Arbeit und wird an dieser Stelle nur der Vollständigkeit halber erwähnt.

Im Folgenden wird zunächst die Idee des CG-Verfahren erklärt, sowie die mathematischen Zusammenhänge bei der Umsetzung dieser Idee. Danach wird der Algorithmus erläutert, der das Vorgehen des CG-Verfahren umsetzt.

### 3.1 Die Vorgehensweise des CG-Verfahrens

Das CG-Verfahren löst das LGS Ax=b durch das Lösen eines äquivalenten Problems. Um die Lösung des LGS zu ermittelt, minimiert das CG-Verfahren die quadratischen Funktion  $F(x)=\frac{1}{2}x^TAx-x^Tb+c$ . Da A positiv definit ist, gilt  $x^TAx>0$  und somit, dass das Minimum  $x_F$  von F eindeutig ist. Der Vektor  $x_F$ , der das Minimum von F ist, löst ebenso das LGS Ax=b. Dies wird ersichtlich durch Ableitung von F nach x:

$$\frac{\partial}{\partial x}F(x) = \frac{1}{2}\frac{\partial}{\partial x}(x^TAx) - \frac{\partial}{\partial x}(x^Tb) + \frac{\partial}{\partial x}(c) = \frac{1}{2}(Ax + A^Tx) - b \tag{3.1}$$

Da A symmetrisch ist, gilt  $\frac{1}{2}(Ax + A^Tx) - b = Ax - b$ , somit entspricht das Minimum der Funktion F der Lösung x des LGS Ax = b. Für diese Herleitung sind sowohl die Symmetrie als auch die positive Definitheit der Matrix A erforderlich.

Um das Minimum von F zu finden, beginnt das CG-Verfahren damit, mit einem initialen Suchpunkt  $x_0$ . Die Idee des CG-Verfahrens ist es, den initialen Fehler  $e_0 = x_0 - x$  nach und nach aufzulösen, sodass nach m Iterationen gilt  $e_m \approx 0$  und damit  $x_m = x + e_m \approx x$ .

Die Anzahl der vom CG-Verfahren benötigten Iteration hängt abgesehen vom LGS selbst zusätzlich noch von der Anzahl der linearen Komponenten ab, die notwendig sind, um den initialen Fehler  $e_0$  auszugleichen. Wenn für viele der linearen Komponenten gilt  $\alpha_i d_i \approx 0$ , dann ist der zugehörige initiale Suchpunkt  $x_0$  gut gewählt. Da der initale Fehler jedoch auch von der tatsächlichen Lösung x abhängt, die unbekannt ist, muss der initiale Suchpunkt  $x_0$  im Normalfall willkürlich gewählt werden. Dazu betrachtet das CG-Verfahren den initialen Fehler als Linearkombination  $e_0 = \sum_{i=0}^{n-1} \delta_i d_i$ . In jeder Iteration entfernt das CG-Verfahren eine Komponente dieser Linearkombination durch das Voranschreiten des Suchpunktes  $x_{i+1} = x_i + \alpha_i d_i$ , mit Schrittweite  $\alpha_i = -\delta_i$  und Suchrichtung  $d_i$ . Nach ausreichend Iterationen gilt  $\sum_{i=0}^{m-1} \alpha_i d_i \approx -e_0$  und der Fehler wurde annähernd aufgelöst.

Nehmen wir für einen Moment an, dass die Suchrichtung  $d_i$  paarweise orthogonal sind, d.h.  $d_i^T d_j = 0$  für  $i \neq j$ . In diesem Fall kann die zugehörige Schrittweite  $\alpha_i$  bestimmt werden, da die zugehörige Richtung komplett aus dem folgenden Fehler  $e_{i+1}$  entfernt sein muss. Mathematisch ausgedrückt muss der verbleibende Fehler  $e_{i+1}$  nach dem Addieren der Linearkomponente  $\alpha_i d_i$

orthogonal zum aktuellen Vektor  $d_i$  sein. Für dieses Vorgehen muss jedoch der Fehler  $e_{i+1}=x_{i+1}-x$  und damit die tatsächliche Lösung bekannt sein. Der CG-Algorithmus verwendet aus diesem Grund nicht paarweise orthogonale, sondern A-orthogonale Suchrichtungen, d.h.  $d_i^T A d_j = 0$  für  $i \neq j$ . In diesem Fall muss der nachfolgende Fehler  $e_{i+1}$  nur noch A-orthogonal zum aktuellen Vektor  $d_i$  sein, d.h.  $d_i^T A e_{i+1} = 0$ . Dabei wird ausgenutzt, dass  $A e_i = Ax_i - Ax = Ax_i - b$  gilt, was unabhängig von der tatsächlichen Lösung berechnet werden kann. Im Folgenden ist  $r_i$  das Residuum eines Suchpunkts  $x_i$  mit  $r_i = b - Ax_i = -Ae_i$ .

$$d_i^T A e_{i+1} = 0$$

$$d_i^T A(x_{i+1} - x) = 0$$

$$d_i^T (A(x_i + \alpha_i d_i - b)) = 0$$

$$d_i^T (Ax_i - b) + \alpha_i d_i^T A d_i = 0$$

$$-d_i^T r_i + \alpha_i d_i^T A d_i = 0$$

$$\alpha_i = \frac{d_i^T r_i}{d_i^T A d_i}$$

(3.2)

Später in diesem Abschnitt wird noch gezeigt, dass für eine Suchrichtung gilt  $d_{i+1} = r_{i+1} + \beta_{i+1}d_i$ , mit einem Parameter  $\beta_i$ . Damit kann folgende Gleichung gezeigt werden:

$$r_{i+1}^{T}d_{i+1} = r_{i+1}^{T}(r_{i+1} + \beta_{i+1}d_{i})$$

$$= r_{i+1}^{T}r_{i+1} + \beta_{i+1}r_{i+1}^{T}d_{i}$$

$$r_{i+1}^{T}d_{i+1} = r_{i+1}^{T}r_{i+1} + 0$$

(3.3)

Diese Gleichung in die obige Formel für  $\alpha_i$  eingesetzt ergibt die Formel für  $\alpha_i$ , wie im CG-Verfahren verwendet:

$$\alpha_i = \frac{d_i^T r_i}{d_i^T A d_i} = \frac{r_i^T r_i}{d_i^T A d_i} \tag{3.4}$$

Offen steht noch, wie das CG-Verfahren die A-orthogonalen Suchrichtungen konstruiert. Die erste Suchrichtung  $d_0$  wird mit dem Residuum  $r_i = b - Ax_i$  des initialen Suchpunkts gleichgesetzt, also  $d_0 = r_0 = b - Ax_0$ . Alle folgenden Suchrichtungen werden durch  $d_{i+1} = r_{i+1} + \beta_{i+1}d_i$  konstruiert.

Die Definition des Parameters  $\beta_i$  leitet sich her vom Gram-Schmidtschen Orthogonalisierungsverfahrens [Sch07]. Das Gram-Schmidt-Verfahren konstruiert aus einer Menge von N linear unabhängigen Vektoren  $\{u_0,...,u_{N-1}\}$  eine Menge von N orthogonalen Vektoren  $\{o_0,...,o_{N-1}\}$ . Um einen neuen Vektor  $o_k$  zu konstruieren, werden alle Anteile in Richtung der  $o_i$  mit i < k von  $u_k$  entfernt:

$$o_k = u_k - \sum_{i=0}^{k-1} \frac{o_i^T u_k}{o_i^T o_i} o_i$$

(3.5)

Da die  $u_i$  linear unabhängig sind, bleibt ein Vektor  $o_i$  übrig, der orthogonal zu den  $o_j$  mit j < i ist.

Für das CG-Verfahren ist die A-orthogonalität der Suchrichtungen  $d_i$  notwendig, deshalb wird Gleichung (3.5) dahingehend abgewandelt:

$$d_k = u_k - \sum_{i=0}^{k-1} \frac{d_i^T A u_k}{d_i^T A d_i} d_i$$

(3.6)

Die Formel für die Suchrichtungen, die im CG-Verfahren verwendet wird, lässt sich aus Gleichung (3.6) herleiten. Dazu sind jedoch noch zwei Gleichungen notwendig, die nicht explizit in Shewchuk et al. [She+94] vorkommen, aber wie hier hergeleitet werden können:

$$x_{i+1} = x_i + \alpha_i d_i$$

$$d_i = \frac{x_{i+1} - x_i}{\alpha_i}$$

$$d_i = \frac{(x + e_{i+1}) - (x + e_i)}{\alpha_i}$$

$$d_i = \frac{e_{i+1} - e_i}{\alpha_i}$$

(3.7)

Gleichung (3.7) wird sogleich in Gleichung (3.8) verwendet:

$$d_{i}^{T} A r_{k} = \left(\frac{e_{i+1} - e_{i}}{\alpha_{i}}\right)^{T} A r_{k}$$

$$= \frac{1}{\alpha_{i}} (e_{i+1}^{T} A r_{k} - e_{i}^{T} A r_{k})$$

$$= \frac{1}{\alpha_{i}} (r_{i+1}^{T} r_{k} - r_{i}^{T} r_{k})$$

$$d_{i}^{T} A r_{k} = \frac{d_{i}^{T} A d_{i}}{r_{i}^{T} r_{i}} (r_{i+1}^{T} r_{k} - r_{i}^{T} r_{k})$$

(3.8)

Gleichung (3.6) kann nun vereinfacht werden. Als Menge von linear unabhängigen Vektoren  $\{u_0, ..., u_{N-1}\}$  verwendet das CG-Verfahren gerade die Residuen  $\{r_0, ..., r_{N-1}\}$ .

$$d_{k} = r_{k} - \sum_{i=0}^{k-1} \frac{d_{i}^{T} A r_{k}}{d_{i}^{T} A d_{i}} d_{i}$$

$$d_{k} = r_{k} - \sum_{i=0}^{k-1} \frac{d_{i}^{T} A d_{i}}{r_{i}^{T} r_{i}} \frac{r_{k}^{T} r_{i+1} - r_{k}^{T} r_{i}}{d_{i}^{T} A d_{i}} d_{i}$$

$$d_{k} = r_{k} - \sum_{i=0}^{k-1} \frac{r_{k}^{T} r_{i+1} - r_{k}^{T} r_{i}}{r_{i}^{T} r_{i}} d_{i}$$

$$d_{k} = r_{k} - \frac{r_{k}^{T} r_{k}}{r_{k-1}^{T} r_{k-1}} d_{k-1}$$

$$(3.9)$$

Letzter Gleichungsschritt ist möglich, da die Residuen  $r_i$  paarweise orthogonal sind. Um das zu sehen, ist es notwendig sich klar zu machen, dass eine Schrittweite  $\alpha_i$  immer so gewählt ist, dass der Fehler nach dem Schritt  $e_{i+1}$  A-orthogonal zur aktuellen Suchrichtung  $d_i$  ist, d.h.  $d_i^T A e_{i+1} = 0$ . Mit  $r_{i+1} = A e_{i+1}$ , folgt daraus, dass das Residuum nach dem Schritt orthogonal zur Suchrichtung ist:  $d_i^T r_{i+1} = 0$ . Da  $d_i$  eine Linearkombination der  $r_j$  mit  $j \leq i$  ist, ist  $r_{i+1}$  ebenfalls orthogonal zu den  $r_j$  mit  $j \leq i$ .

Es wurde gezeigt, dass jede Suchrichtung des CG-Verfahrens eine Linearkombination aller vergangenen Residuen ist. Da das Residuum eines Suchpunktes  $r_i = x_i - x$  zum Minimum der Funktion F hinzeigt, ist das die Richtung des stärksten Gefälles und damit gerade der negative Gradient  $\operatorname{grad} F(x_i)$ . Somit ist eine Suchrichtung ebenfalls eine Linearkombination oder Konjugation der Gradienten. Hierher stammt der Name des CG-Verfahrens.

### 3.2 Der Algorithmus zur Vorgehensweise

Mit den geklärten Zusammenhängen kann nun der Algorithmus zusammengesetzt werden, der das CG-Verfahren implementiert. In Algorithmus 3.1 steht dieser in Pseudocode, abgewandelt aus Shewchuk et al. [She+94]. Von Zeile zwei bis Zeile fünf wird der Algorithmus initialisiert. In Zeile sechs wird die Schleife begonnen, deren Rumpf sich von Zeile sieben bis einschließlich Zeile 16 erstreckt. Die restlichen Zeilen rahmen den Algorithmus ein und haben keine weitere Bedeutung.

In Zeile zwei wird zunächst der initiale Suchpunkt  $x_0$  gewählt, hier als Nullvektor. Anschließend wird in Zeile drei das zugehörige Residuum  $r_0$  berechnet und der erste Suchvektor  $d_0$  wird in Zeile vier mit dem Residuum gleichgesetzt. Zeile fünf initialisiert den Schleifenzähler für die kommende Schleife. Die Hauptschleife wird in Zeile sechs begonnen und auf  $i_{max}$  Iterationen beschränkt. Zusätzlich endet die Schleife, wenn eine relative Toleranz  $\epsilon$  unterschritten wurde. In Zeile sieben wird die Schrittweite  $\alpha_i$  zur bereits berechnen Suchrichtung  $d_i$  bestimmt. Mit der Suchrichtung und der Schrittweite feststehend, wird in Zeile acht der neue Suchpunkt  $x_{i+1}$  berechnet. Anschließend wird das zum neuen Suchpunkt  $x_{i+1}$  gehörende Residuum  $r_{i+1}$  berechnet. In Zeile zehn wird dies, wie in den meisten Fällen implizit durchgeführt. In regelmäßigen Abständen (hier, jeder 50. Schleifendurchlauf) wir das Residuum in Zeile zwölf explizit berechnet. In Zeile 14 wird der Parameter  $\beta_{i+1}$  berechnet, mit dem in Zeile 15 die neue Suchrichtung  $d_{i+1}$  konstruiert wird. Abschließend wird in Zeile 16 noch der Schleifenzähler inkrementiert.

Bei exaktem Rechnen ist das implizite und das explizite Berechnen des Residuums äquivalent:

$$r_{i+1} = b - Ax_{i+1}$$

$$r_{i+1} = -Ae_{i+1}$$

$$= -A(e_i - \alpha_i d_i)$$

$$= r_i - \alpha_i Ad_i$$

(3.10)

#### Algorithmus 3.1 Algorithmus des CG-Verfahrens

```

1: procedure

x_0 \leftarrow (0, ..., 0)^T

2:

// willkürliche Wahl von x_0

r_0 \leftarrow b - Ax_0

3:

d_0 \leftarrow r_0

4:

i \leftarrow 0

5:

while i < i_{max}and||r_i|| > \epsilon ||r_0|| do

// Abbruch nach maximal i_{max} Iterationen

6:

\alpha_i \leftarrow \frac{r_i^T r_i}{d_i^T A d_i}

7:

x_{i+1} \leftarrow x_i + \alpha_i d_i

8:

if i is multiple of 50 then

9:

r_{i+1} \leftarrow b - Ax_{i+1}

// berechne r_{i+1} explizit

10:

else

11:

r_{i+1} \leftarrow r_i - \alpha_i A d_i

// berechne r_{i+1} implizit

12:

end if \beta_{i+1} \leftarrow \frac{r_{i+1}^T r_{i+1}}{r_i^T r_i}

13:

14:

d_{i+1} \leftarrow r_{i+1} + \beta_{i+1} d_i

15:

i \leftarrow i + 1

16:

end while

17:

18: end procedure

```

Das Residuum implizit zu berechnen, ermöglicht es, das Matrix-Vektor-Produkt  $Ad_i$ , das in Zeile sieben berechnet werden muss, wiederzuverwendet. So muss in jedem Schleifendurchlauf nur eine Matrix-Vektor-Multiplikation durchgeführt werden.

Der Nachteil der impliziten Berechnungsweise ist, dass der aktuelle Suchpunkt  $x_{i+1}$  nicht explizit in der Berechnung des Residuum  $r_{i+1}$  enthalten ist. Das bedeutet, dass in der Gegenwart von Rundungsfehlern das explizit berechnete Residuum  $r_{i+1} = b - Ax_{i+1}$  und das implizite berechnete Residuum  $r_{i+1} = r_i - \alpha_i Ad_i$  voneinander abweichen. In diesem Fall muss das Residuum regelmäßig explizit berechnet werden, um ein zu starkes Abweichen zu verhindern.

Neben der bereits erwähnten Matrix-Vektor-Multiplikation in Zeile sieben werden noch mehrere Vektor-Vektor Operationen und skalare Operationen im Schleifenrumpf durchgeführt. Damit hat eine Ausfühung der Schleife eine asymptotische Laufzeitkomplexität von  $\mathcal{O}(n^2)$ . Wie bereits angemerkt benötigt, benötigt dass das Verfahren m < n Iterationen, um eine Lösung zu approximieren. Damit gilt für die asymptotische Laufzeitkomplexität des oben gezeigten Algorithmus  $\mathcal{O}(n^3)$ .

## 4 CUDA

In diesem Kapitel wird Compute Unified Device Architecture (CUDA) vorgestellt, die Programmierplatform und Programmierschnittstelle (API), die im Rahmen dieser Arbeit verwendet wurde, um auf Grafikkarten zu rechnen. Es werden die Aspekte von CUDA beleuchtet, die notwendig sind, um die Implementierungen aus Kapitel 5 zu verstehen. Die Informationen dieses Kapitels stammen aus dem CUDA Programming Guide [NVI23]. Die einzelnen Funktionsaufrufe sind im CUDA API Reference Guide zu finden [NVI23].

Im Folgenden werden zunächst Grundlagen von CUDA erklärt. Anschließend werden asynchrone Operationen in CUDA vorgestellt. Zuletzt wird darauf eingegangen, wie multiple Grafikkarten genutzt werden können.

### 4.1 CUDA-Grundlagen

CUDA erweitert eine Programmiersprache (hier C++) mit Konstrukten und Funktionen, um heterogenes Programmieren zu ermöglichen. Durch die von CUDA angebotenen Erweiterungen, können spezielle Funktionen, genannt Kernels definiert werden, die auf der Grafikkarte aufgerufen werden. Die ausführende Grafikkarte wird in CUDA Device genannt, die Maschine, auf der ein CUDA-Programm gestartet wird, wird Host genannt.

#### 4.1.1 Kernels

Ein CUDA-Kernel ist eine Funktion, die von mehreren Threads nebenläufig auf der Grafikkarte ausgeführt wird. Die Ausführung eines Kernels erfolgt auf einem Gitter (engl. Grid), über das definiert wird, von wie vielen Threads ein Kernel ausgeführt wird. Ein Gitter beschreibt eine Anordnung von Thread-Blöcken und innerhalb von jedem Block eine Anordnung von Threads. Threads im selben Thread-Block teilen sich eine Speicheradresse auf dem Grafikprozessor und können über diesen effizient Daten austauschen. In komplexeren Kernels arbeiten die Threads in einem Thread-Block als Einheit zusammen.

Die Anordnung von Threads in Thread-Blöcken und von Thread-Blöcken im Gitter kann in einer, zwei oder in drei Dimensionen angegeben werden. In Abbildung 4.1 ist ein Beispiel eines Gitters mit Thread-Blöcken, die in zwei Dimensionen definiert sind. Im Beispiel ist zu sehen, wie Threads innerhalb ihres Thread-Blocks und Thread-Blöcke innerhalb des Gitters

**Abbildung 4.1:** Hierarchische Struktur von Threads in CUDA Quelle: CUDA Programming Guide [NVI23], Kapitel 2.2

nummeriert werden. Mit dieser Nummerierung hat jeder Thread einen globalen Index, anhand dessen er seine Berechnung ausrichtet.

In Listing 4.1 ist ein Beispiel eines Kernels zu sehen, der ein Array aufsummiert. Der Präfix \_\_global\_\_ bei der Funktionsdeklaration gibt an, dass es sich bei dieser Funktion um einen Kernel handelt, der vom Host aufgerufen werden kann. Die Variable tid definiert den globalen Index des ausführenden Threads. Falls der Index des ausführenden Threads innerhalb der Länge des aufzusummierenden Arrays ist, so addiert der Thread den Wert an diese Stelle. Die Funktion atomicAdd wird dazu verwendet, wechselseitigen Ausschluss beim Addieren auf die Variable d\_sum zu garantieren.

#### **Listing 4.1** Beispiel eines CUDA-Kernels zum Aufsummieren eines Arrays

```

__global___ sum_array_kernel(double* d_arr, double* d_sum, size_t array_size) {

unsigned int tid = blockIdx.x * blockDim.x + threadIdx.x;

if (tid < array_size)

atomicAdd(d_sum, d_arr[tid]);

}</pre>

```

#### 4.1.2 Hardwareumsetzung

In diesem Kapitel wird auf die Architektur von CUDA-fähigen Grafikkarten eingegangen und wie Kernels darauf ausgeführt werden. Damit eine NVIDIA-Grafikkarte CUDA-fähig ist, muss der Grafikprozessor (engl. Graphics Processing Unit (GPU)) der Grafikkarte einer einheitlichen Architektur folgen. Wie diese Architektur im Detail implementiert ist, hängt von der Mikroarchitektur der jeweiligen Grafikkarte ab. Mikroarchitekturen werden in dieser Arbeit nicht beleuchtet.

Die GPU einer Grafikkarte, ist unterteilt in eine Reihe von Streaming Multiprozessoren (SMs). Ein SM ist seinerseits unterteilt in mehrere CUDA-Kerne. Wenn ein Kernel vom Host aufgerufen wird, so werden die Thread-Blöcke des zugehörigen Gitters auf die SMs verteilt. 32 Threads eines Thread-Blocks werden zu einer Gruppen zusammengefasst, die Warp genannt werden. In jedem Berechnungsschritt eines SMs wird ein Berechnungsschritt eines gesammten Warps parellel von den CUDA-Kernen des SMs ausgeführt. Die SMs rechnen ihrerseits parallel, wodurch ein hohes Maß an Parallelität erzielt wird.

#### 4.1.3 Aufruf von Kernels

In Listing 4.2 ist eine Funktion zu sehen, die den Kernel aus Abschnitt 4.1.1 aufruft, sodass dieser ein Array aufsummiert. Der Funktion wird eine Referenz auf das aufzusummierende Array und die Größe des Arrays übergeben, sowie einen Zeiger auf die Adresse im Speicher, an die die Summe geschrieben werden soll.

Noch bevor Daten zur Berechnung auf das Device geladen werden können, muss dort Speicher allokiert werden. In Listing 4.2 werden in Zeile drei und vier Zeiger deklariert, die auf das Device zeigen werden. Die Funktion cudaMalloc allokiert in Zeile sieben und acht Speicher auf dem Device und schreibt die Adresse des allokierten Speichers in den als Referenz übergebenen Zeiger.

Die Speicherstelle, auf den der Zeiger d\_sum zeigt, wird in Zeile elf auf 0 gesetzt, damit dort das Array aufsummiert werden kann. In der darauffolgenden Zeile zwölf wird das Array auf das Device kopiert.

Um den Kernel auszuführen wird in den Zeile 15 und 16 das Gitter vorbereitet. Ein Thread-Block enthält 256 Threads, die in einer Reihe, d.h. in einer Dimension angeordnet sind. Die

#### **Listing 4.2** Beispiel eines CUDA-Programms zum Aufsummieren eines Arrays

```

void sum_array(double* h_arr, double* h_sum, size_t array_size) {

// Deklarierung der Zeiger auf das Device

double* d_sum;

double* d_arr;

// Speicherallokierung auf dem Device

cudaMalloc(\&d\_sum, \textbf{sizeof}(\textbf{double}));

cudaMalloc(&d_arr, array_size * sizeof(double));

// Initialisieren von Daten auf dem Device

10

cudaMemset(d_sum, 0, sizeof(double));

cudaMemcpy(d_arr, h_arr, array_size * sizeof(double), cudaMemcpyHostToDevice);

12

13

// Kernel-Aufruf

14

dim3 block_dim(256);

dim3 grid_dim((array_size - 1) / 256 + 1);

16

sum_array_kernel<<<grid_dim, block_dim>>>(d_arr, d_sum, array_size);

17

18

// Kopieren des Ergebnisses zum Host

19

cudaMemcpy(h_sum, d_sum, sizeof(double), cudaMemcpyDeviceToHost);

20

21

// Speicherfreigabe

cudaFree(d_sum);

cudaFree(d_arr);

24

}

25

```

Größe des Gitters wird mittels einer ganzzahligen Division bestimmt, bei der das Ergebnis aufgerundet wird. Dadurch überdecken die Thread-Blöcke das Array vollständig. Aus diesem Grund wird innerhalb des Kernels geprüft, ob sich der Index mit dem auf das Array zugegriffen wird noch innerhalb der Grenzen des Arrays befindet. Der Kernel-Aufruf erfolgt in Zeile 17.

Nach der Berechnung des Kernels wird das Ergebnis in Zeile 20 in die Adresse von h\_sum kopiert. Zuletzt wird in den Zeilen 23 und 24 der allokierte Speicher auf dem Device wieder freigegeben.

#### Kopieren einer Teilmatrix

Beim Kopieren von Teilmatrizen ist der Speicher, den es zu kopieren gilt, häufig nicht linear im Speicher angeordnet. Für diesen Fall gibt es in CUDA eine spezialisierte Funktion.

```

cudaError_t cudaMemcpy2D ( void* dst, size_t dpitch, const void* src,

size_t spitch, size_t width, size_t height, cudaMemcpyKind kind )

```

cudaMemcpy2D kopiert height Speichersegmente der Größe width in Bytes. Die Adresse des ersten Segments ist src, die Adresse der folgenden zu kopierenden Segmente ist jeweils um

spitch Bytes verschoben. Analog wird das erste Segment an die Adresse dst kopiert, die Zieladresse der folgenden Segmente ist jeweils um dpitch Bytes verschoben. Damit entspricht cudaMemcpy2D dem mehrfachen Aufrufen von cudaMemcpy, wenn dabei die Ziel- und Quelladressen einheitlich verschoben sind.

#### 4.1.4 Speicherhierarchie

Das Speichermodell in CUDA stellt unterschiedliche Arten von Speichern zur Verfügung, die einen festen Platz auf der Hardware der Grafikkarte einnehmen. Die gängigsten Speicherstellen und ihre Hierarchie werden hier vorgestellt.

**Global memory** ist der allgemeinste Speicher in der Hierarchie. Jeder Thread in einem Grid kann darauf zugreifen. Global memory befindet sich im Hauptspeicher der Grafikkarte, im Grafikspeicher (VRAM), weshalb Lese- und Schreibzugriffe darauf vergleichsweise langsam erfolgen (typischerweise hunderte von Zyklen).

Lese- und Schreibzugriffe auf global memory werden immer im L2-Cache der Grafikkarte zwischengespeichert und werden deshalb in Speicherbänke von 128 Bytes eingeteilt.

**Shared memory** ist ein Speicherbereich, auf den von allen Threads in einem Thread-Block zugegriffen werden kann. Damit Daten in diesem Bereich gespeichert werden, muss eine Variable mit dem Schlüsselwort \_\_shared\_\_ annotiert werden. Shared memory befindet sich im L1-Cache des SMs, dem der Thread-Block zugeordnet wurde. Damit sind Lese- und Schreibzugriffe auf shared memory um ein vielfaches schneller als Zugriffe auf global memory.

Ist der Platzbedarf der annotierten Variable zur Zeit der Kompilierung bekannt, so wird der shared memory statisch im L1-Cache eines SMs allokiert. Wenn der Platzbedarf nicht bekannt ist, so muss die Größe beim Kernel-Aufruf (siehe Abschnitt 4.1.1) als Parameter übergeben werden, um dynamisch allokiert zu werden.

**Register** sind die kleinsten und schnellsten Speicherbereiche, die einer GPU zur Verfügung stehen. Die Register befinden sich, ähnlich wie shared memory direkt auf einem SM. Wenn ein Thread-Block einem SM zugeordnet wird, wird jedem Thread dieses Thread-Blocks eine Menge von Registern zugeteilt. Bevor eine Berechnung für einen Thread auf einem CUDA-Kern ausgeführt werden kann, müssen die Daten für diese Berechnung in ein Register des Threads geladen werden.

Variablen und Arrays, die in einem Kernel definiert werden, werden nach Möglichkeit in Registern gehalten. Wenn kein Register mehr zum Speichern von Variablen zu Verfügung steht (engl. register spilling), so werden die Daten in local memory ausgelagert. **Local memory** ist, ähnlich wie ein Register ein Speicherbereich, der einem bestimmten Thread zur Verfügung steht. Anders als der Name es vermuten lässt, befindet sich local memory im VRAM, genau wie global memory. Zugriffe auf local memory sind also ähnlich langsam (typischerweise hunderte von Zyklen). Local memory wird immer dann verwendet, wenn die Register nicht ausreichend Speicher bieten oder wenn ein Thread-lokales Array eine dynamische Größe besitzt.

## 4.2 Asynchrone Operationen

Um eine einfache Berechnung auf der Grafikkarte durchzuführen müssen Daten auf das Device kopiert werden, eine Berechnung muss ausgeführt werden und das Ergebnis muss zurück auf den Host kopiert werden. In CUDA können diese drei Operationen unabhängig voneinander ausgeführt werden. Das heißt, zeitgleich zur Ausführung eines Kernels können Daten für andere Berechnungen vom und zum Device kopiert werden.

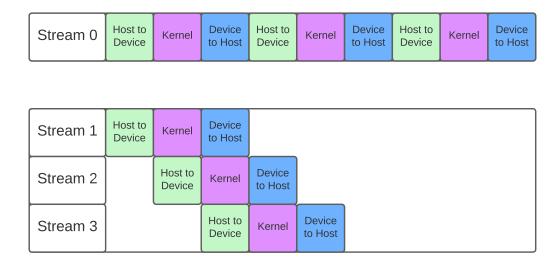

Dazu ist es notwendig, Asynchrone Operationen in Kombination mit CUDA-Streams zu verwenden. Abbildung 4.2 zeigt ein Beispiel, in dem drei Berechnungen überlagert werden können, um deren Ausführung zu beschleunigen. Grüne- und blaue Blöcke repräsentieren jeweils Kopieroperationen von Host zu Device und Device zu Host. Violette Blöcke repräsentieren Kernel aufrufe.

Ein CUDA-Stream ist eine Befehlswarteschlange für ein Device. Die Operationen in einem CUDA-Stream werden nach dem first in - first out (FIFO) Prinzip abgearbeitet. Wenn mehr als eine Warteschlange auf einem Device existieren, so können die Operationen der unterschiedlichen CUDA-Stream parallel ausgeführt werden, solange sie nicht auf den selben Speicher zugreifen und genügend Ressourcen verfügbar sind.

Listing 4.3 zeigt eine abgewandelte Funktion des Kernel-Aufrufs aus Abschnitt 4.1.3. Im hiesigen Beispiel wird in Zeile zehn ein CUDA-Stream deklariert und anschließend in Zeile elf erstellt. Die Funktionsaufrufe aus Abschnitt 4.1.3 finden sich hier in asynchronen Varianten wieder. Von Zeile 14 bis Zeile 31 werden die Funktionsaufrufe aus Abschnitt 4.1.3 in asynchronen Varianten ausgeführt.

Die asynchronen Funktionsaufrufe haben gemein, dass sie mit dem Suffix Async enden. Zusätzlich muss einem asynchronen Aufruf immer ein CUDA-Stream übergeben werden, sodass die Operation in diesen eingereiht werden können.

Der CUDA-Stream wird in Zeile 33 erst dann zerstört, wenn er leer ist, d.h. wenn alle Operationen ausgeführt sind. Um zu gewährleisten, dass die Summe des Arrays auf den Host kopiert wurde, wird dieser in Zeile 35 blockiert, bis alle Operationen auf dem Device fertig ausgeführt sind. Die nicht erwähnten Zeilen des Beispiels werden in den folgenden Abschnitten erklärt.

**Listing 4.3** Beispiel eines CUDA-Programms mit Asynchronen Funktionen, Speicherregistrierung auf dem Host und freier Wahl des Devices

```

void sum_array(double* h_arr, double* h_sum, size_t array_size, size_t device_id) {

cudaSetDevice(device_id);

// Auswahl des Devices

double* d_sum;

// Deklarierung der Zeiger auf das Device

double* d_arr;

// Registrieren von Speicher auf dem Host

cudaHostRegister(h_arr, array_size, cudaHostRegisterDefault);

cudaStream_t stream;

// Derklarieren und

cudaStreamCreate(&stream);

// Erstellen eines CUDA-Streams

11

12

// Asynchrone Speicherallokierung auf dem Device

13

cudaMallocAsync(&d_sum, sizeof(double), stream);

cudaMallocAsync(&d_arr, array_size * sizeof(double), stream);

15

16

// Asynchrones Initialisieren von Daten auf dem Device

17

cudaMemsetAsync(d_sum, 0, sizeof(double), stream);

cudaMemcpyAsync(d_arr, h_arr, array_size * sizeof(double), cudaMemcpyHostToDevice,

19

stream):

21

dim3 block_dim(256);

// Definieren des Gitters

dim3 grid_dim((array_size - 1) / 256 + 1);

23

24

// Asynchroner Kernel-Aufruf

25

sum_array_kernel<<<grid_dim, block_dim, 0, stream>>>(d_arr, d_sum, array_size);

26

27

// Asynchrones Kopieren der Ergebnisse zum Host

28

cudaMemcpyAsync(h_sum, d_sum, sizeof(double), cudaMemcpyDeviceToHost, stream);

cudaFreeAsync(d_arr, stream);

// Asynchrone Speicherfreigabe

31

cudaFreeAsync(d_sum, stream);

32

33

cudaStreamDestroy(stream);

// Zerstörden der CUDA-Streams

34

35

cudaDeviceSynchronize();

// Warten auf das Device

cudaHostUnregister(h_arr);

// De-registrieren des Speichers auf dem Host

38

}

39

```

**Abbildung 4.2:** Überlagerung von Berechnungen mittels CUDA-Streams Quelle: Selbst erstellt

### 4.3 Registrierter Speicher

Wenn Daten vom Host zum Device kopiert werden, werden diese zunächst in den Hauptspeicher (RAM) des Hosts geladen und dort in CUDA registriert. Erst nachdem die Daten registriert sind, können diese auf das Device kopiert werden. Wenn Daten an einer Speicherstelle mehrfach vom Host auf das Device kopiert werden, so ist es sinnvoll den Speicher manuell in CUDA zu registrieren. Das hat zur Folge, dass die Daten an der registrierten Speicherstelle unverzüglich auf das Device kopiert werden können.

In Listing 4.3 wird in Zeile sieben der Speicherbereich des zu kopierenden Arrays auf dem Host registriert. Nachdem das Array auf das Device kopiert wurde, wird der registrierte Speicher in Zeile 23 wieder de-registriert.

### 4.4 Multiple Grafikkarten

CUDA ermöglicht es, mehrere Devices gleichzeitig zu koordinieren. Die dazu notwendige Funktion wird in Listing 4.3, in Zeile zwei verwendet. Durch den Aufruf der Funktion cudaSetDevice werden alle nachfolgenden Operationen im Kontext des Device mit Index device\_id ausgeführt.

Jedes Device verfügt über einen eigenen VRAM, sowie eigene SMs. Dadurch tragen mehrere Devices dazu bei, den Grad der parallelen Ausführung zusätzlich zu erhöhen. Noch wichtiger im Kontext dieser Arbeit ist jedoch, dass mehrere Devices gemeinsam über einen größeren VRAM verfügen, als ein einzelnes Device.

Wenn Funktionen oder Kernels im Kontext eines Device aufgerufen werden, muss darauf geachtet werden, dass die referenzierten Speicheradressen und CUDA-Streams ebenfalls zum Kontext des Devices gehören. Ansonsten würde ein Device dazu aufgefordert werden auf einer Speicheradresse zu operieren, auf den es keinen Zugriff hat.

## 5 Implementierung

Im Rahmen dieser Arbeit wurde der CG-Algorithmus in fünf Versionen implementiert. Diese Versionen sind:

- 1. Eine sequenzielle Implementierung des CG-Algorithmus

- 2. Eine Implementierung für Mehrkernprozessoren

- 3. Eine Implementierung, bei der jede Berechnung maximal einen vorgegebenen Speicherplatz in Anspruch nimmt

- 4. Eine Implementierung für eine Graphics Processing Unit (GPU)

- 5. Eine Implementierung für mehrere GPUs

Die Einschränkung des Speicherplatzes, die für die dritte Implementierung gilt, gilt auf ähnliche Weise für die vierte und fünfte Implementierung. Der Grafikspeicher (VRAM), der einer GPU zur Verfügung steht ist für gewöhnlich deutlich kleiner als der Hauptspeicher (RAM), der einer CPU zur Verfügung steht. Deshalb sind Implementierungen vier und fünf an den VRAM der Grafikkarte gebunden, auf der gerechnet wird.

Für die Implementierungen wurden C++ Templates verwendet, sodass sowohl mit einfacher, als auch mit doppelter Genauigkeit gerechnet werden kann. Der Datentyp real\_type ersetzt in den Templates die Datentypen float und double.

Im Folgenden wird zunächst die Struktur des CG-Algorithmus gezeigt, die die fünf CG-Implementierungen folgen. Danach wird jede der Implementierungen in einem eigenen Abschnitt vorgestellt. Zuletzt wird kurz darauf eingegangen, wie Lineare Gleichungssysteme (LGS) zum Testen und sammeln der Laufzeiten generiert wurden.

## 5.1 Allgemeine CG-Struktur

In Algorithmus 5.1 ist die allgemeine Struktur des CG-Algorithmus zu sehen, an der sich jede der Implementierungen orientiert.

Algorithmus 5.1 basiert auf der CG-Variante von Shewchuk et al. aus [She+94], die bereits in Kapitel 3 vorgestellt wurde. Die für die Implementierung verwendete, angepasste Variante unterscheidet sich jedoch in Bezug auf den Toleranzparameter  $\epsilon$ .

#### Algorithmus 5.1 Allgemeine Struktur der CG-Implementierungen

```

1: procedure CG-Algorithmus(A, b, x, \epsilon, i_{max})

x \leftarrow (0, ..., 0)^T

2:

// Eigentlich r \leftarrow b - Ax, aber Ax = 0

r \leftarrow b

3:

r\_r \leftarrow r^T r

// Berechne r^T r immer mit r

4:

d \leftarrow r

5:

i \leftarrow 0

6:

while i < i_{max} do

// Abbruch nach maximal i_{max} Iterationen

7:

A\_d \leftarrow Ad

// Berechnen von Ad zum Beginn der Schleife

8:

\alpha \leftarrow \frac{r\_r}{d^T A\_d}

9:

x \leftarrow x + \alpha d

10:

\beta \leftarrow r \ r

// Speichern des alten Wertes von r_r

11:

if i \% 32 \neq 0 then

12:

r \leftarrow r - \alpha A_{\underline{\phantom{A}}} d

/\!/ implizites Berechnen von r

13:

r r \leftarrow r^T r

14:

end if

15:

if i \% 32 = 0 or \sqrt{r_r} < \epsilon then

16:

r \leftarrow b - Ax

// explizites Berechnen von r

17:

r\_r \leftarrow r^T r

18:

if \sqrt{r_r} < \epsilon then

19:

break while

20:

end if

21:

end if

22:

\beta \leftarrow \frac{r_- r}{\beta}

//\beta enthält hier den alten Wert von r_r

23:

d \leftarrow r + \beta d

24:

i \leftarrow i + 1

25:

end while

26:

27: end procedure

```

In der Beispielimplementierung aus Shewchuk et al. [She+94] wurde sich für eine relativen Toleranzparameter  $\epsilon$  entschieden, der mit der Norm des initialen Residuums  $||r_0||$  multipliziert wird. Da das initiale Residuum  $r_0$  vom initialen Fehler  $e_0$  und damit vom willkürlich gewählten initialen Suchpunkt  $x_0$  abhängt, ist die resultierende Toleranz ebenso willkürlich. Aus diesem Grund wird in dieser Arbeit ein absoluter Toleranzparameter verwendet.

Ein weiterer Unterschied ist, dass Algorithmus 5.1 nicht direkt terminiert, wenn das implizite Residuum die Toleranz  $\epsilon$  unterschreitet. In diesem Fall wird, anders als in Algorithmus 3.1, zunächst das explizite Residuum berechnet und danach erneut geprüft, ob die Toleranz  $\epsilon$  unterschritten wurde. Wie in Zeile 19 in Algorithmus 5.1 zu sehen, terminiert der Algorithmus erst, nachdem diese Bedingung erfüllt ist.

In Algorithmus 5.1 sind skalare Operationen, Vektor-Vektor-Operationen, sowie Matrix-Vektor-Multiplikationen vertreten. Die skalaren Operationen der Zeilen 6, 7, 11, 12, 16, 19, 23 und

# **Listing 5.1** Auszug aus der sequenziellen CG-Implementierung: Explizite Berechnung des Residuums

```

// calculate actual residual (r = b - Ax)

std::memset(residual_r.data(), 0, order * sizeof(real_type));

for (size_t ii = 0; ii < order; ii += MATRIX_BLOCKING_SIZE) {</pre>

for (size_t jj = 0; jj < order; jj += MATRIX_BLOCKING_SIZE) {</pre>

for (size_t i = 0; i < MATRIX_BLOCKING_SIZE \&\& ii + i < order; i++) {

real_type Ax_i = 0.0;

for (size_t j = 0; j < MATRIX_BLOCKING_SIZE \&\& jj + j < order; <math>j++) {

Ax_i += matrix_A[(ii + i) * order + jj + j] * search_point_x[jj + j];

residual_r[ii + i] += Ax_i;

10

}

11

}

12

}

13

product_r_r = 0.0;

for (size_t i = 0; i < order; i++) {</pre>

15

residual_r[i] = vector_b[i] - residual_r[i];

16

product_r_r += residual_r[i] * residual_r[i];

17

}

```

25 werden in allen Implementierungen direkt auf der CPU ausgeführt. Die einzelnen Implementierungen unterscheiden sich in ihrer Umsetzung der Matrix-Vektor-Multiplikationen in Zeilen acht und 17, sowie der Vektor-Vektor-Operationen der übrigen Zeilen.

## 5.2 Sequenzielle Implementierung

Die erste Implementierung des CG-Verfahrens ist sequenziell. Die Matrix-Vektor-Multiplikationen und Vektor-Vektor-Operationen aus Algorithmus 5.1 werden auf einem Einzelkernprozessor (engl. Single-Core CPU) ausgeführt, zusammen mit den skalaren Operationen.

Listing 5.1 zeigt einen Auszug aus der sequenziellen CG-Implementierung, in dem das Residuum mit der Formel r=b-Ax explizit berechnet wird. Von Zeile zwei bis 13 wird das Matrix-Vektor-Produkt Ax ausgeführt und im Vektor residual\_r gespeichert. Anschließend wird von Zeile 14 bis 18 das Residuum r=b-Ax und dessen quadratische Norm  $r^Tr$  berechnet.

In der sequenziellen Implementierung werden die Matrix-Vektor-Multiplikation block-weise ausgeführt. In Listing 5.1 wird initial, in Zeile zwei der Vektor residual\_r auf 0 gesetzt. Die beiden äußeren Schleifen in Zeile drei und vier iterieren über die Teilmatrizen der Matrix matrix\_A. Im Inneren wird von Zeile fünf bis Zeile elf eine Matrix-Vektor-Multiplikation auf den Teilmatrizen ausgeführt und zum Ergebnis addiert.

Unterschiedliche Vektor-Vektor-Operationen werden in der sequenziellen Implementierung nach Möglichkeit in eine Schleife zusammengefasst. In Listing 5.1 wird in von Zeile 15 bis

## **Listing 5.2** Auszug aus der Mehrkernprozessor Implementierung: Explizite Berechnung des Residuums

```

product_r_r = 0.0;

// calculate actual residual (r = b - Ax)

#pragma omp parallel for reduction(+ : product_r_r)

for (size_t i = 0; i < order; i++) {

real_type Ax_i = 0.0;

for (size_t j = 0; j < order; j++) {

Ax_i += matrix_A[i * order + j] * search_point_x[j];

}

residual_r[i] = vector_b[i] - Ax_i;

product_r_r += residual_r[i] * residual_r[i];

}</pre>

```

Zeile 18, in der selben Schleife, in der das Residuum berechnet wird, dessen quadratische Norm  $r^Tr$  berechnet.

## 5.3 Mehrkernprozessor Implementierung

In diesem Abschnitt wird die Implementierung für Mehrkernprozessoren vorgestellt. Um die zusätzlichen Kerne solcher Prozessoren auszureizen, verwendet diese CG-Implementierung mehrere Threads. OpenMP [Ope15] wird verwendet, um Threads zu erzeugen und zu koordinieren.

Für eine Schleife wurde die Compileranweisung #pragma omp parallel for verwendet, um für diese Schleife mehrere Threads zu starten und die Berechnung innerhalb der Schleife auf diese Threads aufzuteilen.

Falls in der parallel ausgeführten Schleife eine Summe berechnet wird, z.B. beim Skalarprodukt zweier Vektoren, so wird die Klausel reduction (+ : var) hinzugefügt, um die Teilergebnisse der einzelnen Threads effizient in der Variable var zu summieren.

In dieser Implementierung konnten die Matrix-Vektor-Multiplikationen nicht durch blockweises Berechnen beschleunigt werden. Die Matrix-Vektor-Multiplikationen werden Zeilenweise auf die Threads unterteilt, sodass jeder Thread eine Menge von Skalarprodukten berechnet. Zudem, da kein Cache effizientes Berechnen mehr praktiziert wird, werden alle Arten von Schleifen zusammengefasst, wenn dies möglich ist. In Listing 5.2 wird das Residuum explizit berechnet. Hier werden Schleifen für die Berechnung des Matrix-Vektor-Produkts Ax und des Residuums r=b-Ax zusammengefasst.

**Listing 5.3** Auszug aus der CPU-Implementierung mit Speicherbegrenzung: Explizite Berechnung des Residuums

```

product_r_r = 0.0;

// calculate actual residual (r = b - Ax)

for (size_t ii = 0; ii < order; ii += matrix_block_size) {</pre>

const size_t block_size_i = std::min(order - ii, matrix_block_size);

std::memset(&residual_r[ii], 0, block_size_i * sizeof(real_type));

for (size_t jj = 0; jj < order; jj += matrix_block_size) {</pre>

#pragma omp parallel for

for (size_t i = 0; i < block_size_i; i++) {</pre>

real_type Ax_i = 0.0;

10

for (size_t j = 0; j < matrix_block_size && jj + j < order; <math>j++) {

11

Ax_i += matrix_A[(ii + i) * order + jj + j] * search_point_x[jj + j];

12

13

residual_r[ii + i] += Ax_i;

14

}

15

}

16

17

}

for (size_t ii = 0; ii < order; ii += space_for_rt / 2) {</pre>

const size_t block_size = std::min(order - ii, space_for_rt / 2);

20

#pragma omp parallel for reduction(+ : product_r_r)

21

for (size_t i = 0; i < block_size; i++) {</pre>

22

23

residual_r[ii + i] = vector_b[ii + i] - residual_r[ii + i];

product_r_r += residual_r[ii + i] * residual_r[ii + i];

24

}

25

}

```

## 5.4 CPU-Implementierung mit Speicherbegrenzung

In dieser Implementierung ist darauf zu achten, dass jede parallele Berechnung maximal einen vorgegebenen Speicherplatz in Anspruch nimmt. Um das zu bewerkstelligen werden Matrix-Vektor-Multiplikationen und Vektor-Vektor-Operationen in Blöcken berechnet.

Listing 5.3 zeigt einen Auszug aus der Implementierung, in dem das Residuum des aktuellen Suchpunktes explizit berechnet wird. Von Zeile drei bis 17 wird das Produkt Ax berechnet. Die beiden äußeren Schleifen in Zeile drei und sechs iterieren über die Teilmatrizen der Matrix matrix\_A. Für jede Teilmatrix wird von Zeile acht bis 15 eine Matrix-Vektor-Multiplikationen parallel ausgefüht.

Mit dem Produkt Ax wird von Zeile 18 bis 26 das Residuum r=b-Ax und das Produkt  $||r||^2$  berechnet. Hier wird die parallele Berechnung in den Zeilen 21 bis 25 ebenfalls mehrfach ausgefüht.

Die Größen, die zum Unterteilen der Schleifen verwendet werden, sind matrix\_block\_size und space\_for\_rt. In Listing 5.4 ist zu sehen, wie die Größen zum Unterteilen der Schleifen

# **Listing 5.4** Auszug aus der CPU-Implementierung mit Speicherbegrenzung: Herleitung der Blockgrößen

```

const size_t space_for_rt = l3_cache_size / sizeof(real_type);

const size_t cache_lines_matrix = (sqrt(space_for_rt) - 1) / l3_cache_line_size;

const size_t matrix_block_size = cache_lines_matrix * l3_cache_line_size;

```

berechnet werden. Der Speicherplatz, den die parallelen Berechnungen nicht überschreiten dürfen ist der L3-Cache des Prozessors.

Die Größe space\_for\_rt sagt aus, wie viele Variablen vom Typ real\_type in den L3-Cache passen. Daran kann direkt die Blockgröße beim Rechnen mit Vektoren hergeleitet werden. In Listing 5.3, in Zeile 21 bis 25, sind zwei Vektoren Bestandteil der parallelen Berechnung. Deshalb wird in Zeile 19 die Blockgröße so gewählt, dass zwei Subvektoren den L3-Cache nicht überschreiten. Hier wird darauf spekuliert, dass die Anzahl der Cache-Zeilen im L3-Cache durch zwei teilbar ist, sodass der Cache auf die beiden Subvektoren aufgeteilt werden kann.

Die Größe matrix\_block\_size entspricht der Quadratwurzel der Elemente, die im Cache Platz finden, minus eins, abgerundet auf das größte Vielfache einer L3-Cache-Zeilengröße.

Die Idee dahinter ist, dass für eine Matrix-Vektor-Multiplikation  $n^2$  Elemente für die Matrix, sowie 2n Elemente für den Vektor Platz im Speicher benötigen. Die Elemente einer Teilmatrix sind im RAM nicht komplett linear angeordnet, sondern nur zeilenweise linear. Da eine Cache-Zeile nur linear angeordneten Speicher zwischenspeichern kann, muss der Parameter matrix\_block\_size abschließend auf das größte Vielfache einer L3-Cache-Zeilengröße abgerundet werden.

## 5.5 GPU-Implementierung

Bei der GPU-Implementierung des CG-Verfahrens werden alle Vektor-Vektor- und Matrix-Vektor-Operationen auf der GPU berechnet. Für große LGS reicht der VRAM einer Grafikkarte nicht aus, um die Daten für alle Berechnungen zeitgleich zu halten. So benötigt z.B. allein die Matrix eines LGS der Ordnung 75000 über 41GB Speicherplatz. Die im Rahmen dieser Arbeit verwendete Server-Grafikkarte NVIDIA A100-SXM4 [NVIa] besitzt einen VRAM von 40GB und kann damit die Matrix nicht im Speicher halten. Aus diesem Grund müssen während der Ausführung von Algorithmus 5.1 mehrfach Daten zum und vom Device kopiert werden.

Vor Beginn der Ausführung muss Speicher auf dem Device allokiert werden, sodass die Daten kopiert werden können. Zusätzlich, um das Kopieren der Daten effizienter zu gestalten, werden sämtliche zu kopierenden Daten im Speicher des Hosts registriert (siehe Abschnitt 4.3).

Im Folgenden wird zunächst gezeigt, wie der VRAM auf der Grafikkarte eingeteilt wird. Anschließend wird im Detail erklärt, wie die Matrix-Vektor-Multiplikation auf dem Device

Abbildung 5.1: Speichereinteilung des VRAM einer Grafikkarte

ausgeführt wird. Zuletzt wird darauf eingegangen, wie Vektor-Vektor-Operationen auf dem Device ausgeführt werden.

## 5.5.1 Speichereinteilung des VRAM

In Abbildung 5.1 ist zu sehen, wie der VRAM der Grafikkarte eingeteilt wird. Der grüne Block d\_s repräsentiert einen Speicherbereich für einen einzelnen Wert, ein Skalar. Die Speicherbereiche, die von den blauen Blöcken repräsentiert werden, sind für Vektoren unterschiedlicher Länge vorgesehen. d\_x bietet dabei Platz für einen Vektor, dessen Länge n der Ordnung des zu lösenden LGS entspricht. In den Speicherbereichen d\_b 1 und 2 finden jeweils Vektoren der Länge m Platz. Die violetten Blöcke d\_A 1 und 2 repräsentieren jeweils eine Speicherbereiche für eine  $(m \times n)$ -Matrix.

Anhand von Abbildung 5.1 ist leicht zu erkennen, dass folgende Ungleichung für den VRAM der Grafikkarte gelten muss:

$$VRAM \ge (2m+1)(n+1)e$$

Hier ist die Konstante e ist der Speicherbedarf eines Elements. Für doppelte Präzision gilt e=8 Bytes. In der GPU-Implementierung wurde die Größe m wie folgt bestimmt:

$$mb = \frac{(0.95 \cdot VRAM) - (n+1)e}{2(n+1)}$$

$$m = 128 \cdot \left| \frac{mb}{128} \right| \cdot \frac{1}{e}$$

In der Berechnung werden nur 95% des VRAMs der Grafikkarte verwendet. 5% des VRAM werden nicht allokiert, sodass darin der Code der Kernels geladen werden kann. Würde der Speicher vollständig allokiert werden, so könnten im Anschluss keine Kernels ausgeführt werden [NVI23]. Um auf den Wert m zu schließen wird der Wert mb auf das größte vielfache von 128 abgerundet.

#### 5.5.2 Matrix-Vektor-Multiplikation

Die Berechnung des Matrix-Vektor-Produkts b = Ax erfolgt über mehrere Teilrechnungen  $b_i = A_i x$ . Hier wird  $A_i$ , eine  $(m \times n)$ -Teilmatrix mit dem vollständigen Eingabevektor x multipliziert. Ergebnis der Teilrechnung ist ein Teil des Ergebnisvektors  $b_i$  mit Länge m.

Für eine Teilrechnung wird zunächst die  $(m \times n)$ -Teilmatrix in einen der Speicherbereiche d\_A 1 oder 2 kopiert. Anschließend wird der entsprechende Speicherbereich des Ergebnisvektors d\_b 1 oder 2 auf 0 gesetzt. Nun wird der Kernel aufgerufen, der die Matrix-Vektor-Multiplikation ausführt. Im letzten Schritt wird das Ergebnis auf den Host kopiert.

Listing 5.5 zeigt die Host-Funktion, der die Matrix-Vektor-Multiplikation koordiniert. Im Folgenden wird erklärt, welche Optimierungen auf Host-Seite verwendet werden und wie sich diese auf den Code des Hosts auswirken.

Überlagerung der Teilrechnungen Die zeitaufwändigste Operation einer Teilrechnung ist das Kopieren der  $(m \times n)$ -Teilmatrix auf das Device. Für eine optimale Auslastung der Hardware werden die einzelnen Teilrechnungen so überlagert, dass ununterbrochen neue Teilmatrizen auf das Device kopiert werden können. Während mit der Teilmatrix  $A_i$  in einem der Speicherbereiche gerechnet wird, wird die nächste Teilmatrix  $A_{i+1}$  auf das Device kopiert. Aus diesem Grund sind die Speicherbereiche für Teilmatrizen und Teilergebnisse doppelt im VRAM vorhanden. Analog zu den Speicherstellen werden zwei CUDA-Streams für das Device auf dem Host erstellt.

#### **Listing 5.5** Auszug aus der GPU-Implementierung:

Host-Funktion zum Berechnen des Matrix-Vektor-Produkts

```

void gpu_cg_re<real_type>::matrix_vector_product(const real_type* matrix,

const real_type* vector_in, real_type* vector_out) {

const dim3 thread_block_dim(THREAD_BLOCK_SIZE, 1);

// which submatrices are precopied and at which memory-space

size_t stream_index = copied_submatrix_stream;

size_t chunk_shift = copied_submatrix_index;

cudaMemcpy(d_x, vector_in, order * sizeof(real_type), cudaMemcpyHostToDevice);

\label{eq:continuous_num} \textbf{for } ( \mbox{\sc size\_t} \ \mbox{\sc chunk\_num} \ = \ \theta \mbox{; } \mbox{\sc chunk\_num} \ < \ \mbox{\sc num\_chunks} \mbox{; } \mbox{\sc chunk\_num} \mbox{++}) \ \{

const size_t chunk_offset = ((chunk_num + chunk_shift) % num_chunks) * chunk_size;

const size_t this_chunk_size = std::min(order - chunk_offset, chunk_size);

11

const dim3 grid_dim((order - 1) / THREAD_BLOCK_SIZE + 1,

12

(this_chunk_size - 1) / THREAD_BLOCK_SIZE + 1);

13

// first (NUM_CUDA_STREAMS) submatrices are precopied

15

if (chunk_num >= NUM_CUDA_STREAMS) {

cudaMemcpy2DAsync(d_A[stream_index], chunk_size * sizeof(real_type),

&matrix[chunk_offset], order * sizeof(real_type),

18

this_chunk_size * sizeof(real_type), order,

19

cudaMemcpyHostToDevice, streams[stream_index]);

20

copied_submatrix_stream = (copied_submatrix_stream + 1) % NUM_CUDA_STREAMS;

21

copied_submatrix_index = (copied_submatrix_index + 1) % num_chunks;

23

cudaMemsetAsync(d_b[stream_index], 0, this_chunk_size * sizeof(real_type),

streams[stream_index]);

d_matrix_vector_product_col<<<grid_dim, thread_block_dim,</pre>

0, streams[stream_index]>>>(d_A[stream_index], d_x, d_b[stream_index],

27

chunk_size, order, this_chunk_size);

28

cudaMemcpyAsync(&vector_out[chunk_offset], d_b[stream_index],

this_chunk_size * sizeof(real_type), cudaMemcpyDeviceToHost,

streams[stream_index]);

31

stream_index = (stream_index + 1) % NUM_CUDA_STREAMS;

34

35

cudaDeviceSynchronize();

36

}

```

In Listing 5.5 entspricht jeder Schleifendurchlauf einer Teilrechnung. Alle Operationen der Teilrechnung werden asynchron ausgeführt und in den selben CUDA-Stream eingereiht. Der selbe Index, der zum Anwählen des CUDA-Streams verwendet wird, wird auch verwendet, um die Speicherstellen d\_A und d\_b auf dem Device zu referenzieren.

Am Ende der Schleife, in Zeile 29 wird der stream\_index angepasst. Dadurch wird die nächste Teilrechnung in den anderen CUDA-Stream eingereiht wird und verwendet die anderen Speicherstellen d\_A und d\_b auf dem Device. So kommt jedem CUDA-Streams ein eigener Speicherbereich zum Verwalten zu.

**Kopieren von transponierten Teilmatrizen** Beim Rechnen mit Matrizen auf der GPU ist es für effizientere Speicherzugriffe sinnvoll, dass eine Matrix spaltenweise im Speicher des Devices hinterlegt ist. Um eine Teilmatrix  $A_i$  spaltenweise vom Host auf das Device zu kopieren, wird die Symmetrie der Matrix A ausgenutzt.

Anstatt eine  $(m \times n)$ -Teilmatrix  $A_i$  zu kopieren, wird ihr transponiertes  $A_i$ ' auf das Device kopiert. Da  $A_i$ ' zeilenweise im Speicher hinterlegt ist, entspricht das der spaltenweisen Darstellung von  $A_i$ .

Das Kopieren der Teilmatrix wird in Listing 5.5 von Zeile 16 bis 19 in Auftrag gegeben. Der Funktion cudaMemcpy2dAsync wird hier die transponierte  $(n \times m)$ -Teilmatrix  $A_i$ ' referenziert.

Wiederverwendung der kopierten Teilmatrizen Die in Algorithmus 5.1 vertretenen Matrix-Vektor-Multiplikationen erfolgen allesamt mit der selben Matrix A. Nachdem eine Matrix-Vektor-Multiplikation vollständig auf dem Device ausgeführt wurde, verbleiben die zuletzt kopierten Teilmatrizen noch dort. Die nächste Matrix-Vektor-Multiplikation wird mit den noch auf dem Device befindlichen Teilmatrizen begonnen, sodass initial keine Teilmatrix kopiert werden muss.

Vor Ausführung der ersten Matrix-Vektor-Multiplikation müssen dazu die ersten beiden Teilmatrizen auf das Device kopiert werden. In Listing 5.5 befinden sich zwei Teilmatrizen  $A_k$  und  $A_{k+1}$  bereits auf dem Device. Der kleinere Index k der beiden Teilmatrizen wird in der Variable copied\_submatrix\_index hinterlegt. Die Variable copied\_submatrix\_stream gibt an, an welchem Speicherplatz sich Teilmatrix mit dem kleineren Index befindet.

In Zeile fünf wird initial der CUDA-Stream ausgewählt, in dessen Speicherbereich sich die Teilmatrix mit Index k befindet. Der Index der folgenden Teilberechnungen wird um den Wert von k verschoben. In Zeile neun wird der verschobene Offset entsprechend berechnet.

Das Kopieren einer neuen Teilmatrix in Zeile 16 bis 19 wird für die ersten beiden Schleifendurchläufe ausgesetzt, da sich zwei Teilmatrizen bereits auf dem Device befinden. Wird jedoch eine neue Teilmatrix auf das Device kopiert, so werden die Variablen copied\_submatrix\_index und copied\_submatrix\_stream dementsprechend angepasst.

**Listing 5.6** Auszug aus der GPU-Implementierung:

Kernel zum Berechnen des Matrix-Vektor-Produkts

```

__global__ void d_matrix_vector_product(

const real_type* d_A, const real_type* d_x, real_type* d_b,

2

const kernel_index_type pitch,

const kernel_index_type width,

const kernel_index_type height) {

const kernel_index_type block_offset_x = blockIdx.x * THREAD_BLOCK_SIZE;

const kernel_index_type block_offset_y = blockIdx.y * THREAD_BLOCK_SIZE;

__shared__ real_type local_x[THREAD_BLOCK_SIZE];

// boundary check

10

if (block_offset_x + threadIdx.x < width) {</pre>

local_x[threadIdx.x] = d_x[block_offset_x + threadIdx.x];

11

12

__syncthreads();

13

14

if (block_offset_y + threadIdx.x < height) {</pre>

// boundary check

15

real_type b_i = 0.0;

16

for (kernel_index_type i = 0; i < THREAD_BLOCK_SIZE; i++) {</pre>

17

if (block_offset_x + i < width) {</pre>

// boundary check

18

b_i += d_A[(block_offset_x + i) * pitch + block_offset_y + threadIdx.x] *

19

local_x[i];

20

}

21

}

atomicAdd(&d_b[block_offset_y + threadIdx.x], b_i);

23

}

24

}

25

```

#### Kernel der Matrix-Vektor-Multiplikation

In Listing 5.6 ist der Kernel zu sehen, der in der GPU-Implementierung zum Berechnen des Matrix-Vektor-Produkts verwendet wird. Seine Funktionsweise wird im Folgenden erklärt.

Dem Kernel wird die Speicheradresse der Matrix A, des Eingabevektors x und des Ergebnisvektors b mit den Zeigern  $d_A$ ,  $d_x$  und  $d_b$  übergeben. Die Matrix A ist dabei spaltenweise im Speicher hinterlegt.

Der Übergabeparameter pitch gibt den Abstand zweier aufeinanderfolgender Spalten der Matrix A an. Mithilfe von pitch werden die Elemente in A adressiert. Die Parameter width und height geben die Anzahl der zu multiplizierenden Spalten und Zeilen der Matrix an. Mit ihnen wird mehrfach geprüft, ob sich ein Index noch innerhalb der Grenzen des zulässigen Speichers befindet (engl. boundary checking). Die Grenzprüfungen werden im Text nicht erneut erwähnt, sind aber im Code kommentiert.

Innerhalb eines Thread-Blocks führen t linear angeordnete Threads gemeinsam eine Matrix-Vektor-Multiplikation auf einer  $(t \times t)$ -Teilmatrix aus. Auf die Größe t hat ein Thread Zugriff

über die Konstante THREAD\_BLOCK\_SIZE. Die Zuständigkeit des Thread-Blocks wird in den Zeilen sechs und sieben bestimmt.

**Caching** Für die Ausführung eines Thread-Blocks wird der relevante Teil des Eingabevektors x in shared memory zwischengespeichert. Da die Latenz von shared memory um ein vielfaches geringer ist, als die Latenz von global memory, kann dieses Vorgehen als Caching beschrieben werden.

Ein shared memory Array wird in Zeile neun deklariert, in das in Zeile elf der für den Thread-Block relevante Teil des Eingabevektors x gespeichert wird. Anschließend werden die Threads eines Thread-Blocks in Zeile 13 mit der Anweisung  $\_$ -syncthreads() synchronisiert. So wird garantiert, dass das shared memory Array vollständig befüllt wurde, bevor mit dessen Einträgen gerechnet wird.

**Verschmolzener Speicherzugriff (Coalesced Memory Access)** Von Zeile 15 bis 24 erfolgt die eigentliche Matrix-Vektor-Multiplikation. Die for-Schleifen von Zeile 17 bis 22 summiert die Produkte des zwischengespeicherten Eingabevektors und einer Teilzeile der Matrix in der lokalen Variable b\_i auf. In Zeile 23 wird diese Variable mit der Funktion atomicAdd atomar zum Ergebnisvektor addiert.

Die Indizierung der Matrix in Zeile 19 erfolgt so, dass die Threads in einem Warp im Thread-Block auf Einträge zugreifen, die linear im Speicher angeordnet sind. Mit dieser Indizierung werden mehrere Anfragen auf den global memory zu einem einzelnen Speicherzugriff verschmolzen (coalesced memory access). Zusätzlich wurde der Speicher bei der Allokierung auf 128 Bytes ausgerichtet, sodass bei doppelter Präzision ein Warp nur zwei Speicherzugriffe benötigt.

### 5.5.3 Vektor-Vektor-Operationen