# Scalable Deterministic Logic Built-In Self-Test

Von der Fakultät Informatik, Elektrotechnik und Informationstechnik der Universität Stuttgart zur Erlangung der Würde eines Doktors der Naturwissenschaften (Dr. rer. nat.) genehmigte Abhandlung

Vorgelegt von

## Valentin Gherman

aus Onești/Rumänien

Hauptberichter:Prof. Dr. rer. nat. H.-J. WunderlichMitberichter:Prof. Dr. rer. nat. W. Anheier

Tag der mündlichen Prüfung: 19. Mai 2006

Institut für Technische Informatik der Universität Stuttgart

2006

## Abstract

The core-based design style of integrated circuits (ICs) helps to manage the development challenges brought by the ever increasing complexity of integrated systems and the ever tighter time-to-market. Nevertheless, test-related problems are still far away from having a unitary and satisfactory solution, especially in the system on a chip (SOC) context.

For the test of ICs two reference approaches are available: external testing and built-in self-test (BIST), out of which a variety of hybrid test strategies are obtained by test resource partitioning (TRP). The final goal is to provide advantageous tradeoffs of the test evaluation indicators like: test development and application cost, hardware overhead, fault coverage, etc.

BIST offers support for in-field, on-line, burn-in and at-speed test that is indispensable for delay fault testing. Moreover, tradeoffs between fault coverage, hardware overhead and test length are possible. External testing is characterized by flexibility, reduced hardware overhead and high fault coverage for a given test length.

Deterministic logic BIST (DLBIST) is an attractive test strategy, since it combines the advantages of deterministic external testing and pseudo-random logic BIST (LBIST). Unfortunately, previously proposed DLBIST methods are unsuited for large ICs, since computation time and memory consumption of the DLBIST synthesis algorithms increase exponentially, or at least cubically, with the circuit size.

In this work, a novel procedure for the development of the so-called *bit-flipping* DLBIST scheme is proposed, which has nearly linear complexity in terms of both computation time and memory consumption. This new method is based on the use of Binary Decision Diagrams (BDDs). The efficiency of the employed algorithms is demonstrated for industrial designs containing up to 2M gates.

The embedded test sequences obtained by mapping deterministic cubes to pseudorandom sequences are also evaluated with respect to the coverage of non-target defects, which are modeled with the help of resistive bridging faults. The experimental results prove that both deterministic cubes and pseudo-random sequences are useful for detecting non-target defects. Moreover, possible tradeoffs between test length, hardware overhead, fault coverage and non-target defect coverage are analyzed.

This work additionally presents the results of extending the bit-flipping DLBIST scheme such that it also supports the transition fault testing besides the stuck-at fault testing. Transition faults model defects which are responsible for the incorrect operation of the core under test (CUT) at the desired speed. The importance of these defects is continuously enhanced by the ever increasing clock rates and integration density of today's circuits. Experimental results obtained for large industrial benchmark designs are reported. No *pure* DLBIST approach for the test of delay faults in circuits with standard scan design has been published so far.

In order to decrease the logic overhead of DLBIST, an innovative way of constructing efficient implementations for the involved Boolean functions (e.g. bit-flipping functions) is presented. A key feature of these functions is their incomplete specification which is based on large *don't care sets* (sets of input assignments for which it does not matter whether they are mapped to '0' or '1'). Reduced ordered Binary Decision Diagrams (ROBDD) are used for representing and manipulating the involved functions and multi-level implementations are obtained based on the use of free BDDs (FBDD). Experimental results show that for all the considered functions, implementations are found with a significant reduction of the gate count as compared to a state-of-the-art multi-level synthesys tool (SIS [Sen92]) or to methods offered by a state-of-the-art BDD package. This performance is due to a reduction of the node count in the corresponding FBDDs and a decrease in the average number of gates needed to implement the FBDD nodes.

The experimental results obtained for large industrial benchmark designs show that DLBIST may be well suited for use in special segments of IC development, like the ones dealing with security chips or hard cores.

## Acknowledgments

First of all, I would like to thank Professor Hans-Joachim Wunderlich who gave me the chance to express myself working towards the accomplishment of this work and who supervised my activity.

I am very grateful to Professor Walter Anheier<sup>1</sup> for his survey of this work.

I wish to express my gratitude to Harald Vranken<sup>2</sup> and Friedich Hapke<sup>3</sup> for their assistance during the completion of my work.

I would also like to mention the precious technical support of Michael Garbers<sup>3</sup>, Michael Wittke<sup>3</sup>, Andreas Glowatz<sup>3</sup>, Rüdiger Solbach<sup>3</sup> and Ralf Reche<sup>3</sup>.

I am also very grateful to all my current and former-colleagues for our discussions and exchange of knowledge, in particular to Arnould Virazel, Abdul-Wahid Hakmi, Gundolf Kiefer, Rainer Dorsch and Yuyi Tang. Thanks go to Nicoleta Pricopi and Karin Angele for their support and comradeship.

I would like to thank Carmen Constantinescu and David Rio Mascarenas for their help and assistance in writing down the manuscript. I am also very thankful to my colleagues Wolfgang Moser, Tobias Bergmann, Alexandra Wiedmann, Hairuo Qiu and Andreas Heinchen for correcting and refining the style of the section written in German.

Finally, I would like to dedicate this work to my family, especially to my mother. I am very grateful to my uncle, Niculae Balan, who proved so much talent and patience in revealing me, since I was a child, the existence and the dynamic of a fascinating Universe.

<sup>&</sup>lt;sup>1</sup> University of Bremen.

<sup>&</sup>lt;sup>2</sup> Philips Research, in Eindhoven.

<sup>&</sup>lt;sup>3</sup> Philips Semiconductors GmbH, in Hamburg.

## Zusammenfassung

*System on a Chip* (SOC) sind komplexe Systeme mit Millionen von Transistoren auf einer einzelnen integrierten Schaltung (engl. *integrated circuit* (IC)). Solche ICs enthalten in der Regel verschiedene Komponenten und Technologien, wie beispielsweise Speicher, Prozessoren, anwendungsspezifische Logik, Hochfrequenzund Analogmodule. Um die Kosten der Entwicklung zu reduzieren, werden immer häufiger vorentworfene Funktionsblöcke verwendet (engl. *core-based design*). Dieser Entwurfsstil stellt eine große Herausforderung an die Testverfahren dar.

Das Hauptziel eines jeden Testverfahrens ist es, einen Kompromiss zwischen den Testkosten und der Testqualität (Produktqualität) zu finden. Wichtige Kriterien für den Test von ICs sind: Testentwicklungskosten, Testapplikationskosten, zusätzlicher Bedarf an Schaltungsfläche, Fehlererfassung, etc.

Zu den Anforderungen, die an die heutigen IC Testverfahren gestellt werden, gehören spezifische Anforderungen, die auf die verschiedenen Typen von Modulen abgestimmt sind. Zudem besteht zunehmender Bedarf an Verzögerungstests, *in-field* und *on-line* Tests.

In den traditionellen Testverfahren werden die ICs normalerweise extern mit speziellen Testautomaten (engl. *automated test equipment* (ATE)) getestet. Die externen Testverfahren zeichnen sich durch hohe Flexibilität, relativ geringen zusätzlichen Bedarf an Schaltungsfläche und hohe Fehlererfassung für eine bestimmte Testlänge aus.

Die zunehmende Komplexität und der wachsende Umfang der Testdaten machen die Durchführung externer Tests immer schwierig. Die Qualität der Fehlererfassung wird durch die Unzugänglichkeit der internen Blöcke verringert. Außerdem ist es sehr teuer, mit ATEs die maximal mögliche Taktfrequenz moderner ICs zu messen. Diese Probleme werden durch die hohe Komponentendichte sowie die Anwendung verschiedener Technologien in der SOC-Fertigung vergrößert, so dass Messmethoden mit externen Testautomaten ungenau, und das ATE selbst sehr teuer wird.

Selbsttestverfahren (engl. *built-in self-test* (BIST)) sind dem oben genannten Verfahren in Bezug auf die erwähnten Problemen überlegen. Mit BIST können *online, in-field, burn-in* und *at-speed* Tests realisiert werden. *In-field* Tests werden für periodische Wartungen verwendet, *burn-in* Tests sind wichtig für die Steigerung der Produktqualität und Zuverlässigkeit und *at-speed* Tests sind notwendig um die Verzögerungsfehler zu finden. Außerdem sind Kompromisse zwischen der erreichten Fehlererfassung, dem zusätzlichen Bedarf an Schaltungsfläche und der Testlänge möglich.

Neben den externen und den Selbsttestverfahren gibt es noch verschiedene Arten von Testverfahren, die auf *test resource partitioning* (TRP) basieren.

Deterministic logic BIST (DLBIST) ist eine sehr attraktive Teststrategie, weil sie die Vorteile von deterministischen externen Testverfahren und pseudozufälligen logic BIST kombiniert. Die bisher vorgeschlagenen DLBIST Verfahren können nur bei kleineren Entwürfen angewendet werden, da die Laufzeit und der Speicherbedarf der Hardwaresynthese exponentiell oder wenigstens kubisch mit der Schaltungsgröße steigen.

Es gibt zwei grundlegende DLBIST Verfahren: *store and generate* Verfahren und *test set embedding* Verfahren. Bei dem *store and generate* Verfahren werden die Testmuster in einer komprimierten Form auf dem Chip gespeichert und darauf ein Dekompressionsalgorithmus angewendet. Bekanntere Beispiele dieser DLBIST Methode basieren auf Kodierung durch rückgekoppelte Schieberegister (engl. *LFSR*) [Koe91], Multipolynom Reinitialisierung [Hel92] [Hel95] und Faltender Zähler (engl. *folding counter*) [Lia02].

Bei *Test set embedding* Verfahren werden pseudozufallsgenerierte Muster durch deterministische Muster ergänzt. Bekannte *test set embedding* Verfahren sind die *bit-flipping* [Kie00][Wun96][Kie97][Kie98] und *bit-fixing* [Tou96] Verfahren.

Bei diesen beiden DLBIST Verfahren werden Testmustergeneratoren eingesetzt, die eine gute Fehlererfassung ermöglichen. Die Besonderheit dieser Testmustergeneratoren ist ein Logikmodul, das eine *bit-flipping* Funktion (BFF), beziehungsweise *bit-fixing* Funktion (BFX), durchführt. Die Implementierung dieser Testmustergeneratoren umfasst zwei Schritte: (1) die Abbildung einer Reihe deterministischer Testmuster zu einer Folge von Pseudozufalltestmustern und (2) die Synthese des Logikmoduls, welches die Abbildung durchführt.

In dieser Arbeit wird ein neues Verfahren für den Aufbau der *bit-flipping* DLBIST Hardware vorgeschlagen. Die BFF beschreibt das Einbetten von deterministischen Testmustern zu einer pseudozufälligen Testfolge, die durch einen LFSR und eventuell einen Phasenschieber (engl. *phase shifter*) erzeugt wird. Die Suche nach einem effizienten deterministischen Testmuster-Einbettungsverfahren mit geringem zusätzlichem Bedarf an Schaltungsfläche ist eine schwierige Aufgabe.

Ein Beitrag dieser Arbeit ist eine skalierbare Lösung, sowohl für die Abbildung von deterministischen Testmustern (d.h. die Generation von BFF), als auch für die Logiksynthese der resultierenden BFF [Ghe04]. Ein ATPG Werkzeug wird verwendet, um deterministische Testmuster für alle Fehler zu erzeugen, die nicht durch die pseudozufällige Testfolge entdeckt werden. Diese deterministischen Testmuster enthalten eine große Zahl nicht spezifizierter Bits (engl. *don't care (DC) bits)*. Ein Pseudozufallstestmuster wird jedem dieser deterministischen Testmuster zugeteilt, so dass die Größe der resultierenden BFF minimiert wird. In Anbetracht eines deterministischen Testmusters werden nur diejenigen Pseudozufallstestmuster untersucht, die eine minimale Zahl von unpassenden (engl. *conflicting*) Bits enthalten. Um weiter die Abbildung von Testmustern zu optimieren, wird eine Kombination von folgenden Maßnahmen verwendet:

- Minimierung der Taktzyklen, die sowohl zusammenpassende (engl. *matching*) als auch unpassende Bits enthalten. Dadurch wird versucht den Logikanteil, der bei der BFF Implementierungen für unterschiedliche Prüfpfade gemeinsam benutzt wird, zu maximieren.

- Minimierung der Zahl von Prüfpfaden, die sowohl zusammenpassende als auch unpassende Bits pro eingebettetem Testmuster enthalten. Dies erhöht die Optimierungsmöglichkeiten für die BFF Implementierung jedes Prüfpfades.

Das neue Verfahren stützt sich auf die Effizienz und die Kompaktheit der BDDbasierten Funktionsdarstellung und hat eine beinahe lineare Komplexität in Bezug auf Laufzeit und Speicherbedarf.

Die Effizienz des neuen Verfahrens wird für industrielle Schaltungen bis zu einer Größe von 2 Millionen Gattern nachgewiesen. Mit der neuen Einbettungsmethode sind Verbesserungen mehrerer Größenordnungen, verglichen mit den vorherigen Verfahren [Wun96] sowohl in Bezug auf den Laufzeitbedarf, als auch in Bezug auf den Speicherbedarf, erreichbar. Die neue DLBIST Hardware-Synthese hat jetzt denselben Laufzeit- und Speicherverbrauch wie die anderen benötigten Verfahrensschritte, ATPG und Fehlersimulation. Die Laufzeitverbesserungen können auch dazu verwendet werden, um noch bessere Lösungen in Bezug auf den zusätzlichen Bedarf an Schaltungsfläche und Fehlererfassung zu erhalten.

Ein anderer Beitrag dieser Arbeit ist eine Studie zur Wirksamkeit des *bit-flipping* DLBIST im Test von nicht modellierten Defekten [Eng05]. Die widerstandsbehafteten Brückenfehler (engl. *resistive bridging faults*) wurden verwendet, um nicht modellierte Defekte zu simulieren. Experimentelle Ergebnisse zeigen, dass sowohl deterministische als auch pseudozufällige Testmuster nützlich sind, um nicht modellierte Defekte zu testen. Außerdem werden mögliche Kompromisse zwischen der Testlänge, zusätzlichem Bedarf an Schaltungsfläche, Fehlererfassung und Erfassung der nicht modellierten Defekte analysiert. Es zeigt sich, dass durch die Erhöhung der Anzahl von Testmustern die Defekterfassung erhöht und der zusätzliche Bedarf an Schaltungsfläche bedeutend reduziert wird. Das vergrößert die Attraktivität der vorgeschlagenen DLBIST Architektur und reduziert den Bedarf an teuren ATEs.

Diese Arbeit enthält auch eine Erweiterung der entwickelten *bit-flipping* DLBIST Architektur, so dass neben Haftfehlern auch Übergangsfehler testbar werden [Ghe05]. Die Übergangsfehler (engl. *transition faults*) sind eine Art von Verzögerungsfehler und modellieren Defekte, die für eine nicht funktioniernde Schaltung bei der verwendeten Taktfrequenz verantwortlich sind. Die Bedeutung dieser Defekte wird durch die jeweils zunehmende Taktrate und Integrationsdichte heutiger Schaltungen ständig erhöht.

Es ist bis jetzt kein DLBIST Verfahren für die Prüfung der Übergangsfehler veröffentlicht worden. Die Besonderheit der Tests von Übergangs- und allgemeinen Verzögerungsfehlern besteht in der Notwendigkeit, Paare von Testmustern und nicht einzelne Testmuster, wie im Falle von Haftfehlern, anzuwenden. Es wird in diesem Verfahren das erste Testmuster jedes Paares genau wie im Fall von Haftfehler-Test erzeugt, und die Schaltungsantwort auf das erste Testmuster wird als zweites Testmuster verwendet (engl. *functional justification*).

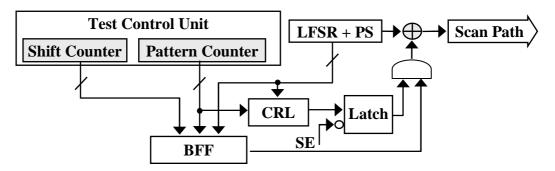

Da bei diesem Test Testmusterpaare verlangt werden, ist die zufällige Fehlererfassung bedeutend kleiner als für Haftfehler. Um das Einbetten von Testmustern effizienter zu machen, wird ein spezielles Modul, *correction logic* (CRL) genannt, eingeführt. Das CRL-Modul wird genau wie das BFF-Modul synthetisiert. Die Ausgangssignale des CRL-Moduls müssen während der *scan*-Taktzyklen, entsprechend jedem Testmuster, unverändert bleiben. Da sich einige der Eingangssignale während der *scan*-Taktzyklen ändern, werden die Ausgangssignale des CRL-Moduls in einem Flipflop gespeichert. Dieses Flipflop kann nur dann beschrieben werden, wenn ein neues Testmuster in den Prüfpfad gescannt wird. Das Flipflop wird durch das *scan enable*-Signal gesteuert, das benutzt wird, um die *scan*-Flipflops zwischen *scan mode* und *functional mode* zu schalten.

Um die Größe des CRL und BFF zu beschränken, werden die deterministischen Testmuster am Ende der pseudozufälligen Testfolge eingebettet. Die Länge der pseudozufälligen Testfolge, die modifiziert werden kann, ist ein Bruchteil der ganzen Testlänge. Um die Bits in der pseudozufälligen Testfolge davor zu bewahren, gekippt (engl. *flipped*) zu werden, werden die Ausgangssignale des BFF mit der Hilfe eines UND-Gatters pro Prüfpfad auf Null gesetzt.

Die geringere pseudozufällige Testbarkeit von Übergangsfehlern relativ zu den Haftfehlern verlangt bedeutend längere Testmusterfolgen. Diese eignen sich sowohl zum Begrenzen des zusätzlichen Bedarfs an Schaltungsfläche als auch für eine verbesserte Erfassung von modellierten und nicht modellierten Defekten. Experimentelle Ergebnisse für große Industrieschaltungen zeigen mögliche Kompromisse zwischen der Testlänge, zusätzlichem Bedarf an Schaltungsfläche und Fehlererfassung auf.

Ein weiterer Beitrag dieser Arbeit ist ein Logikoptimierungswerkzeug, das verwendet wird, um die Implementierung des BFF zu verbessern. Dieses Logikoptimierungswerkzeug ist besonders zur Implementierung von unregelmäßigen und unvollständig spezifizierten Booleschen Funktionen geeignet. In diesem Fall bedeutet die Unregelmäßigkeit einer Booleschen Funktion, dass ihre Eingaben, deren Abbild '1' ist, zufällig über dem Definitionsraum verteilt sind. Unvollständige Spezifizierung beruht auf Inputs, für die es gleichgültig ist, ob sie auf '0' oder '1' abgebildet werden. Beispiele für diese Art von Funktionen sind: BFF, BFX [Tou96] und die so genannte X-Maskierungsfunktion (XMF) [Tan04]. Alle diese Beispiel-funktionen werden in verschiedenen *test set embedding* Verfahren verwendet.

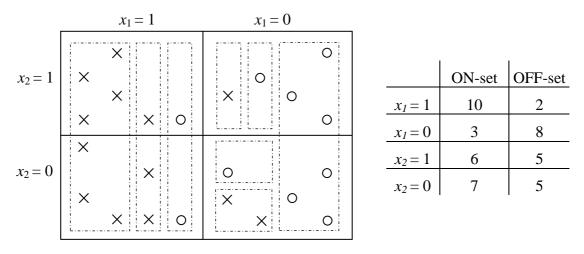

Für solche Funktionen werden effiziente mehrstufige Logikimplementierungen erzeugt. Diese Logikimplementierungen können sehr gut mit Hilfe ungeordneter BDDs (FBDDs) modelliert werden. Das Problem wird auf die Synthese eines minimalen FBDD reduziert. Dies wird durch den Ansatz zweier verschiedener Methoden erreicht: (a) auf DC-basierte Knotenzahlreduzierung und (b) Verteilung des Definitionsraumes der Zielfunktion in eine reduzierte Zahl von Subräumen, die entweder zu '0' oder zu '1' abgebildet werden können. Heuristiken werden verwendet, um fast optimale Teilungen des Definitionsraums in solchen Subräumen zu finden und folglich die Anzahl der Knoten und Pfade der resultierenden FBDD-artigen Implementierungen zu minimieren. Außerdem ist diese Näherung auch im Stande, unter Anwendung des DC-Raumes, die Gatteranzahl zu reduzieren, die in der Implementierung jeder Knotenfunktion erscheint.

Verglichen mit den im CUDD-Paket [Cudd] enthaltenen Methoden (*restrict*-Operator und Umstellung von BDD Variablen), liefert das FBDD-basierte Verfahren

Χ

Logikimplementierungen, deren Schaltungsbeschreibungen ungefähr 70% weniger Logikoperatoren benötigen. Diese Schaltungsbeschreibungen, erzeugt mit beiden Verfahren, wurden mit dem Synopsys Design Compiler synthetisiert. Infolgedessen konnte man erkennen, dass das FBDD-basierte Verfahren den zusätzlichen Bedarf an Schaltungsfläche um einen Faktor zwischen zwei bis drei verbessert und die Laufzeit bedeutend reduziert wird. Des Weiteren kann beobachtet werden, dass das vorgeschlagene Verfahren besser skaliert und einen größeren Nutzen aus der DC-Menge zieht als das bekannteste mehrstufige Synthesewerkzeug SIS [Sen92].

Insgesamt zeigen die experimentellen Ergebnisse für große industrielle Schaltungen, dass das *bit-flipping* DLBIST Verfahren für verschiedene Segmente der IC Tests verwendet werden kann, z.B. für die jenigen die sich mit Sicherheitschips (z.B. Smart-Cards) oder mit *Hardcores* befassen.

Am Ende dieser Arbeit werden einige Ideen vorgeschlagen, um die hier präsentierte Forschung fortzusetzen.

## **Table of Contents**

| Introduction                                                                                                                                                                                                                                      | 1        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1.1 Motivation and Goal of the Work                                                                                                                                                                                                               | 1        |

| 1.2 Outline                                                                                                                                                                                                                                       | 4        |

| Basic Fault Models                                                                                                                                                                                                                                | 7        |

| 2.1 Stuck-at Faults                                                                                                                                                                                                                               | 8        |

| 2.2 Resistive Bridging Faults                                                                                                                                                                                                                     | 9        |

| <ul> <li>2.3 Delay Faults</li> <li>2.3.1 Path-Delay Faults</li> <li>2.3.2 Transition Faults</li> </ul>                                                                                                                                            | 12       |

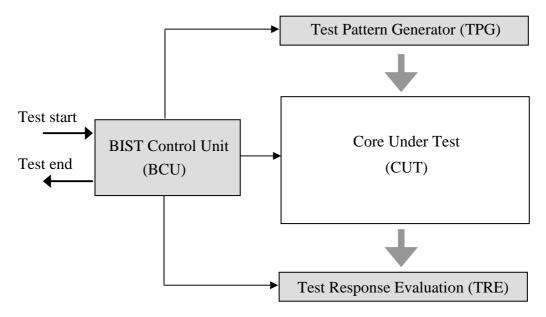

| Basic Concepts of Built-In Self-Test                                                                                                                                                                                                              | 15       |

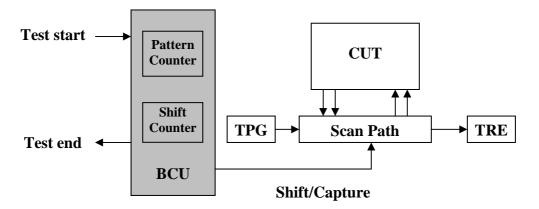

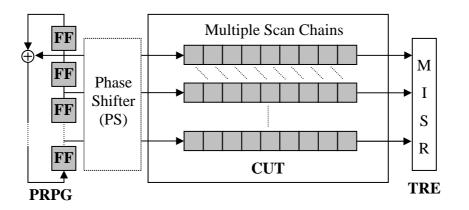

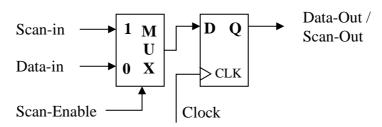

| 3.1 Test-per-scan Schemes                                                                                                                                                                                                                         | 16       |

| 3.2 Test-per-clock Schemes                                                                                                                                                                                                                        | 18       |

| <ul> <li>3.3 Test Pattern Generation</li> <li>3.3.1 Pseudo-Random Pattern Generation</li> <li>3.3.2 Weighted-Random Pattern Testing</li> </ul>                                                                                                    | 19       |

| <ul><li>3.3.3 Exhaustive and Pseudo-Exhaustive Testing</li><li>3.3.4 Deterministic Testing</li><li>3.3.5 Mixed-Mode Testing</li></ul>                                                                                                             | 24       |

| 3.4 Test Response Evaluation                                                                                                                                                                                                                      | 25       |

| Representation, Manipulation and Implementation of Boolean<br>Functions                                                                                                                                                                           |          |

| 4.1 Two-level (Cube-based) Representations of Boolean Functions                                                                                                                                                                                   |          |

| 4.2 Multi-level Implementations of Boolean Functions                                                                                                                                                                                              |          |

| <ul> <li>4.3 BDD-based Representations of Boolean Functions</li> <li>4.3.1 Types of Binary Decision Diagrams</li> <li>4.3.2 ROBDD-based Manipulation of Boolean Functions</li> <li>4.3.3 BDD-based Implementation of Boolean Functions</li> </ul> | 34<br>35 |

| Scalable Pattern Mapping for Deterministic Logic BIST                                                                                                                                                                                             |          |

| 5.1 Bit-Flipping DLBIST Architecture                                                                                                                                                                                                              | 41       |

| 5.2 The Pattern Mapping Problem                                                                                                                                                                                                                   |          |

| 5.3 Cube-based Pattern Mapping                                         |       |

|------------------------------------------------------------------------|-------|

| 5.3.1 Mapping Cost-Function                                            |       |

| 5.3.2 The Algorithm<br>5.3.3 An Example                                |       |

| 5.4 BDD-based Pattern Mapping                                          |       |

| 5.5 Experimental Evaluation of the BDD-based Approach vs. the Cube-ba  |       |

| Approach                                                               |       |

| 5.6 Non-Target Defect Coverage and Overhead Dependence on Sequence     |       |

| 5.7 Conclusion                                                         |       |

| Deterministic Logic BIST for Transition Fault Testing                  | 59    |

| 6.1 Random Testability of Transition and Stuck-at Faults               | 60    |

| 6.2 Bit-flipping Deterministic Logic BIST for Transition Fault Testing | 62    |

| 6.3 Experimental Results                                               | 66    |

| 6.4 Conclusion                                                         | 67    |

| Scalable Synthesis of Irregular Combinational Functions with           | Large |

| Don't Care Sets                                                        | -     |

| 7.1 Examples of Irregular Incompletely Specified Boolean Functions     | 70    |

| 7.2 Proposed FBDD-based Logic Synthesis                                | 71    |

| 7.3 Experimental Results                                               | 76    |

| 7.4 Conclusion                                                         | 78    |

| Conclusions                                                            | 79    |

| 8.1 Summary                                                            | 79    |

| 8.2 Contributions Overview                                             | 81    |

| 8.3 Future Work                                                        |       |

| References                                                             | 85    |

| Index                                                                  | 93    |

| Appendix 1 – Tables with Experimental Results                          | 95    |

| Appendix 2 – Implementation of the Proposed Methods                    | 111   |

| Appendix 3 – Related Papers                                            | 115   |

| Appendix 4 – Short Presentation of the Author                          | 117   |

# **List of Figures**

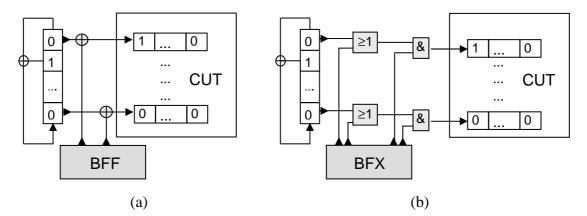

| Figure | 1.1:          | (a) Bit-flipping and (b) bit-fixing BIST schemes                                                                                                                              | 3  |

|--------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

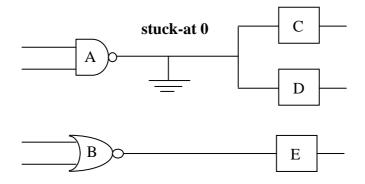

| Figure | 2.1:          | Example of a stuck-at fault                                                                                                                                                   | 8  |

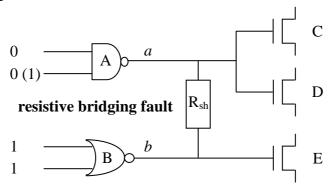

| Figure | 2.2: ]        | Example of a resistive bridging fault [Eng03]                                                                                                                                 | .9 |

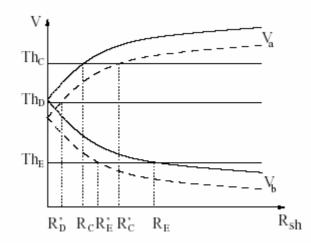

| Figure | 2.3:          | R <sub>sh</sub> -V – diagram [Eng03]                                                                                                                                          | 10 |

| Figure | <b>3.1:</b> ] | Built-in self-test (BIST) (adapted from [Hua03]).                                                                                                                             | 15 |

| Figure | 3.2: '        | Test-per-scan scheme (adapted from [Wun98])                                                                                                                                   | 16 |

| Figure | 3.3:          | STUMPS architecture for parallel-serial mixed scheme (adapted from [Wun02]).                                                                                                  | 16 |

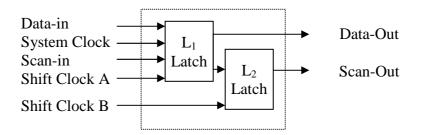

| Figure | 3.4:          | Storage cells for scan design (adapted from [Wun02])                                                                                                                          | 17 |

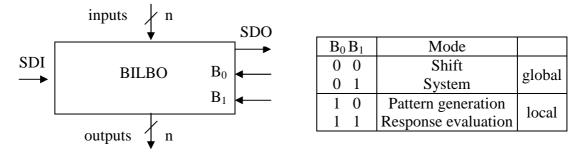

| Figure | 3.5:          | Control signals of a BILBO (adapted from [Wun98])                                                                                                                             | 18 |

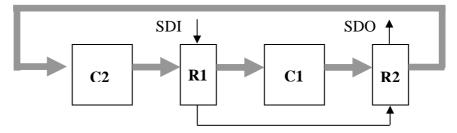

| Figure | 3.6:          | Test-per-clock scheme (adapted from [Wun02]).                                                                                                                                 | 18 |

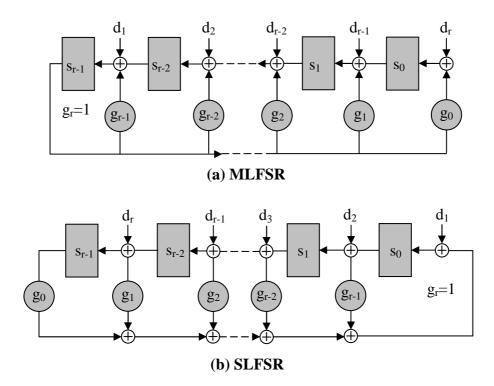

| Figure | 3.7:          | Standard linear feedback shift register (adapted from [Wun98])                                                                                                                | 20 |

| Figure | 3.8:          | State transition matrix of an SLFSR (adapted from [Wun98])                                                                                                                    | 20 |

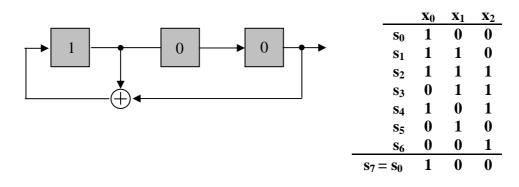

| Figure | 3.9:          | Example of maximum length SLFSR (adapted from [Wun02])                                                                                                                        | 21 |

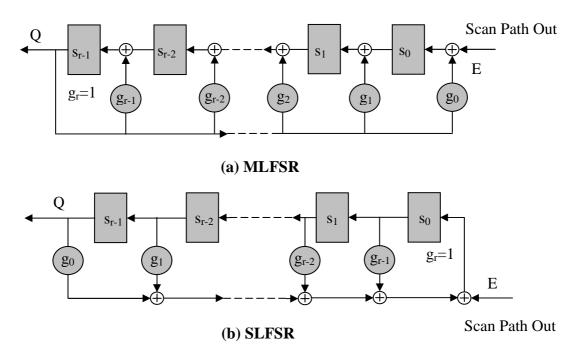

| Figure | 3.10:         | LFSR-based testing (adapted from [Wun98])                                                                                                                                     | 22 |

| Figure | 3.11:         | Modular linear feedback shift register (adapted from [Wun98])                                                                                                                 | 22 |

| Figure | 3.12:         | Equivalence between the transition matrices of MLFSRs and SLFSRs (adapted from [Hua03]).                                                                                      |    |

| Figure | 3.13:         | : LFSR-based time compressors (adapted from [Wun98])                                                                                                                          | 26 |

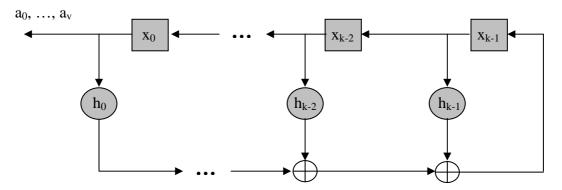

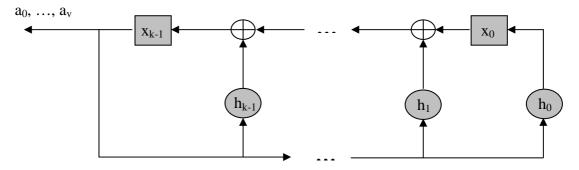

| Figure | 3.14:         | LFSR performing division (adapted from [Hua03]).                                                                                                                              | 27 |

| Figure | 3.15:         | Parallel signature analysis (adapted from [Wun02])                                                                                                                            | 27 |

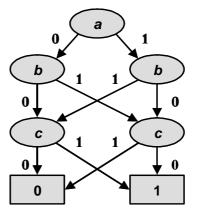

| Figure | 4.1:          | BDD representation of the parity function with three input variables (adapted from [Bry86]).                                                                                  | 33 |

| Figure | 4.2:          | Procedure <i>constrain</i> without hash table (adapted from [Cou90])                                                                                                          | 36 |

| Figure | 4.3:          | Procedure <i>fit</i> without hash table                                                                                                                                       | 37 |

| Figure | 4.4:          | Procedure <i>restrict</i> without hash table (adapted from [Cou90])                                                                                                           | 37 |

| Figure | 4.5:          | (a) BDD for the function $f = \neg a \cdot (\neg b \cdot (\neg c \cdot \neg d) + b \cdot \neg d) + a \cdot (c + \neg d)$ .<br>(b) MUX-based implementation of the function f. | 38 |

| Figure | 4.6:          | Non-redundant implementation of the circuit from Figure 4.5 (b)                                                                                                               | 38 |

| Figure 5.1: | Bit-flipping DLBIST architecture                                                                                                                                                                                                                       |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 5.2: | Cube-based pattern mapping by means of bit-flipping47                                                                                                                                                                                                  |

| Figure 5.3: | LFSR used in the example (adapted from [Wun96])48                                                                                                                                                                                                      |

| Figure 5.4: | New pattern generator including bit-flipping logic (adapted from [Wun96])                                                                                                                                                                              |

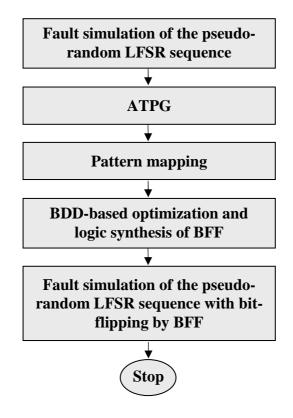

| Figure 5.5: | BDD-based pattern mapping by means of bit-flipping. A description of the program implementing this algorithm is given in Appendix 253                                                                                                                  |

| Figure 5.6: | Evaluation of the effect of embedding deterministic test cubes into a pseudo-random sequence on non-target defect coverage                                                                                                                             |

| Figure 6.1: | Specified bits for testing stuck-at and transition faults61                                                                                                                                                                                            |

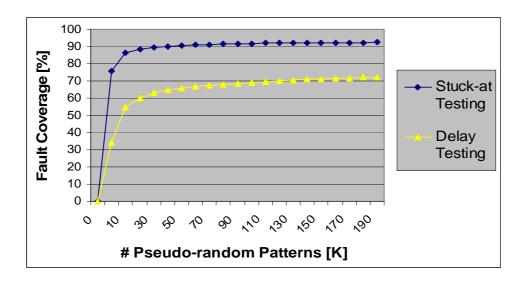

| Figure 6.2: | Cumulative stuck-at and transition fault coverage of a pseudo-random sequence applied to an industrial benchmark design that contains 5116 flip-flops arranged into 11 scan chains. The transition fault testing was based on functional justification |

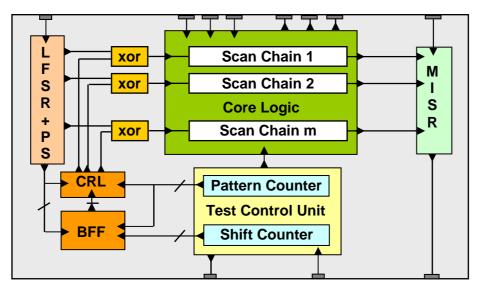

| Figure 6.3: | Architecture of the bit-flipping DLBIST                                                                                                                                                                                                                |

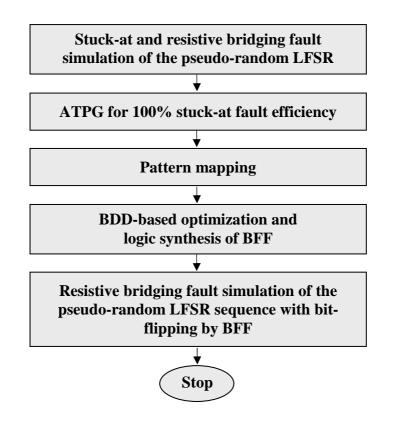

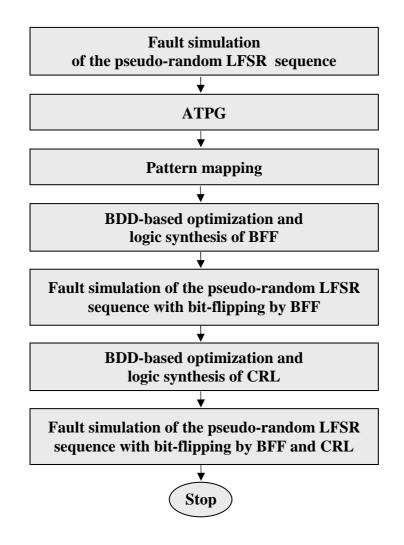

| Figure 6.4: | Implementation flow of the bit-flipping DLBIST for transition fault<br>testing based on functional justification. A description of the program<br>implementing this algorithm is given in Appendix 2                                                   |

| Figure 6.5: | Bit-flipping function (BFF) and correction logic (CRL)65                                                                                                                                                                                               |

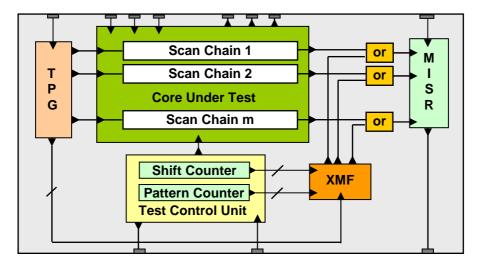

| Figure 7.1: | Embedded test architecture with MISR and X-masking function (XMF).                                                                                                                                                                                     |

| Figure 7.2: | Example of the proposed decomposition of the definition space74                                                                                                                                                                                        |

## List of Tables

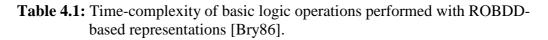

| Table 4.1:        | Time-complexity of basic logic operations performed with ROBDD-based representations [Bry86]35                                                                                                                                                          |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 5.1:        | States of the LFSR (adapted from [Wun96])48                                                                                                                                                                                                             |

| Table 5.2:        | Pseudo-random patterns and corresponding LFSR states (adapted from [Wun96])                                                                                                                                                                             |

| Table 5.3:        | Finding a pattern for mapping $t = 00X00$ (adapted from [Wun96])49                                                                                                                                                                                      |

| Table 5.4:        | Old and new set of patterns (adapted from [Wun96])50                                                                                                                                                                                                    |

| Table 5.5:        | Benchmark designs characteristics with respect to stuck-at fault testing95                                                                                                                                                                              |

| Table 5.6:        | Run-time for different tasks of the cube-based and BDD-based algorithms. For the design $p2074k$ a machine equipped with 2 GB of memory and an Intel Pentium 4 CPU running at 2.4 GHz has been used96                                                   |

| Table 5.7:        | Run-time and memory consumption of the cube-based and BDD-based algorithms. For the design $p2074k$ a machine equipped with 2 GB of memory and an Intel Pentium 4 CPU running at 2.4 GHz has been used. 96                                              |

| Table 5.8:        | Fault efficiency and logic overhead of the cube-based and BDD-based algorithms                                                                                                                                                                          |

| Table 5.9:        | Results obtained with the BDD-based approach targeting the fault efficiency allowed by the ATPG tool. For the designs <i>p278k</i> and <i>p2074k</i> a machine equipped with 2 GB of memory and an Intel Pentium 4 CPU running at 2.4 GHz has been used |

| Table 5.10        | Characteristics of the ISCAS (85 and 89) benchmark designs                                                                                                                                                                                              |

| Table 5.11        | Comparison of the two approaches on some ISCAS (85 and 89) designs.                                                                                                                                                                                     |

| Table 5.12        | : Stuck-at coverage of pseudo-random sequences before deterministic cube embedding                                                                                                                                                                      |

| Table 5.13        | Resistive bridging fault coverage (FC <sub>G</sub> ) of the pseudo-random and embedded test sequences and DLBIST overhead (LSIZE)                                                                                                                       |

| Table 6.1:        | CRL impact on the overhead of the bit-flipping DLBIST architecture101                                                                                                                                                                                   |

| <b>Table 6.2:</b> | Benchmark characteristics with respect to transition fault testing102                                                                                                                                                                                   |

| Table 6.3:        | DLBIST applied to stuck-at and transition fault testing (10K test patterns).<br>                                                                                                                                                                        |

| Table 6.4:        | Test sequence length impact on DLBIST used for transition fault testing                                                                                                                                                                                 |

|                   | Possible trade-offs between the fault efficiency and the hardware corresponding to the maximum test length which can fit in one second of test time at the frequency of 100 MHz |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Table 7.1:</b> | Multi-output incompletely specified benchmark functions105                                                                                                                      |

| <b>Table 7.2:</b> | Comparison between the FBDD-based optimization approach and the approach based on the <i>restrict</i> operator                                                                  |

| <b>Table 7.3:</b> | Optimization potential of the FBDD-based and the OBDD-based ( <i>restrict</i> + variable reordering) approaches                                                                 |

| <b>Table 7.4:</b> | Synthesis results obtained using the FBDD-based and the OBDD-based ( <i>restrict</i> + variable reordering) approaches                                                          |

| Table 7.5:        | Comparison between SIS and the FBDD-based approach combined with SIS110                                                                                                         |

| <b>Table 8.1:</b> | Contributions of the work mapped to the structure of the manuscript82                                                                                                           |

| Table 9.1:        | The functions that implement the flow presented in Figure 6.4                                                                                                                   |

| <b>Table 9.2:</b> | The most important methods of the class CbflBdd112                                                                                                                              |

| <b>Table 9.3:</b> | Thresholds and flags used to configure the DFT flow in Figure 6.4 113                                                                                                           |

# List of Symbols and Abbreviations

| œ                                | Infinite                                                                                                                                        |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Ø                                | Empty set                                                                                                                                       |

| Ω                                | Ohm – measurement unit of the electrical resistance                                                                                             |

| -                                | Logic negation operator                                                                                                                         |

| •                                | Logic conjunction operator or, depending on the context, multiplica-<br>tion operator                                                           |

| +                                | Logic disjunction operator or, depending on the context, addition operator                                                                      |

| $\oplus$                         | EXOR operator                                                                                                                                   |

| U                                | Set union operator                                                                                                                              |

| $\cap$                           | Set intersection operator                                                                                                                       |

| _                                | Concatenation operator                                                                                                                          |

| $\downarrow$                     | Constrain operator                                                                                                                              |

| ₩                                | Restrict operator                                                                                                                               |

| $\exists_x$                      | Existential quantification with respect to the variable $x$                                                                                     |

| $\mathbf{f} _{\mathbf{l}}$       | Cofactor of the Boolean function $f$ with respect to the literal $l$                                                                            |

| <b>h</b>                         | Absolute value of an algebraic expression h                                                                                                     |

| <b>G</b>                         | Size (number of nodes) of the graph G                                                                                                           |

| <b>f</b>                         | Number of input assignments mapped by the Boolean function $f$ to 1                                                                             |

| $F(f_{on}, f_{off})$             | Representation of an incompletely specified function F defined by its ON-set, represented by $f_{on}$ , and OFF-set, represented by $f_{off}$ . |

| ADI                              | Analogue detectability interval                                                                                                                 |

| AND                              | Boolean conjunction operator                                                                                                                    |

| ATE                              | Automated test equipment                                                                                                                        |

| ATPG                             | Automatic test pattern generator                                                                                                                |

| BCU                              | BIST control unit                                                                                                                               |

| BDD                              | Binary Decision Diagram                                                                                                                         |

| BFF                              | Bit-flipping function                                                                                                                           |

| BFX                              | Bit-fixing function                                                                                                                             |

| ATE<br>ATPG<br>BCU<br>BDD<br>BFF | Automated test equipment<br>Automatic test pattern generator<br>BIST control unit<br>Binary Decision Diagram<br>Bit-flipping function           |

| BILBO                   | Built-in logic block observer                                                           |

|-------------------------|-----------------------------------------------------------------------------------------|

| BIST                    | Built-in self-test                                                                      |

| CAD                     | Computer-Aided Design                                                                   |

| <b>ADI</b> <sub>C</sub> | Covered ADI                                                                             |

| <b>ADI</b> <sub>G</sub> | Global ADI                                                                              |

| Cov(F)                  | Cover of the incompletely specified function F                                          |

| CRL                     | Correction logic                                                                        |

| CUDD                    | CU (Colorado University) decision diagram package                                       |

| CUT                     | Core (or circuit) under test                                                            |

| DC                      | Don't care                                                                              |

| DC-set                  | Set of input assignments of a Boolean function that can be mapped either to 1 or to $0$ |

| DC-space                | Similar to DC-set                                                                       |

| DLBIST                  | Deterministic LBIST                                                                     |

| ESPRESSO                | Heuristic approach used for optimizing two-level representations of Boolean functions   |

| EXOR                    | Boolean exclusive-OR operator                                                           |

| EXPAND                  | Operator used by ESPRESSO (transforms a cover into a prime and irredundant cover)       |

| FBDD                    | Free (also called unordered) BDD                                                        |

| FC                      | Fault coverage                                                                          |

| FDD                     | Functional Decision Diagram                                                             |

| FE                      | Fault efficiency                                                                        |

| FF                      | Flip-flop                                                                               |

| FIX-set                 | $On-set \cup Off-set$                                                                   |

| IC                      | Integrated circuit                                                                      |

| ID                      | Identity matrix                                                                         |

| IDDQ                    | Power supply current (IDD) in a CMOS circuit when all nodes are quiescent (static)      |

| ISCAS                   | International Symposium on Circuits and Systems                                         |

| LBIST                   | Logic BIST                                                                              |

| LFSR                    | Linear feedback shift register                                                          |

| LHCA                    | Linear hybrid cellular automata                                                         |

| MISR                    | Multiple input shift register                                                           |

| MLFSR                   | Modular LFSR                                                                            |

| MUX                     | Multiplexer                                                                             |

| NAND    | Boolean negation and conjunction operator                                                                               |

|---------|-------------------------------------------------------------------------------------------------------------------------|

| NOR     | Boolean negation and disjunction operator                                                                               |

| OBDD    | Ordered BDD                                                                                                             |

| OFF-set | Set of input assignments mapped to 0 by a Boolean function                                                              |

| OFF-BDD | ROBDD-based representation of the OFF-set                                                                               |

| ON-set  | Set of input assignments mapped to1 by a Boolean function                                                               |

| ON-BDD  | ROBDD-based representation of the ON-set                                                                                |

| OR      | Boolean disjunction operator                                                                                            |

| PC      | Pattern counter                                                                                                         |

| PLA     | Programmable logic array                                                                                                |

| PRPG    | Pseudo-random pattern generator                                                                                         |

| PS      | Phase shifter                                                                                                           |

| REDUCE  | Operator used by ESPRESSO (transforms a prime and irredundant cover into a new irredundant but usually not prime cover) |

| ROBDD   | Reduced OBDD                                                                                                            |

| ROM     | Read only memory                                                                                                        |

| RPR     | Random pattern resistant                                                                                                |

| RTL     | Register transfer level                                                                                                 |

| SC      | Shift (also called bit) counter                                                                                         |

| SE      | Scan enable signal                                                                                                      |

| SG      | Already synthesized sub-graph                                                                                           |

| SLFSR   | Standard LFSR                                                                                                           |

| SOC     | System on a chip                                                                                                        |

| STUMPS  | Self-test using MISR and parallel shift register sequence generator                                                     |

| Th      | Threshold voltage of a gate input                                                                                       |

| TPG     | Test pattern generator                                                                                                  |

| TRE     | Test response evaluator                                                                                                 |

| TRP     | Test resource partitioning                                                                                              |

| V       | Volt – measurement unit of the voltage                                                                                  |

| VHDL    | VHSIC (very high speed integrated circuit) hardware description lan-<br>guage                                           |

| VDD     | Positive supply voltage for field effect transistors (FET)                                                              |

| X       | Unspecified or unknown bit value                                                                                        |

| XMF     | X-masking function                                                                                                      |

| ZBDD    | Zero-suppressed BDD                                                                                                     |

### **Chapter 1**

### Introduction

#### 1.1 Motivation and Goal of the Work

The sustained improvement of deep-submicron technologies has led to an explosion in the number of transistors that may be integrated on a chip and further to the possibility of putting a whole *system on a chip* (SOC). Core-based design is one paradigm of the new trends used to reduce complexity and costs of chip development. Nevertheless, test-related costs are problems still far away from having a unitary and satisfactory solution.

The external testing of integrated circuits (ICs) is a traditional approach in which *automated test equipment* (ATE) provides all the necessary test data. This may set high requirements on the storage capacity and speed of the ATE. Furthermore, the ever increasing transistor count per I/O pin and the low accessibility of internal blocks are affecting the tradeoff between the final fault coverage and the test application time. All of these, combined with the necessity of specially tuned testers for different types of cores and the growing need for periodic in-field maintenance and on-line testing capabilities make the external testing difficult, costly and insufficient.

All the above mentioned problems demand *built-in self-test* (BIST) solutions. In this context, BIST for random logic (LBIST) is becoming an attractive alternative in IC testing.

The standard BIST architecture [Bar82][Eic83] uses an LFSR that feeds pseudo-random patterns into the scan paths. It is easy to implement and minimizes both hardware overhead and impact on the system performance. However, due to random-patternresistant (RPR) faults, pseudo-random patterns cannot always achieve sufficient fault coverage within an acceptable test time.

The fault coverage can be increased by biasing the pseudo-random test sequence towards the RPR faults [Brg89][Wun88]. Conflicting input values required by different RPR faults may need different weighting sets. Unfortunately, the control logic and the storage requirements for the weighting sets can increase unacceptably.

Pseudo-exhaustive testing [Mcc81] achieves the benefits of exhausting testing while usually requiring less test patterns. This reduction is obtained by splitting the circuit into various segments that are tested exhaustively. The efficiency of the method is limited by the size of the largest segment that has to be tested.

An alternative approach for increasing the fault coverage is the insertion of test points, which has been proposed for both LBIST and external testing [Geu00][Hay74] [Sei91][Vra02]. While the area increase due to test point insertion may be tolerable, they can introduce additional signal delays, which could require a complete resynthesis and a new timing verification [Vra04].

Deterministic LBIST (DLBIST) guarantees higher or complete fault coverage by embedding deterministic test *cubes* (test patterns with unspecified bits) into the pseudo-random sequence. There is a wide range of deterministic logic BIST methods that apply deterministic test patterns and hence improve the low fault coverage often obtained by pseudo-random patterns. In an initial deterministic BIST scheme, additional external patterns were applied on top of the pseudo-random test [Het99]. Unfortunately, the very last percentages of fault coverage require the largest amount of deterministic patterns. For instance, it has been reported in [Bas89] that detecting the last 10% of undetected faults typically requires 70% or more of the test patterns in an automatic test pattern generated set. Consequently, the benefits of deterministic BIST are severely reduced by this approach.

Compression and decompression methods in which a small amount of external test data is continuously fed into the circuit [Koe91][Koe01][Raj02] are more efficient. However, this approach is no longer a BIST method; it may still require a relatively expensive ATE and lose some benefits of BIST like in-field testing.

In contrast to the above mentioned BIST methods, pure DLBIST schemes try to avoid both the modification of the *core under test* (CUT) and the application of additional external test data. These methods can be classified into *store and generate* schemes and *test set embedding* schemes.

*Store and generate* schemes consist of hardware structures which store the test patterns on-chip in a compressed form and implement a decompression algorithm. Widely known representatives of this method are LFSR-reseeding [Koe91], multipolynomial reseeding [Hel92][Hel95] and folding counter based-LBIST [Lia02].

*Test set embedding* schemes rely on a pseudo-random test pattern generator plus some additional circuitry that modifies the pseudo-random sequence in such a way that a set of deterministic cubes is embedded. Widely known test set embedding techniques are *bit-flipping* [Kie00][Wun96][Kie97][Kie98] and *bit-fixing* [Tou96].

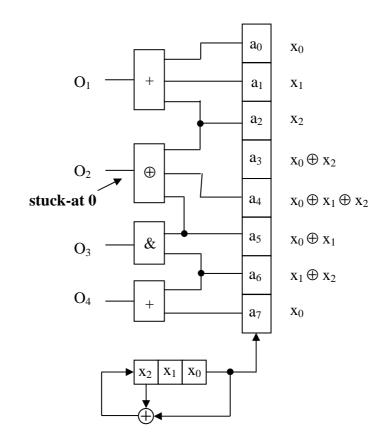

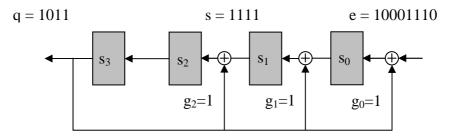

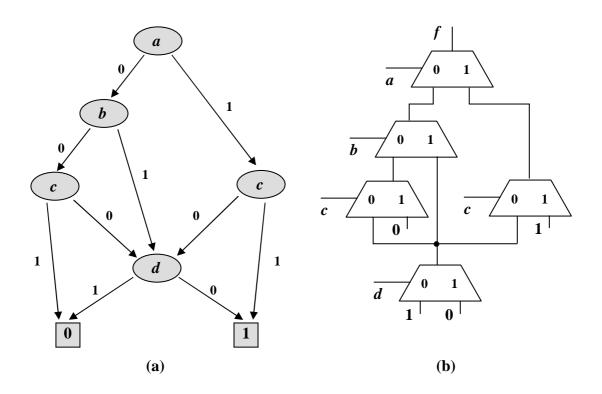

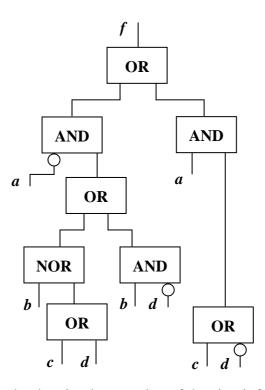

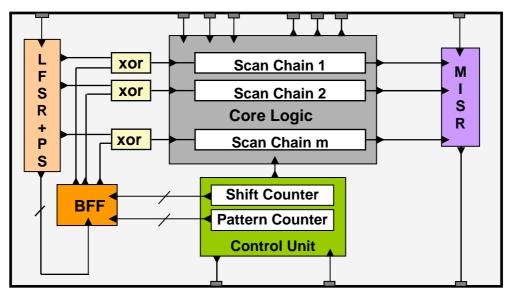

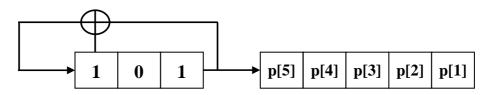

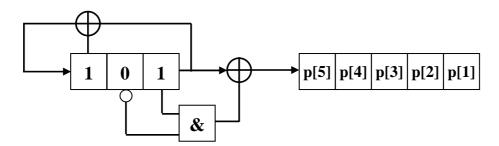

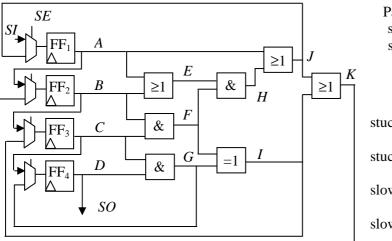

In the bit-flipping approach, the output sequence of an LFSR is inverted at a few bit positions in order to increase the fault coverage (Figure 1.1.a), while in the bit-fixing approach constant values are applied (Figure 1.1.b). The test generation process is controlled by a *bit-flipping function* (BFF) or a *bit-fixing function* (BFX), respectively.

The term *pattern mapping* will be used for referring to the assignment of a pseudorandom pattern to a given deterministic cube. The synthesis procedure of a DLBIST scheme consists of pattern mapping and generation of the hardware structure used to implement the mapping, e.g. by means of a BFF or BFX. The synthesis procedure for generating the BFX as published in [Tou96] is based on rectangle covering, while the synthesis procedure for generating the BFF as published in [Wun96][Kie97][Kie98] is based on manipulating sets of test cubes. In both cases, the procedures use heuristics that generally require at least cubical, but often exponential, effort in terms of memory consumption and computation time.

Figure 1.1: (a) Bit-flipping and (b) bit-fixing BIST schemes.

In this work, a novel *pattern mapping* approach is proposed that has nearly linear complexity in terms of both computation time and memory consumption. The used algorithms are based on Binary Decision Diagrams (BDDs). The efficiency of the new algorithms is demonstrated by experimental results obtained with ISCAS benchmarks and industrial designs containing up to 2M gates.

The embedded test sequences obtained by mapping deterministic cubes to pseudorandom sequences are also evaluated with respect to their coverage of non-target defects. Moreover, possible tradeoffs between the test length, hardware overhead, fault coverage and non-target defect coverage are analyzed.

All the methods discussed so far mainly refer to the test of stuck-at faults. Unfortunately, the steady increase of the clock rate and the integration density in today's IC designs enhance the significance of the timing accuracy defects [Cha96], which are difficult to be covered by the classical stuck-at fault model. Consequently, delay fault models and, implicitly, delay fault testing become more and more important.

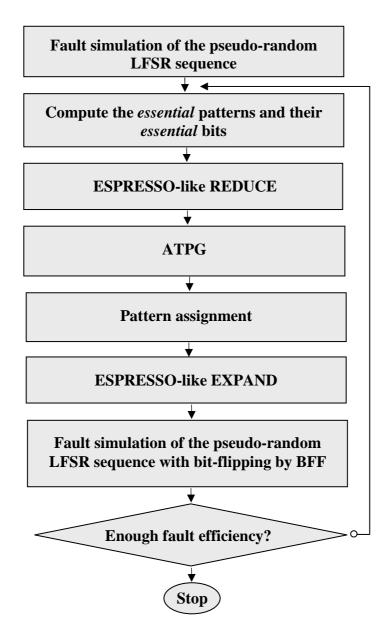

Here, an extension of the bit-flipping DLBIST approach to the test of transition faults is also presented. The scheme is based on functional justification and on an efficient pattern embedding. A special module, the *correction logic* (CRL), is introduced to further improve the pattern embedding. Due to the rather low random-pattern testability of transition faults, the saturation of their random fault coverage requires significantly longer test sequences, which in turn is beneficial for both limiting the hardware overhead and improving the coverage of modeled and non-modeled defects [Tan04].

A major concern of the test set embedding schemes is their hardware overhead. Reducing the hardware overhead of the DLBIST scheme considered here is equivalent to optimizing the logic synthesis of the BFF. Two properties of this function are relevant for its logic implementation: the *irregularity*, defined by the random distribution over the definition space of the input assignments mapped to '1' and the *incomplete specification*, defined by the existence of input assignments for which it does not matter whether they are mapped to '0' or '1'. Other examples of such functions are the BFX [Tou96], the function implemented by the CRL and the so-called *X-masking function* (XMF) [Tan04].

This work proposes an efficient and innovative way to implement irregular Boolean functions with large *don't care* sets. Reduced ordered BDDs (ROBDD) are used for representing and manipulating the involved functions. Multi-level representations are

obtained based on free BDDs (FBDD). The problem is reduced to the construction of an efficient BDD-based representation by using the *don't care* space to perform node reduction and to partition the definition space of the considered function into a minimum number of sub-spaces which may be mapped either '0' or '1'. Heuristics are used to find near-optimal partitions of the definition space into such sub-spaces and, consequently, to minimize the path and node count of the resulting FBDD. Furthermore, this approach is also able to use the *don't care* set to reduce the average gate count per node. Experimental results show that for all the considered functions, implementations are found with a significant reduction of the gate count compared to the well known multi-level synthesis tool, SIS [Sen92], or to methods offered by a state-of-the-art BDD package. This performance is due to a reduction of the node count in the corresponding FBDDs and a decrease in the average number of gates needed to implement the FBDD nodes.

#### **1.2 Outline**

Chapter 2 briefly describes the three logical fault models which will be used in this work. Section 2.1 introduces the stuck-at fault model. In Section 2.2, the resistive bridging fault model is described. Section 2.3 presents two delay fault models: the transition and the path delay fault models. Only the transition fault model will be used later in the work. The path delay fault model is briefly mentioned in order to better understand specific aspects of the delay fault testing.

Basic BIST concepts are reviewed in Chapter 3. *Test-per-scan* and *test-per-clock* BIST schemes are described in Section 3.1 and Section 3.2, respectively. State-of-theart methods for test pattern generation and test response evaluation are analyzed in Section 3.3 and Section 3.4, respectively.

Chapter 4 compares two of the basic approaches that are used for the representation and the manipulation of Boolean functions. Section 4.1 introduces the cube-based, also called disjunctive two-level representation. The generalization of this representation to the multi-level representation and implementation is described in Section 4.2. Section 4.3 presents the representation, manipulation and logic synthesis of Boolean functions based on Binary Decision Diagrams (BDDs).

Chapter 5 presents a new algorithm for mapping deterministic test cubes to a pseudorandom test sequence. The algorithm is based on BDDs and outperforms the previously published cube-based approach [Wun96] by several orders of magnitude. It has been applied to the bit-flipping Deterministic Logic LBIST (DLBIST) architecture which is presented in Section 5.1. The pattern mapping problem is formally defined in Section 5.2. Sections 5.2 and 5.3 provide a detailed description of a prior cube-based and of the new BDD-based mapping algorithms, respectively. Section 5.5 reports the experimental results obtained with a set of industrial designs containing up to 2M gates, ISCAS-85 and combinational parts of ISCAS-89 benchmark designs. These results prove that significant improvements can be achieved with the help of the BDD-based mapping approach. In Section 5.6, the embedded test sequences generated for single stuck-at faults are evaluated with respect to the coverage of non-target defects. Resistive bridging faults are used as a surrogate of non-target defects [Eng05]. This is the first time when the results of such a study are presented. This investigation especially adresses the impact of the test sequence length on the nontarget defect coverage and on the hardware overhead. The chapter is concluded in Section 5.7.

Chapter 6 extends the approach introduced in Chapter 5 to make it also available for the test of transition faults. Due to the fact that pairs of test patterns are required, transition faults are more difficult to test than stuck-at faults. In Section 6.1, a qualitative comparison of stuck-at and transition faults is made with respect to their pseudorandom testability. The extension of the bit-flipping DLBIST scheme for transition fault testing is described in Section 6.2. Relevant experimental results for large industrial benchmark designs are reported in Section 6.3. The chapter is summarized in Section 6.4.

In Chapter 7, an innovative BDD-based logic synthesis method is described that improves the implementation of the BFF. This approach is especially suited for the logic implementations of *irregular* functions that have large *don't care* sets. Some examples of such functions are: the BFF, the BFX [Tou96] and the function XMF introduced in [Tan04], etc. Two of these examples are analyzed in Section 7.1. Section 7.2 presents a new heuristic method to find efficient logic implementations for such functions. In Section 7.3, experimental results are used to compare the new approach with SIS [Sen92] and methods available in the CUDD-package (like *restrict* [Cou90]). Furthermore, the outcome of the proposed method is evaluated as input to Synopsys Design Compiler. The chapter is concluded in Section 7.4.

Chapter 8 summarizes the work and suggests some related research directions that look promising and may be investigated in a future work.

## **Chapter 2**

### **Basic Fault Models**

This chapter describes the three logical fault models used in this work. Logical faults represent the effect of physical defects on the logic behavior of the modeled system. Restricting the analysis of physical defects to the level of the logic behavior has several advantages. The complexity is reduced by transforming a physical problem into a logical problem. The space of physical defects is larger than the space of logical faults, such that a fault model can cover several physical defect types. Moreover, tests derived for certain logical faults may cover physical defects for which no accurate fault model is known. Most of the logical fault models are technology-independent and hence testing and diagnosis methods developed for such fault models are applicable to many technologies [Abr90].

A distinction is made between faults that affect the logic correctness of a circuit and delay faults that affect the operating speed of the system. Depending upon the type of modeling used for the system, the former faults may be divided in structural and functional faults. Structural fault models are usually defined at the gate level net-list and assume that components are fault-free and only their interconnections are affected. Functional faults are usually defined at RTL or higher levels (like behavioral or system level) and they affect the proper execution of the operations used at these levels.

*Shorts* and *opens* are two examples of structural faults. A *short* is formed by connecting points not intended to be connected while an *open* results by breaking a connection.

In this work only structural, permanent and single faults of combinational logic are considered. Intermittent, transient, or multiple-faults are not taken into account. The analog and the memory elements that may be present in the circuit under test are not considered.

Under the single-fault assumption one assumes that in a system at most one logical fault is present. This assumption is justified by the fact that in most of the cases a multiple fault can be detected by the tests designed for the individual single faults that compose the multiple-fault [Abr90].

Section 2.1 introduces the stuck-at fault model. In Section 2.2, the resistive bridging fault model is briefly described. Section 2.3 introduces two representative delay fault models: the transition and the path delay fault model. Only the transition fault model will be used later in this work. The path delay fault model is mentioned in order to better understand specific aspects of the delay fault testing.

#### **2.1 Stuck-at Faults**

The logical fault corresponding to a signal line being *stuck at* a fixed logic value (0/1) is referred to as a single stuck-at 0/1 fault (Figure 2.1). Physical defects which can be modeled with the help of a stuck-at 0/1 fault on the signal line *i* include an open on the fan-out lines driven by the line *i*, a short to power/ground or an internal error in the component driving the line *i*.

Figure 2.1: Example of a stuck-at fault.

Despite the fact that the single stuck-at fault model does not cover all the physical defects that can appear in a digital circuit, it is very useful due to the following properties:

- It is very simple. As compared to other fault models, the number of single stuckat faults in a circuit grows linearly with its size. Moreover, the number of these faults that have to be explicitly considered can be reduced by fault collapsing. Techniques like structural-based and dominance-based fault collapsing can reduce the number of faults to be explicitly analyzed by 50% and 40%, respectively [Abr90].

- It models many different physical defects [Tim83]. Test sets generated for single stuck-at faults may detect many faults belonging to other fault models.

- It is technology independent.

- The single stuck-at fault model and its analysis can be used to construct and analyze other types of fault models, like the transition fault model (Section 2.3.3).

A combinational circuit that contains an undetectable stuck-at fault is said to be *redundant*, since such a circuit can always be simplified by removing at least one gate or input. The test generation problem for stuck-at faults belongs to the class of NP-complete problems (worst-case behavior) [Iba75]. Undetectable (redundant) faults are usually the ones that cause test generation algorithms to exhibit their worst-case behavior [Abr90].

A straightforward extension of the single stuck-at fault model is the multiple stuck-at fault model. This fault model is more difficult to handle. The list of faults for a circuit having *N* possible sites for single stuck-at faults can contain up to 2*N* single and  $3^{N}$ -1 multiple stuck-at faults [Abr90]. Fortunately, the importance of the multiple stuck-at fault model is reduced due to the fact that tests with complete detection of the single stuck-at faults would usually also detect most of the multiple stuck-at faults [Hug84].

For all fault models introduced in this chapter, whose description does not depend on a continuous parameter, the following metrics are used to characterize the quality of a test set.

- **Definition 2.1:** The *fault coverage* (FC) is the percentage of detected faults with respect to the total number of faults.

- **Definition 2.2:** The *fault efficiency* (FE) is the percentage of detected faults with respect to the total number of testable faults.

#### 2.2 Resistive Bridging Faults

A logical fault representing an electrical connection between a pair of signal lines (nets) is referred to as a *bridging fault*. The non-resistive bridging fault model considers a short between the two nets. The logic value of the shorted nets may be modeled as 1-dominated (OR bridge), 0-dominated (AND bridge) or intermediate, depending upon the implementation technology [Bus00][Mal92].