## Institute of Computer Architecture and Computer Engineering Prof. Dr. rer. nat. habil. Hans-Joachim Wunderlich Pfaffenwaldring 47, 70569 Stuttgart

Master Thesis Nr. 3447

# **Embedding Deterministic Patterns in Partial Pseudo-Exhaustive Test**

Anastasia Sannikova

#### **MSc Thesis**

in partial fulfillment of the requirements for the degree of **Master of Science**

Supervisors: M. Sc. Abdullah Mumtaz

Dipl.-Inf. Michael Imhof

Examiner: Prof. Dr. rer. nat. habil. Hans-Joachim Wunderlich

Start Date: 15.11.2012

Submission Date: 17.05.2013

CR Classification: B.7.3, B.8.1

Study Program: M. Sc. Information Technology (INFOTECH)

#### **ABSTRACT**

The topic of this thesis is related to testing of very large scale integration circuits. The thesis presents the idea of optimizing mixed-mode built-in self-test (BIST) scheme. Mixed-mode BIST consists of two phases. The first phase is pseudo-random testing or partial pseudo-exhaustive testing (P-PET). For the faults not detected by the first phase, deterministic test patterns are generated and applied in the second phase. Hence, the defect coverage of the first phase influences the number of patterns to be generated and stored. The advantages of P-PET in comparison with usual pseudo-random test are in obtaining higher fault coverage and reducing the number of deterministic patterns in the second phase of mixed-mode BIST. Test pattern generation for P-PET is achieved by selecting characteristic polynomials of multiple-polynomial linear feedback shift register (MP-LFSR).

In this thesis, the mixed-mode BIST scheme with P-PET in the first phase is further improved in terms of the fault coverage of the first phase. This is achieved by optimization of polynomial selection of P-PET.

In usual mixed-mode BIST, the set of undetected by the first phase faults is handled in the second phase by generating deterministic test patterns for them. The method in the thesis is based on consideration of these patterns during polynomial selection. In other words, we are embedding deterministic test patterns in P-PET. In order to solve the problem, the algorithm for the selection of characteristic polynomials covering the pre-generated patterns is developed.

The advantages of the proposed approach in terms of the defect coverage and the number of faults left after the first phase are presented using contemporary industrial circuits. A comparison with usual pseudo-random testing is also performed. The results prove the benefits of P-PET with embedded test patterns in terms of the fault coverage, while maintaining comparable test length and time.

# **Table of Contents**

| ABSTRACT                                                                | 1  |

|-------------------------------------------------------------------------|----|

| LIST OF FIGURES                                                         | 4  |

| LIST OF TABLES                                                          | 5  |

| LIST OF ABBREVIATIONS                                                   | 6  |

| 1. INTRODUCTION                                                         | 7  |

| 1.1 Motivation and goals of the work                                    | 7  |

| 1.2 Thesis outline                                                      | 9  |

| 2. PRELIMINARIES AND STATE OF THE ART                                   | 10 |

| 2.1 Basic Definitions                                                   | 10 |

| 2.2 Fault model dependent testing                                       | 14 |

| 2.2.1 Mixed-mode BIST                                                   | 17 |

| 2.3 Fault model independent testing                                     | 20 |

| 2.4 Partial Pseudo-Exhaustive Testing                                   | 23 |

| 3. PROBLEM FORMULATION AND SOLUTION FLOW                                | 27 |

| 3.1 Problem formulation                                                 | 27 |

| 3.2 Solution flow                                                       | 28 |

| 4. FAULTS CLASSIFICATION AND TEST PATTERN GENERATION                    | 30 |

| 4.1 Fault classification on hard-to-detect and easy-to-detect faults    | 30 |

| 4.2 Generation of deterministic test patterns for hard-to-detect faults | 32 |

| 4.2.1 ATPG with minimum number of care bits                             | 32 |

| 4.2.2 Commercial ATPG                                                   | 35 |

| 5. SET COVERING HEURISTICS                                              | 38 |

| 5.1 Shifting of the cones and removing redundant cones                  | 39 |

| 5.2 Iterative polynomial selection                                      | 39 |

| 5.2.1 General algorithm                                                 | 40 |

| 5.2.1.1 Essential cone handling                                         | 42 |

| 5.2.1.2 Realization with minimal number of polynomials                  | 43 |

| 5.2.1.3 Realization with more than minimal number of polynomials        | 43 |

| 5.3 User-defined introduction of extra polynomial                       | 45 |

| 5.4. Summary of the algorithm for polynomial selection                  | 46 |

| 6. | EXPERIMENTAL RESULTS                              | 48 |

|----|---------------------------------------------------|----|

|    | 6.1 Circuit characteristics                       | 48 |

|    | 6.2 Fault simulation results                      | 49 |

|    | 6.3 Results of test pattern generation            | 50 |

|    | 6.4 Set covering heuristics results               | 52 |

|    | 6.5 Comparison of P-PET and pseudo-random testing | 58 |

|    | 6.6 Summary and discussions                       | 59 |

| 7. | CONCLUSIONS                                       | 61 |

| RE | EFERENCES                                         | 63 |

| De | eclaration                                        | 67 |

# LIST OF FIGURES

| Figure 2.1: The concept of testing                              | 10 |

|-----------------------------------------------------------------|----|

| Figure 2.2: Combinational circuit                               | 12 |

| Figure 2.3: General BIST hardware scheme                        | 14 |

| Figure 2.4: External type linear feedback shift register        | 15 |

| Figure 2.5: Internal type linear feedback shift register        | 15 |

| Figure 2.6: Example of external linear feedback shift register  | 16 |

| Figure 2.7: LFSR with scan chain                                | 18 |

| Figure 2.8: Multiple-polynomial LFSR                            | 19 |

| Figure 2.9: LFSR reseeding scheme                               | 19 |

| Figure 2.10: General STUMPS scheme                              | 20 |

| Figure 2.11: Circuit under test                                 | 21 |

| Figure 2.12: Cone segmentation                                  | 21 |

| Figure 2.13: Testing via sensitized path segmentation [13]      | 22 |

| Figure 2.14: Cone segmentation for P-PET                        | 23 |

| Figure 2.15: STUMPS architecture for P-PET testing              | 24 |

| Figure 2.16: LFSR and scan chain                                | 25 |

| Figure 3.1: Cone segmentation in P-PET                          | 27 |

| Figure 4.1: Fault simulation                                    | 31 |

| Figure 4.2: Fault coverage of pseudo-random testing             | 31 |

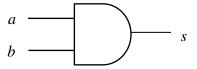

| Figure 4.3: AND-gate for 2-valued logic                         | 33 |

| Figure 4.4: AND-gate for 3-value logic                          | 34 |

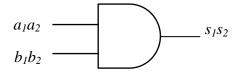

| Figure 4.5: Process of generating patterns with commercial ATPG | 36 |

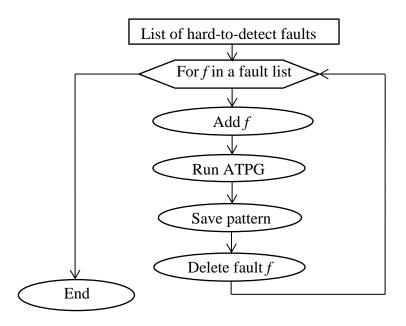

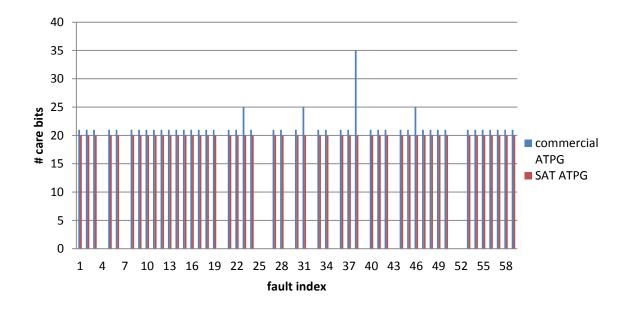

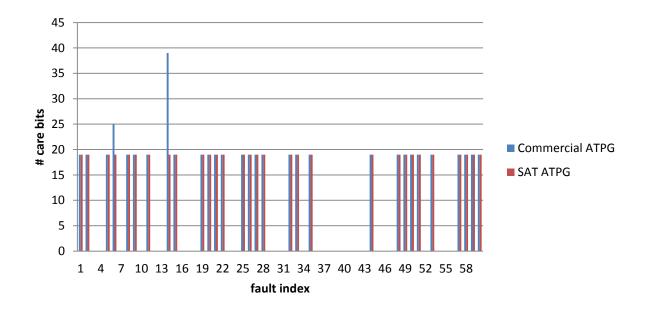

| Figure 4.6: Commercial vs. SAT-based ATPG for p45k              | 36 |

| Figure 4.7: Commercial vs. SAT-based ATPG for p100k             | 37 |

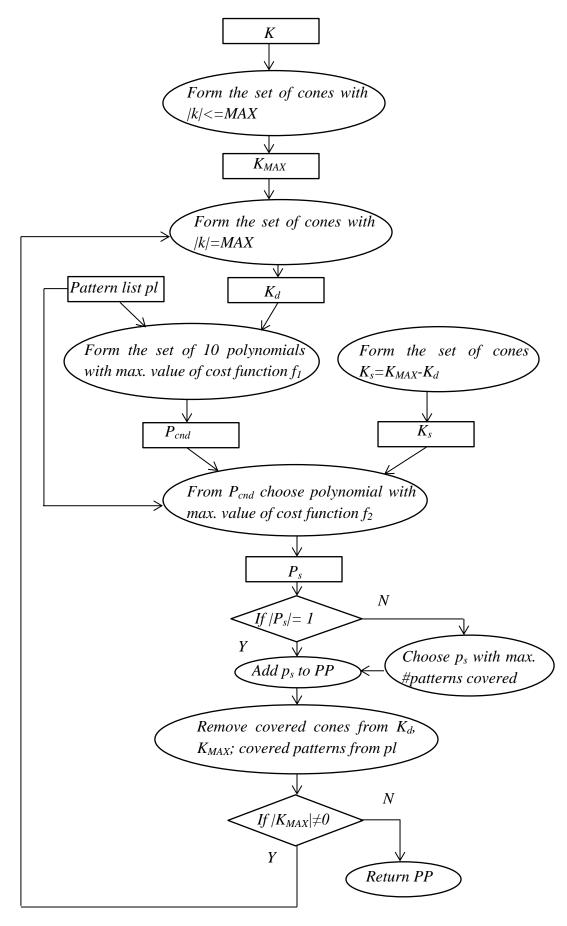

| Figure 5.1: Algorithm for the selection of polynomials          | 41 |

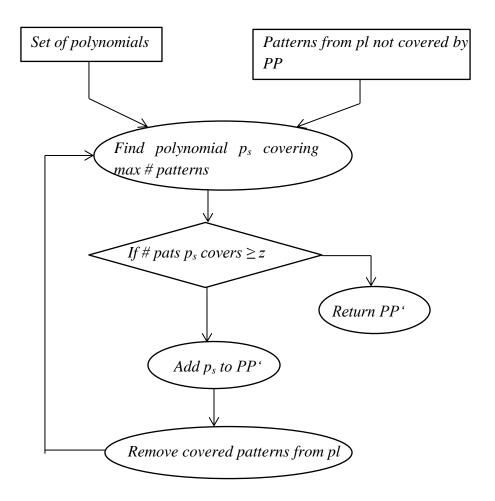

| Figure 5.2: Algorithm for adding extra patterns                 | 46 |

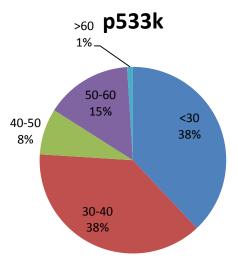

| Figure 6.1: Care bit distribution diagram for p533k             | 60 |

# LIST OF TABLES

| Table 2.1: Sequences generated by LFSR                                            | 16 |

|-----------------------------------------------------------------------------------|----|

| Table 4.1: Truth table for AND-gate                                               | 33 |

| Table 4.2: Truth table for AND-gate for 4-value logic                             | 34 |

| Table 6.1: Circuits' characteristics [9]                                          | 49 |

| Table 6.2: Results of fault simulation                                            | 50 |

| Table 6.3: ATPG results                                                           | 51 |

| Table 6.4: Distribution of the patterns with different number of care bits        | 52 |

| Table 6.5: Heuristics results for coefficient_cones=1.0, coefficient_patterns=0.0 | 53 |

| Table 6.6: Heuristics results for different coefficients                          | 55 |

| Table 6.7: Results of heuristics with weights consideration                       | 57 |

| Table 6.8: Results of heuristics with user-defined polynomial introduction        | 57 |

| Table 6.9: Single stuck-at fault coverage                                         | 58 |

#### LIST OF ABBREVIATIONS

ATE Automatic Test Equipment

ATPG Automatic Test Pattern Generation

BIST Built-In Self-Test

CUT Circuit under Test

DFT Design for Testability

ET Exhaustive Testing

LFSR Linear Feedback Shift Register

MISR Multiple Input Signature Register

MP-LFSR Multiple-Polynomial LFSR

PET Pseudo-Exhaustive Testing

PI Primary Input

PO Primary Output

P-PET Partial Pseudo-Exhaustive Testing

PPI Pseudo-Primary Input

PPO Pseudo-Primary Output

PRT Pseudo-Random Testing

ROM Read-Only Memory

PRSG Parallel Shift Register Sequence Generator

RA Response Analyzer

SAT Satisfiability

STUMPS Self-Test Using Multiple Input Signature Register and Parallel Shift

Register Sequence Generator

TPG Test Pattern Generator

VLSI Very Large Scale Integration

#### CHAPTER 1

#### INTRODUCTION

#### Contents

| 1.1 Motivation and goals of the work | 7 |

|--------------------------------------|---|

| 1.2 Thesis outline                   | 9 |

# 1.1 Motivation and goals of the work

Testing plays a crucial role in any kind of production. There is a certain risk of the product to be of low-quality when poorly examined. The meaning of the term testing varies depending on the device to be tested. In general sense, testing is a checking of the quality of the item. The results of the testing show whether the product meets all specifications and requirements.

For very large scale integration (VLSI) circuits, testing is a necessity due to possible defect presence. These defects might be caused by material defects, malfunctions of equipment, design errors. On the stage of development, when the design is fabricated for the first time, testing is performed to ensure correctness of the design and meeting of specifications. In mass production, every chip is subjected to manufacturing testing where material defects are of concern. In testing, the representation of the material defect, fault, is used. There exist different fault models to capture the nature of the physical defect logically. The most spread fault model is the stuck-at fault model. In this model, it is assumed that the line is always connected to ground (stuck-at "0") or power supply (stuck-at "1").

VLSI circuits are tested by applying the test patterns to the inputs of the circuit and comparing each of the output to the correct one. The test inputs, or patterns, need to be pre-computed and stored. They also can be generated during the test. Testing of VLSI circuits can be classified to online testing, which takes place during system operation, and offline; external testing and internal, or self-testing. External testing is performed by automatic test equipment (ATE). For the purpose of pattern generation, automatic test pattern generator (ATPG) is used. Internal testing takes advantages of design for testability (DFT) techniques to decrease the cost and the time of testing. DFT is a technique which increases the testability of the design. One well-known application of DFT is built-in self-test (BIST). In BIST, the part of the circuit on a chip tests the circuitry by generating the test patterns and analyzing the output responses of the circuit.

Testing of VLSI circuits can be fault model dependent and fault model independent. Generally speaking, the fault model dependent algorithm creates test for the faults of a pre-defined fault model. In the fault model independent testing, test patterns are generated without targeting specific fault models. The fault model dependent testing has a smaller set of the patterns to be applied, but it is more difficult to generate these patterns; whereas the fault model independent test set is easier to generate, but it ends up with larger number of the patterns to ensure specified fault coverage. Even so a fault model is helpful in the testing; it cannot completely accurately represent the real defect [18]. So, the significant advantage of the fault model independent testing is that it is not constrained to the specific fault model.

As an example of the fault model dependent testing, pseudo-random testing can be named. In *pseudo-random* testing [10], the set of pseudo-random patterns are used to test the circuit. If we have a circuit with n inputs, then the subset of  $2^n$  test patterns is applied. Pseudo-random testing cannot give 100% fault coverage since the circuit contains random-pattern-resistant faults. In order to determine the quality of the test, a fault simulation is required. In addition to that, the number of patterns needed to ensure high fault coverage might be large. This makes the approach impractical.

In order to increase the fault coverage of pseudo-random testing, it is often used as a part of *mixed-mode BIST* scheme. Mixed-mode BIST consists of two phases. The first phase is usually pseudo-random testing covering the most of the faults, and the second is the phase of generation of deterministic test patterns to cover all faults undetected in the first phase, so-called random-pattern resistant faults. The limitations of the fault model to represent a real defect lead us to the consideration of fault-model independent testing.

We will start by introduction of exhaustive testing (ET). Exhaustive testing gives 100% defect coverage, but it requires applying all possible  $2^n$  test patterns to an n-input combinational circuit under test (CUT) and verifying the correctness of the output for each combination. If n is large, exhaustive testing requires too much time and certainly very large number of the test patterns to be applied. This makes the approach unrealizable.

A way to decrease the test time is *pseudo-exhaustive testing* (PET). It uses  $2^w$  test patterns, where w < n. Pseudo-exhaustive testing [11] exercises different kinds of circuit segmentation, and then it tests each segment exhaustively. The time for PET depends on the sizes of segments. The obvious advantage of PET is that it does not require fault simulation or fault modeling [15].

In ET and PET one can obtain 100% defect coverage. However, the sizes of the circuits, as well as the number of primary inputs and outputs are increasing. Mentioned approaches are facing the challenge of generating long test length for today's circuits, and that makes them infeasible. In order to solve this problem *partial pseudo-exhaustive testing* (P-PET) was proposed.

P-PET [9] exercises cone segmentation where each cone is a subcircuit containing

all predecessors of the output of the circuit. In P-PET case, only cones up to a given size *MAX* are tested exhaustively (instead of all the circuit cones as in pseudo-exhaustive testing and instead of exhaustively enumerating of all inputs as in exhaustive testing). After applying P-PET, some faults from the larger than *MAX* cones are left undetected and the desired fault coverage might not be achieved. In order to increase the fault coverage, mixed-mode BIST scheme is needed.

In [9] it was proposed to use P-PET in the first phase of mixed-mode BIST. The benefit of the approach is in obtaining higher fault coverage than in pseudo-random testing while maintaining the handleable test length. After applying P-PET, fewer faults are left for the second phase of mixed-mode BIST in comparison with usage of pseudo-random testing.

The number of the test patterns to be generated in the second phase might still be big to ensure required fault coverage. In BIST we need to store deterministic test patterns on a chip. So, the problem of violating the memory limitations might occur when storing deterministic patterns. Particularly this problem we want to solve in the thesis. We aim at obtainment of higher defect coverage of the first phase and significant decrease of the number of deterministic patterns in the second phase of mixed-mode BIST provided the use of P-PET in the scheme. Hence, less memory is needed to store the patterns.

The goal of the thesis is to encode the deterministic test patterns during P-PET. To accomplish the goal, we need to foresee the faults which would not be detected in the first phase of mixed-mode BIST and to test maximized number of these faults already in P-PET. Thus, we may not need mixed-mode BIST, and P-PET is enough to attain certain level of the fault coverage. This will give a significant improvement in terms of the memory needed to store the test patterns.

#### 1.2 Thesis outline

The introductory part is followed by background information and state of the art in chapter 2. Then the formulation of the problem and the proposed solution are discussed in chapter 3. The described solution flow determines the order of the proceeding chapters. Firstly, the fault classification and deterministic test pattern generation will be considered in chapter 4. Then, we will deal with the process of selection of characteristic polynomials for P-PET in chapter 5. The experimental results will be discussed in chapter 6. Conclusions are made in chapter 7.

### **CHAPTER 2**

#### PRELIMINARIES AND STATE OF THE ART

#### Contents

| 2.1 Basic Definitions                 | . 10 |

|---------------------------------------|------|

| 2.2 Fault model dependent testing     | . 14 |

| 2.2.1 Mixed-mode BIST                 | . 17 |

| 2.3 Fault model independent testing   | . 20 |

| 2.4 Partial Pseudo-Exhaustive Testing | . 23 |

|                                       |      |

In this chapter we will discuss preliminaries necessary for understanding of the problem stated in the thesis and the solution proposed. Firstly, we will introduce basic definitions regarding testing of VLSI circuits as defect, fault, fault model and pattern. We will introduce fault model dependent testing and discuss its advantages and disadvantages. Then we will consider fault model independent testing with its pros and cons. And finally, the problem to be solved will be presented.

#### 2.1 Basic Definitions

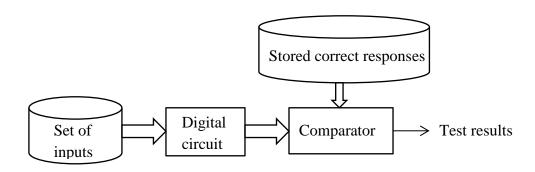

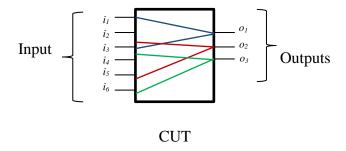

A **testing** of VLSI circuits is an experiment to check the presence of errors. It provides with information about the quality of the chip. Testing procedure consists of applying the set of inputs to the circuit and observing the outputs with subsequent evaluation of the outputs. The concept of testing is depicted in Figure 2.1.

Figure 2.1: The concept of testing

A **defect** is a flaw or physical imperfection that may lead to a fault [6]. The purpose of the testing is to identify the presence of the defects in the circuit. We understand that the circuit has defects if we observe incorrect behavior.

The **sources of defect** are missing or extra material, wear-out, influence of environmental factors, such as temperature, humidity, vibrations causing the aging of components. Defects of interconnections among components can be subdivided to shorts and opens. Short happens when there is a connection which should not be, and open occurs as a result of breaking out of connection.

A **fault** is a representation of a defect reflecting a physical condition that causes a circuit to fail to perform in a required manner [6]. Faults can be classified to permanent, intermittent and transient depending on their duration. Permanent faults once occurred do not vanish. Intermittent faults appear for some periods of time. Transient faults arise one time and often are caused by environmental factors. Later on we will talk about permanent faults only.

A **fault model** is a logical representation of the fault. The fault model introduction makes analysis of the testing possible and also limits the scope of the faults to be considered. There exist different kinds of fault models. There are stuck-at fault model [34] (stuck-at "0" or stuck-at "1") when there is a permanent short with ground or power; bridging fault model [12] in case of the short between two signal lines; CMOS transistor stuck-open [16] when transistor is stuck in the open state; and CMOS transistor stuck-short [20] when transistor is permanently shorted; memory faults [30] and delay faults [41].

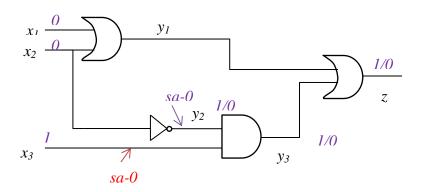

**Stuck-at fault** model is the most popular fault model. It can be used for modeling many defects, it is technology independent, and it is simple. There are single stuck-at faults and multiple stuck-at faults. In the single stuck-at fault model, one line is assumed to be stuck-at "0" or "1". For example, in the circuit depicted in Figure 2.2, the line  $x_3$  is stuck-at "0". In multiple stuck-at fault models, several lines are faulty at the same time. In order to identify the presence of the fault in a circuit, the test inputs which can detect the fault need to be applied. The set of inputs is composed of so-called patterns.

A **pattern** is an assignment of the inputs of the circuit under test. One can distinguish between **care bits** (or specified bits) which are either logic "0" or "1", and **don't care bits** (or unspecified bits) represented by "X". In the case of care bits, specific input must be set to the value of the care bit in order to detect particular fault. In the case of don't care bit, the input can be set either to "0" or "1" without influencing on the detection of the fault.

The pattern can detect the fault if the output of the faulty circuit is different from the output of the fault-free circuit when applying this pattern. In other words, if z is the output of the fault-free circuit and  $z_f$  is the output of the faulty circuit, then particular pattern tests the fault if  $z \oplus z_f = 1$ .

Consider the combinational circuit consisting of primitive logic gates such as

AND, OR and NOT depicted in Figure 2.2. The circuit output function is  $z = (x_1 + x_2) + \overline{x_2}x_3$ . Assume that there is stuck-at "0" on the input line  $x_3$ . The faulty output function will be  $z_f = x_2 + x_3$ . Then, in order to detect this fault we need to have (2.1).

$$z \oplus z_f = (x_1 + x_2) + \overline{x_2}x_3 + (x_1 + x_2) = \overline{x_2}x_3 = 1$$

(2.1)

So, to assure that  $\overline{x_2}x_3 = 1$ , it is necessary to have at the same time  $x_2=0$  and  $x_3=1$ . The value of  $x_1$  is not important, it can be either "0" or "1". Consequently, the pattern detecting the fault will be X01.

**ATPG** (Automatic test pattern generation/generator) is an electronic design automation technology to generate test patterns to be applied to the circuit in order to ascertain the presence or absence of the fault at some location of the circuit. In the process of ATPG, we can distinguish two main concepts. There are *fault activation* and *fault propagation*.

Consider the same circuit in Figure 2.2. Assume there is stuck-at "0" on the line  $y_2$ . We need to perform **fault simulation**, that is simulating of the circuit without this fault and with the presence of fault. Applying the test pattern 001, we get the output of the fault-free circuit z=1. The output of the faulty circuit is  $z_f=0$ . The test pattern 001 *activates* the fault stuck-at "0" on the line  $y_2$  if it generates the error by creating the value on the line  $y_2$  different from the value of assumed fault. And then the resulting signal value, or the fault effect, is propagated to the primary output. The propagation path in our example is  $y_2$ ,  $y_3$ , z.

Figure 2.2: Combinational circuit

A **fault coverage** is a percentage of the faults detected after the test is performed. Fault coverage is determined by fault simulation. After performing the fault simulation, we have information regarding detected and undetected faults. Fault coverage is defined by equation (2.2). In order to calculate the fault coverage, we divide the number of detected faults to the total number of faults.

$$Fault coverage = \frac{\#detected faults}{Total \# faults}$$

(2.2)

The fault coverage evaluates the effectiveness and quality of the test. Fault coverage of 100% cannot be achieved if the circuit contains undetectable faults. For undetectable faults, it is not possible to find the pattern to differentiate the fault-free circuit from the faulty circuit. In this case, we will refer to effective fault coverage or test coverage calculated by formula (2.3). The effective fault coverage is calculated by division of the number of detected faults into subtracted by the number of undetectable faults total number of faults. The number of undetectable faults is also determined by fault simulation.

$$Effective fault coverage = \frac{\# detected faults}{Total \# faults - \# undetectable faults}$$

(2.3)

**ATE** (automatic test equipment) is equipment that performs testing using automation to perform measurements, obtain and evaluate the test results. ATE realizes the test by transporting and applying the test patterns and by evaluation of responses which are transported back to ATE. ATE is very precise equipment, but it is also very expensive. ATE is used for external testing. In internal testing the techniques called design for testability (DFT) are exploited.

**DFT** is a technique that ensures testability of the design. Testability of the design can be determined by controllability and observability.

**Controllability** is an ability to set some internal circuit nodes to specific values.

**Observability** is an ability to observe the values of internal nodes.

By increasing the level of testability of the design, the decrease in the test time and the cost can be reached in internal testing. On the other hand, additional hardware is required that affects the area overhead and causes delays. So, the balance is needed between introducing DFT and the gain which can be achieved by DFT.

Among DFT techniques should be mentioned ad hoc techniques [13] (initialization [13], test points insertion [6], partitioning of the circuit [13]), scan-based design [6] and boundary scan [34]. Scan design is widely used approach, method of distributing the test patterns to the internal circuit under test and responses to the outputs of the circuit by means of the scan chains.

A **scan chain** is a chain of registers or flip-flops allowing easy to read and write the content. The test patterns are shifted in via the scan chain and results are shifted out to the chip output pins.

One way of application of DFT is built-in self-test (BIST). In BIST, the part of the circuit tests itself. BIST scheme makes testing easier, faster and cheaper. In BIST, additional hardware and software are needed to enable self-checking.

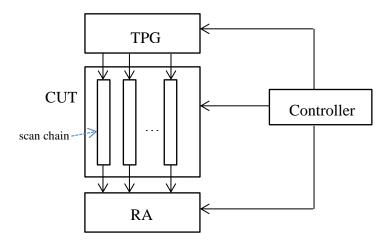

Having discussed the basic terms, we can introduce typical BIST scheme. The typical BIST application hardware includes test pattern generator (TPG), response analyzer (RA), circuit under test (CUT) and controller (Figure 2.3).

It should be noted that in BIST not only the test pattern generator is on the chip, but also the response analyzer. The whole process of testing is under regulation of controller. In this scheme, TPG generates the test patterns to be applied to CUT; the outputs of CUT are evaluated by RA by comparing them to the correct outputs. It is of great importance the way TPG generates the patterns since it affects the fault coverage, test time and test cost.

Figure 2.3: General BIST hardware scheme

Testing can be based on fault model or can be independent of fault model. In relation to that, testing is classified to *fault model dependent* testing and *fault model independent* testing.

## 2.2 Fault model dependent testing

Fault model dependent testing is entirely based on the assumed fault model. It often results in a shorter test length. Fault model dependent testing has limitations of fault model since fault model cannot precisely reflect the nature of the fault. In addition to that, in order to perform thorough test of the circuit, one need to consider several fault models that increases the test length and time. Another disadvantage of fault model dependent schemes is that they often require fault simulation to be performed which is expensive. Test pattern generation for fault model dependent testing can be performed by ATPG. In this case, ATPG generates patterns for the considered list of the faults of particular fault model.

We will consider fault model dependent testing on the example of *pseudo-random testing*. In pseudo-random testing, patterns have many characteristics of random patterns, but they are generated deterministically, that is why the method is called pseudo-random. If we have the circuit with *n* inputs, pseudo-random TPG generates the

subset of  $2^n$  input combinations.

Pseudo-random patterns can be generated by cellular automata or linear feedback shift register (LFSR). Cellular automata have better randomness property. Cellular automata consist of the cells with forward and backward connections. If we denote by  $C_i$  the state of the current cell, then the next state of  $C_i$  will be determined by  $(C_{i-1}, C_i, C_{i+1})$ , where  $C_{i-1}$  and  $C_{i+1}$  are neighboring cells. More information regarding cellular automata can be found in [35].

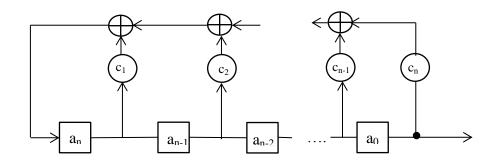

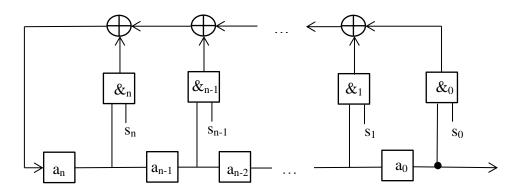

We will concentrate on using LFSR as a pattern generator for pseudo-random testing. For that, we need basic knowledge of the LFSR. Mathematical background of LFSR is presented in [36]. There are two types of the LFSR depending on where XOR-gates are placed. In Figure 2.4 the external type LFSR is presented, and in Figure 2.5 the internal type LFSR is depicted.

Figure 2.4: External type linear feedback shift register

Figure 2.5: Internal type linear feedback shift register

A LFSR consists of the number of D-type flip-flops  $a_0...a_n$  and exclusive OR (XOR) gates. The configuration of the LFSR is determined by the feedback or characteristic polynomial  $P(x) = 1 + c_1x + c_2x^2 + ... + c_nx^n$  where  $c_1, c_2,...,c_n$  are feedback coefficients of the value '0' or '1'signifying the presence or absence of connection. The degree of characteristic polynomial is equal to the number of flip-flops of the LFSR. The LFSR generates periodic sequences with maximal period of  $2^n$ -1 where n is the degree of characteristic polynomial.

A **primitive polynomial** is a characteristic polynomial of the LFSR generating maximum-length sequence. Primitive polynomial p(x) has the property that if we

compute the remainders of the polynomial division of increasing powers of x to p(x) (i.e., x modulo p(x),  $x^2$  modulo p(x),  $x^3$  modulo p(x) and so on), we will obtain all possible non-zero polynomials of degree less than p(x).

A **seed** is an initial state of a LFSR. On the next cycle all seed elements are shifted by one position and new seed element is calculated by applying XOR operation on the seed elements from the previous cycle specified by the feedback polynomial.

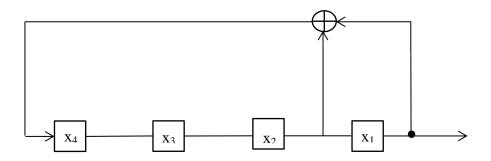

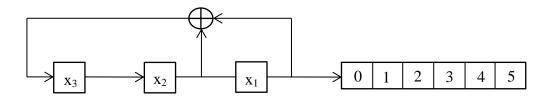

Consider the LFSR depicted in Figure 2.6. The feedback polynomial of this LFSR is  $P(x) = x^4 + x^1 + 1$ . P(x) is a primitive polynomial. The degree of this primitive polynomial is equal to 4. We will run this LFSR for  $(2^4-1) = 15$  cycles and fill in Table 2.1.

Figure 2.6: Example of external linear feedback shift register

| Clock cycle |                         |                         |                         |                         |

|-------------|-------------------------|-------------------------|-------------------------|-------------------------|

| 0           | $\chi_4$                | $x_3$                   | $x_2$                   | $x_1$                   |

| 1           | $x_2 + x_1$             | $\chi_4$                | $\chi_3$                | $x_2$                   |

| 2           | $x_3 + x_2$             | $x_2 + x_1$             | $\chi_4$                | <i>X</i> <sub>3</sub>   |

| 3           | $x_4 + x_3$             | $x_3 + x_2$             | $x_2 + x_1$             | $\chi_4$                |

| 4           | $x_2 + x_1 + x_4$       | $x_4 + x_3$             | $x_3 + x_2$             | $x_2 + x_1$             |

| 5           | $x_3 + x_1$             | $x_2 + x_1 + x_4$       | $x_4 + x_3$             | $x_3 + x_2$             |

| 6           | $x_4 + x_2$             | $x_3 + x_1$             | $x_2 + x_1 + x_4$       | $x_4 + x_3$             |

| 7           | $x_2 + x_1 + x_3$       | $x_4 + x_2$             | $x_3 + x_1$             | $x_2 + x_1 + x_4$       |

| 8           | $x_4 + x_3 + x_2$       | $x_2 + x_1 + x_3$       | $x_4 + x_2$             | $x_3 + x_1$             |

| 9           | $x_4 + x_3 + x_2 + x_1$ | $x_4 + x_3 + x_2$       | $x_2 + x_1 + x_3$       | $x_4 + x_2$             |

| 10          | $x_4 + x_3 + x_1$       | $x_4 + x_3 + x_2 + x_1$ | $x_4 + x_3 + x_2$       | $x_2 + x_1 + x_3$       |

| 11          | $x_4 + x_1$             | $x_4 + x_3 + x_1$       | $x_4 + x_3 + x_2 + x_1$ | $x_4 + x_3 + x_2$       |

| 12          | $x_1$                   | $x_4 + x_1$             | $x_4 + x_3 + x_1$       | $x_4 + x_3 + x_2 + x_1$ |

| 13          | $x_2$                   | $x_1$                   | $x_4 + x_1$             | $x_4 + x_3 + x_1$       |

| 14          | $x_3$                   | $x_2$                   | $x_1$                   | $x_4 + x_1$             |

| 15          | $x_4$                   | $\chi_3$                | $x_2$                   | $x_1$                   |

Table 2.1: Sequences generated by LFSR

The values from the last column fill in the scan chain. In Table 2.1 the shifting can

be easily observed and calculation of new element by applying XOR operation on the forth and the third column. The values on the  $15^{th}$  cycle are the same as initial. This proves that P(x) is indeed the primitive polynomial.

LFSR tends to generate equal number of "0"s and "1"s. For some circuits the biased distribution of "0"s and "1"s is preferred. This is explained by the presence of **random pattern resistant faults**. Random pattern resistant faults have low detection probability; they are detected by only a few patterns. As a result, the presence of random pattern resistant faults negatively influences the fault coverage.

There exist several ways to tackle this problem. Firstly, in order to reduce random pattern resistivity, weighted TPG can be applied. And, secondly, the fault coverage can be improved by mixed-mode BIST scheme.

In **weighted TPG** ([34], [42]) the distribution of "0"s and "1" in the pattern depends on the weight. Different weights should be pre-computed for the circuitry since for each part of the circuit specific distribution has better results. As TPG, LFSR with combinational logic is used [29].

#### 2.2.1 Mixed-mode BIST

**Mixed-mode BIST** scheme consists of two phases. The first phase is pseudorandom testing during which the large part of the faults is tested, and the second is applying deterministic patterns for the random pattern resistant faults which were not detected in the first stage.

For the purpose of deterministic pattern generation, automatic test pattern generator is used. All deterministic patterns need to be stored in a ROM (Read-only memory). The size of the pattern set directly influence the size of the memory. Sometimes the size of the pattern set to be stored violates the memory requirements. In order to reduce the memory needed to store the patterns, compression techniques are used.

As we already know, the pattern consist of care bits, which are important for particular fault detection, and don't care bits, which can be either "0" or "1". Compression technique takes advantage of don't care bits assigning to them certain logic values which enables compression. Or, in other words, compression mechanism looks for the patterns which differ in a small number of bits and tries to combine them.

Different approaches have been proposed for the test data compression. They can be classified to code-based schemes (e.g., Dictionary code [5], Huffman code [3]), linear-decomposition-based schemes (e.g., linear LFSR reseeding based schemes), broadcast-scan-based schemes [6]. In mixed-mode BIST, the deterministic test patterns can be encoded in the sequence of pseudo-random patterns by bit-flipping or bit-fixing approaches [37], [38], [1]. We will consider in more details LFSR reseeding as very

popular and elegant solution for compression.

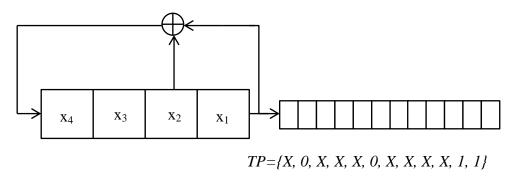

In LFSR reseeding [1], deterministic test patterns are encoded into seeds. After initializing the LFSR with pre-computed seed, LFSR generates deterministic test pattern and fills in the scan chain with the pattern after m cycles, where m is the length of the scan chain. A seed can be computed by solving the system of linear equations based on the feedback polynomial of LFSR, where each specified bit of the pattern is represented by an equation in terms of the seed variables [7].

In Figure 2.7 the LFSR with feedback polynomial  $P(x) = x^4 + x^1 + 1$  is depicted. We start with running the LFSR with seed elements as variables and filling in the scan chain.

Figure 2.7: LFSR with scan chain

Then we compose the system of linear equations according to the bits of the given pattern. The system of linear equations for the test pattern TP is represented by (2.4).

$$\begin{cases} x_1 = 1 \\ x_2 = 1 \\ x_3 + x_4 = 0 \\ x_1 + x_2 + x_3 = 0 \end{cases}$$

(2.4)

In our example, the system of equations (2.4) has the solution:  $x_1=1$ ,  $x_2=1$ ,  $x_3=0$ ,  $x_4=0$  which is the seed needed to encode the pattern TP. The number of care bits in the pattern determines the number of equation. The less number of care bits in the pattern, the more probability to find the seed.

In [1] Könemann showed that single-polynomial LFSR should have the length of (s+20) in order to find the seed for the pattern with s care bits with the probability less than  $10^{-6}$ . Then multiple-polynomial LFSRs [2] (MP-LFSR) were introduced. Using MP-LFSR, test pattern with s care bits can be encoded with (s+4) bits.

**MP-LFSR** is an LFSR with reconfigurable feedback network, where AND-gates are used to control the feedback polynomial.

Multiple-polynomial LFSR gives more freedom and flexibility during pattern

encoding in the sense that hardware is programmable with the seed, and polynomial information can be modified [7].

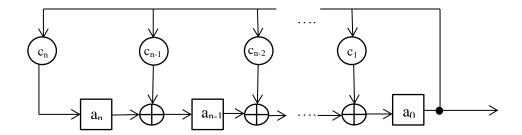

Figure 2.8: Multiple-polynomial LFSR

In Figure 2.8 the MP-LFSR is illustrated. There the sequence of bits  $s_0$ ,  $s_1$ ,...,  $s_n$  are used to determine the resulting feedback polynomial. If the bit is "0", the output from AND-gate is also "0", and corresponding branch is not present. As we can see in Figure 2.8, the hardware overhead in comparison with the single-polynomial LFSR consists of only AND-gates.

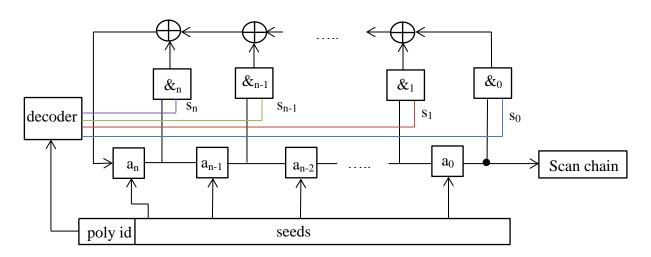

In Figure 2.9 the encoding scheme based on the reseeding of the LFSR is presented. The seeds and corresponding polynomial identifiers are stored in a ROM. Polynomial identifier is used to configure the feedback network of the LFSR.

Figure 2.9: LFSR reseeding scheme

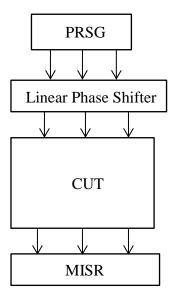

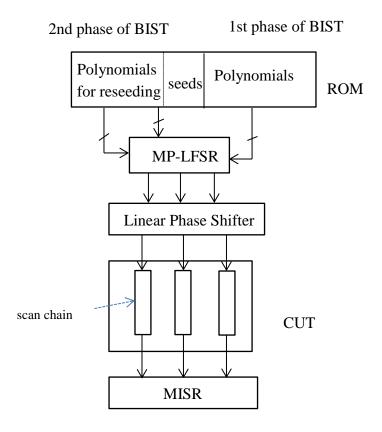

The basic hardware scheme for BIST is Self-Test Using Multiple Input Signature Register (MISR) and Parallel Shift Register Sequence generator (PRSG) (STUMPS), and in the work presented we will also use this scheme.

The general STUMPS scheme is illustrated in Figure 2.10. In STUMPS, PRSG

[46] is used for the test pattern generation. Multiple scan chains are applied for the purpose of minimization of the test time. Scan chains may have different lengths. In this scheme, MISR is used to compact responses [33] since the outcome of CUT should be compacted, otherwise processing of huge amount of data becomes impossible. In this case, the circuit is tested by comparing the output signature with the correct precomputed signature. For this purpose the signature, that is the compressed form of the response, is calculated. Further information regarding response compaction can be found in [25], [26], [27].

Figure 2.10: General STUMPS scheme

PRPG loads the scan chains in parallel. The system clocks are triggered. Then the test responses are shifted to the MISR, at the same time new patterns are shifted in. To improve the randomness of the PRPG, linear phase shifter may be used [46].

#### 2.3 Fault model independent testing

Fault model independent testing does not have the limitations of the fault models. This kind of testing may result in a long test length because it does not target specific faults. One example of fault model independent testing is exhaustive testing.

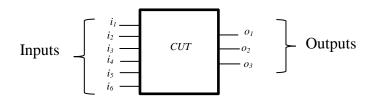

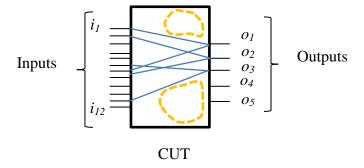

In exhaustive testing, all possible  $2^n$  input combinations are applied to the circuit with n inputs. Consider the circuit under test in Figure 2.11. This circuit has six inputs and three outputs. One should apply  $2^6 = 64$  test patterns to test the circuit exhaustively.

Test patterns for exhaustive testing can be generated by binary counters or LFSRs. Since the order of the patterns generated is not important, it is better to use LFSRs [39].

LFSRs require less hardware than binary counters.

Figure 2.11: Circuit under test

If the number of inputs is small, then exhaustive testing is very useful because 100% of all combinational defects are guaranteed to be detected. But in the case of the large number of inputs, exhaustive test ends up with long test length which is infeasible. In order to have the benefits of exhaustive testing and less number of the test patterns, pseudo-exhaustive testing was proposed.

Pseudo-exhaustive testing (PET) [31], [43] exercises different kinds of circuit segmentation. Segment is a subcircuit. Each segment is tested exhaustively. In pseudo-exhaustive testing, one can achieve complete detection of combinational defects. The advantage of pseudo-exhaustive testing is that it requires less number of the test patterns than exhaustive testing. Segmentation of the circuit can be logical (cone and sensitized path segmentation) and physical (hardware) [13].

We will start with consideration of the cone segmentation. This approach is also called *verification testing* [15].

An **output cone** is a sub-circuit containing all structural predecessors of one primary output.

Figure 2.12: Cone segmentation

In the case of the cone segmentation, each cone is tested exhaustively, and all cones are tested concurrently. If we have m-outputs circuit, than this technique defines

*m* cones. The cone segmentation example is shown in Figure 2.12.

The **size of the cone** is determined by the number of the inputs in the cone. Consider the circuit in Figure 2.12; it has six inputs and three outputs. We divided the circuit into three cones (by the number of outputs). The size of each cone is equal to three. To test the circuit we will need  $3*2^3=24$  patterns instead of 64 patterns as in exhaustive testing.

Verification testing cannot be feasible if the circuit has outputs depending on too many circuit inputs [43]. If the circuit is too big and complex, three other techniques are used: sensitized path segmentation, hardware partitioning and partial hardware partitioning.

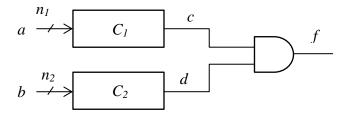

To start off with, we will consider sensitized path segmentation [31]. A line in a circuit whose value in the test changes in the presence of fault is said to be **sensitized** to the fault by the test.

#### **Sensitized path** is a path composed of sensitized lines.

In sensitized path segmentation, some inputs are set to the values, so that particular segments are triggered. Consider combinational circuit in Figure 2.13.  $C_1$  and  $C_2$  are sub-circuits. In order to test  $C_1$  exhaustively, one need to apply  $2^{n_1}$  test patterns to a. At the same time we need to set b to some value so that d=1. Sensitized path in this case is c-f.  $C_2$  can be tested in a similar way. Totally, we will need  $2^{n_1} + 2^{n_2} + 1$  patterns to test the circuit [13] instead of  $2^{n_1+n_2}$  patterns necessary for exhaustive testing.

Figure 2.13: Testing via sensitized path segmentation [13]

Sensitized path segmentation technique requires high computational time. It may result in incomplete defect coverage because of the possible defects presence between the segments [14].

In hardware partitioning technique [31], [28], hardware is added to the circuit to control and observe the segment's inputs and outputs. So, the circuit is divided into small sub-circuits. Each subcircuit is directly controllable and observable. One way is to use multiplexer partitioning. The disadvantage of adding extra hardware is in the speed decrease and the cost of implementation.

In partial hardware partitioning [44], circuit's inputs indirectly control the segment's input, and added hardware directly observes the segment output. Partial hardware partitioning has features of hardware partitioning and sensitized partitioning. Test patterns are applied to the primary inputs as in the sensitized partitioning. But instead of sensitizing the segment outputs to circuit outputs, extra hardware is added to allow the segments outputs to be observed directly as in the hardware partitioning. This approach results in lower hardware overhead and less test set generation complexity [44].

There are number of ways to generate test patterns in PET: syndrome-driver counter [19], constant-weight counter [15], combined LFSR and shift register [21], combined LFSR and XOR gates, condensed LFSRs [22], cyclic LFSRs [23], [24]. These methods in some cases may result in a long test length, which is not applicable for today's circuits.

Summing up, PET results in a less number of test patterns than exhaustive testing, and it is fault model independent. PET attains mentioned benefits by means of logical or hardware segmentation. If the circuit is very large, cone segmentation has infeasible test length. In order to tackle this problem, hardware segmentation was proposed. The disadvantages of hardware segmentation technique are in the additional delays and in the cost increase. In order to have the benefits of cone segmentation (no hardware overhead) and make it feasible for larger circuits, partial pseudo-exhaustive testing was proposed.

# 2.4 Partial Pseudo-Exhaustive Testing

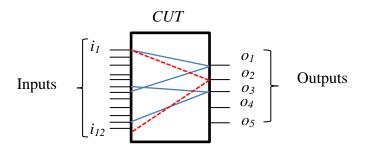

Partial pseudo-exhaustive testing (P-PET) [9] is a technique that is based on the cone segmentation. In P-PET, only cones up to specified *MAX* size are tested exhaustively. So, the problem of long test length is tackled there. Cone segmentation technique becomes feasible.

Figure 2.14: Cone segmentation for P-PET

Consider the circuit in Figure 2.14. If we assume that MAX=6, then we start with exhaustive testing of the blue cones of the size 6. The red cone will not be tested

exhaustively since the size of it is larger than 6.

After testing exhaustively the cones up to *MAX* size, some faults from the larger cones will not be detected. It should be noted that for the faults from the larger cones, P-PET behaves like pseudo-random testing. In order to target the faults from the larger cones which were not detected by P-PET, deterministic patterns need to be generated. So, P-PET cannot be used alone but in a mixed-mode BIST scheme where in the first phase is P-PET instead of pseudo-random testing. Consequently, P-PET scheme is based by half on fault model independent testing (first phase of mixed-mode BIST) and by other half on fault model dependent testing (second phase of mixed-mode BIST).

Consider STUMPS architecture depicted in Figure 2.15 for P-PET testing. Pattern generation for P-PET is implemented by MP-LFSR. The corresponding characteristic polynomials are stored in a ROM to update MP-LFSR. So, in the first stage of the mixed-mode BIST, MP-LFSR, configured by stored characteristic polynomials, generates test patterns to tests all cones up to *MAX* size exhaustively.

Figure 2.15: STUMPS architecture for P-PET testing

Then for the faults from the larger than *MAX* cones which were not detected by the first stage, deterministic test patterns are encoded by LFSR reseeding technique. Seeds and characteristic polynomials are also stored in a ROM. In the second phase of the mixed-mode BIST, the deterministic test patterns generated by MP-LFSR configured by corresponding characteristic polynomial and initialized with particular

seed are applied.

Characteristic polynomials for MP-LFSR are pre-calculated from the circuit structure. The process of choosing feedback polynomials for P-PET is NP-complete problem, and set covering heuristics is applied to solve the problem efficiently. In [9] the goal was set to obtain the smallest possible number of feedback polynomials. In this case, the test application time will be minimal, and less memory is need to store the polynomials.

Formulating the problem from [9] more formally, let  $K_c$  be the set of cones of the circuit up to the size MAX. Let P be the set of polynomials up to degree MAX. The aim is to find the smallest set of polynomials  $P_s$ , the subset of the set P, which will cover the set of the cones  $K_c$  (2.2).

$$\forall k \in K_c \exists p \in P_s \ p < k \tag{2.2}$$

We will use the following designation p < k to denote that the polynomial p tests, or covers, the cone k. It is said that the feedback polynomial of degree r tests the cone k which has s inputs when  $2^r-1$  different patterns generated cover  $2^s-1$  different assignments of the cone. On the other hand, this approach is very time consuming and not applicable for the large set of polynomials.

For this task Barzilai's Theorem [32] is very helpful.

#### Barzilai's theorem:

Let  $(a_{\tau})_{\tau \geq 0}$  be a shift register sequence generated by a primitive polynomial p of degree r. The set  $T=(a_0,...,a_{r-1}), (a_1,...,a_r), ...,(a_2^r, a_0,...,a_{r-2})$  is an exhaustive enumeration of the assignment of  $(i_1,...,i_s)$ , if the remainder classes  $(X^{i_1} \mod p), ..., (X^{i_s} \mod p)$  over GF(2) are linearly independent. Consequently, to determine whether the polynomial covers the cone we need to check the linear independency of remainders  $(X^{i_1} \mod p), ..., (X^{i_s} \mod p)$  [32].

Figure 2.16 shows an example for checking whether particular feedback polynomial can cover the cone.

Figure 2.16: LFSR and scan chain

Depicted in Figure 2.16 LFSR, has feedback polynomial  $P(x) = x^3 + x^2 + 1$ . In this example, we are considering the cone  $k = \{0, 2, 4\}$ . So, according to Barzilai's Theorem, we need to calculate remainders (2.5).

$$(x^{0}) \bmod (x^{3} + x^{2} + 1) = (1)$$

$$(x^{2}) \bmod (x^{3} + x^{2} + 1) = (x^{2})$$

$$(x^{4}) \bmod (x^{3} + x^{2} + 1) = (x^{2} + x + 1)$$

$$(2.5)$$

The remainders (1),  $(x^2)$ ,  $(x^2+x+1)$  are linearly independent, consequently, the feedback polynomial  $P(x) = x^3 + x^2 + 1$  covers the cone k.

If we consider the cone  $k_I = \{0, 2, 4, 5\}$ , the corresponding remainders presented in (2.6) are linearly dependent.

$$(x^{0}) \bmod (x^{3}+x^{2}+1) = (1)$$

$$(x^{2}) \bmod (x^{3}+x^{2}+1) = (x^{2})$$

$$(x^{4}) \bmod (x^{3}+x^{2}+1) = (x^{2}+x+1)$$

$$(x^{5}) \bmod (x^{3}+x^{2}+1) = (x+1)$$

$$(2.6)$$

Consequently, the polynomial  $P(x) = x^3 + x^2 + 1$  does not cover the cone  $k_1$ .

Having discussed the principles of P-PET, we continue with advantages of P-PET. Usually in the first phase of the mixed-mode BIST, pseudo-random test is used. Applying P-PET in the first phase of the mixed-mode BIST results in the increased defect coverage and lower number of deterministic patterns in the second phase of mixed-mode BIST.

The problem with this realization may arise when in the second phase of mixed-mode BIST, one need to encode large number of deterministic patterns and store them on a chip. Memory requirements may limit the storage for deterministic patterns. That is the reason why we want to tackle this problem and try to target some part of the faults from the larger than *MAX* cones which cannot be covered by P-PET already during P-PET stage. Or, in other words, we want to encode the deterministic patterns, which would be generated in the second phase of the mixed-mode BIST for the uncovered faults from the larger cones, in P-PET. So, the defect coverage of P-PET will be increased. This can be done by appropriate selection of the feedback polynomials for P-PET pattern generation. In some cases, only P-PET would be enough to reach certain fault coverage, in others- less number of patterns need to be encoded and stored.

## **CHAPTER 3**

### PROBLEM FORMULATION AND SOLUTION FLOW

#### Contents

| 3.1 Problem formulation | 27 |

|-------------------------|----|

| 3.2 Solution flow       | 28 |

In this chapter we will provide detailed problem description and formulation of the goal to be reached in the thesis. We will also discuss the proposed solution flow to achieve the objective.

## 3.1 Problem formulation

In mixed-mode BIST scheme, two phases are distinguished. In the first phase, patterns generated on a chip are applied to the circuit. For the faults which were not detected in the first phase, deterministic test patterns are stored on a chip. In the second phase, these stored patterns are used to reach the certain fault coverage.

P-PET in the first phase of mixed-mode BIST tests exhaustively cones up to some *MAX* size. In Figure 3.1 the cones of the circuit up to *MAX* size are shown with the blue color. For the faults from the larger than *MAX* cones, P-PET behaves like pseudorandom test. In Figure 3.1 the possible locations of these faults are represented by yellow areas.

Figure 3.1: Cone segmentation in P-PET

The majority of the faults are already covered by P-PET. For the faults not detected by P-PET, deterministic test patterns need to be generated. One possibility is to store deterministic test patterns on a chip. Another way is to encode these patterns in P-PET. The degree of freedom to choose primitive polynomials to cover all cones up to MAX size can be exploited. So, our goal can be formulated as follows: we aim to select polynomials for P-PET pattern generation such that the set of undetected faults is minimized (or the number of detected faults from the larger than MAX cones is maximized).

The goal formulation can be further concretized. We can either aim to have the same number of polynomials as in P-PET where only cones up to *MAX* size are targeted, or to obtain higher fault coverage by means of adding extra polynomials. So, we can distinguish two subgoals:

- 1) Selection of minimal number of polynomials for P-PET so that the number of undetected faults is minimized.

- 2) Selection of polynomials for P-PET so that the number of undetected faults is minimized (the number of polynomials can be more than minimal)

We will define the problem more formally.

Given the circuit to be tested, we denote  $K_{MAX}$  the set of cones of the circuit up to the size MAX. The set of cones larger than MAX is denoted as  $K_{LMAX}$ , and F stands for the set of the faults from  $K_{LMAX}$ . We also have the set of polynomials up to degree MAX,  $P_{MAX}$ . Let  $K_p = \{k \in K_{MAX}, p < k\}$  be the set of cones from  $K_{MAX}$  tested by the polynomial p.

The aim is to find the set of polynomials  $P_s \subset P_{MAX}$  such that  $K_{MAX} = \bigcup_{p \in P_s} K_p$ , and the set of undetected faults  $F_{ud}$  is minimized.

#### 3.2 Solution flow

We aim to target the faults from the set  $F_{ud}$  during the selection of polynomials for P-PET. But the genuine set of the faults  $F_{ud}$  can be obtained only after applying P-PET. We can exploit the fact that P-PET for the set of faults F from the larger than MAX cones behaves like pseudo-random test and classify the faults from the set F into hard-to-detect faults (not detectable by applying pseudo-random patterns) and easy-to-detect faults (detectable by pseudo-random pattern sequence). This fault classification can be performed by fault simulation of the large number of pseudo-random patterns (for example,  $10^6$  patterns). It is important to note that the set of hard-to-detect faults will be a superset of the set  $F_{ud}$  since the number of patterns applied in the multiple-polynomial scheme of P-PET is larger than  $10^6$ .

Having obtained the list of hard-to-detect fault, it is necessary to encode these faults by test patterns so that we can take them into account while selecting the feedback polynomials for P-PET. In the step of checking whether some polynomial can cover the pattern, we will use the idea of MP-LFSR reseeding presented in the second chapter. The polynomial covers the pattern, if there is such a seed that LFSR will generate this particular pattern, given the configuration of the LFSR represented by certain feedback polynomial. It is necessary to emphasize that the less number of care bits the test pattern has, the bigger the probability to find the polynomial covering the pattern. This was discussed in subsection 2.2 of chapter 2. So, for us it is important to generate test patterns with minimized number of care bits.

Given the set of cones up to MAX size, the set of polynomials up to degree MAX, the pattern list with minimized number of care bits, we aim to select the polynomials, so that they cover all the cones up to the size MAX, and the number of deterministic test patterns covered is maximized. This is a set covering problem where heuristics is applied to solve it efficiently.

To sum up, the following steps will be taken to accomplish the goal:

- 1) Fault classification on hard-to-detect and easy-to-detect faults

- 2) Generation of the test patterns for hard-to-detect faults with minimized number of the care bits

- 3) Set covering heuristics to choose feedback polynomials for P-PET TPG

In chapter 4 and 5, these steps are described in details.

#### **CHAPTER** 4

#### FAULTS CLASSIFICATION AND TEST PATTERN GENERATION

#### Contents

| 4.1 Fault classification on hard-to-detect and easy-to-detect faults    | 30 |

|-------------------------------------------------------------------------|----|

| 4.2 Generation of deterministic test patterns for hard-to-detect faults | 32 |

| 4.2.1 ATPG with minimum number of care bits                             | 32 |

| 4.2.2 Commercial ATPG                                                   | 35 |

|                                                                         |    |

In this chapter we will consider the first two steps necessary to achieve the formulated goal. In the first subsection, we will deal with fault classification and obtainment of the list of hard-to-detect faults. In the second subsection, we will discuss test pattern generation process with minimized number of care bits for the list of hard-to-detect faults.

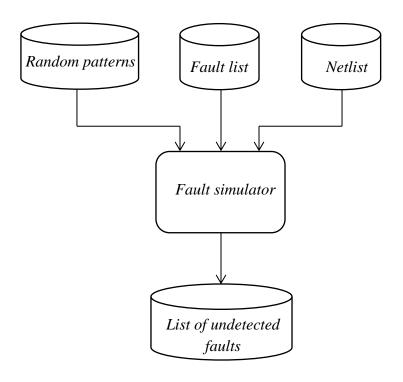

# 4.1 Fault classification on hard-to-detect and easy-to-detect faults

In this subsection, we will discuss in details the first step in the process of achieving the goal described in chapter 3. In general P-PET, all faults from the cones up to MAX size are detected. For the faults from the larger than MAX cones, P-PET acts like pseudo-random test. Hence, some faults from the larger than MAX cones are also detected, some of them are not detected. We need to obtain a safe approximation to the set of the faults  $F_{ud}$  not detected by P-PET.

We will approach the problem by classification of the faults from set F, the set of the faults from the larger than MAX cones, into detectable by pseudo-random test sequence (easy-to-detect faults) and not detectable by pseudo-random test (hard-to-detect faults).

This classification is achieved by performing the fault simulation when applying the large number of random patterns. Figure 4.1 illustrates the idea. Given the circuit netlist, the list of faults from the set F of stuck-at model, we simulate the circuit in the presence of a million of random patterns. The resulting list of undetected faults will be equivalent to the list of hard-to-detect faults. All detected by the fault simulation faults are identical to the easy-to-detect faults.

The obtained set of hard-to-detect faults is a super set of the set of faults  $F_{ud}$ . This

is due to the fact that the number of patterns applied in multiple-polynomial scheme of P-PET is larger than a million, the number of random patterns we applied for the fault simulation.

Figure 4.1: Fault simulation

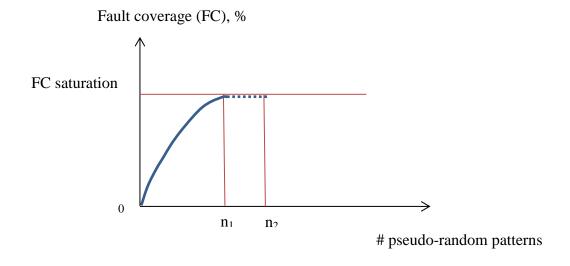

The number of random patterns we applied in the fault simulation was a million. We will discuss now the relation between the number of random patterns applied and the fault coverage in pseudo-random testing.

Figure 4.2: Fault coverage of pseudo-random testing

In Figure 4.2 the dependency of the fault coverage from the number of pseudorandom patterns applied in pseudorandom testing is shown [40]. The fault coverage rises in logarithmic manner towards the saturation.

According to Figure 4.2, in the beginning the slope of the curve is quite steep till it reaches its saturation. So, the fault coverage is growing rapidly until it saturates [40]. Hence, it does not matter how many patterns to apply  $n_1$  or  $n_2$  when we are close to the saturation of the fault coverage.

The fault simulation was performed for industrial circuits of different sizes. The results of the fault simulation and discussions are presented in chapter 6. The percentage of hard-to-detect faults from the faults of the set F lies in the range from 0.6% to 50%.

# 4.2 Generation of deterministic test patterns for hard-to-detect faults

Having obtained the list of hard-to-detect faults, we aim now at encoding these faults into test patterns with minimized number of care bits. The requirement of minimized number of care bits is very essential. The patterns generated for hard-to-detect faults will be used further in the process of selection of characteristic polynomials. And the less number of care bits the pattern has, the greater the probability for the polynomial to cover the pattern.

We will consider several methods for the test pattern generation: ATPG with minimum number of care bits and commercial ATPG.

#### 4.2.1 ATPG with minimum number of care bits

The process of the test pattern generation with minimum number of care bits will be based on satisfiability (SAT) problem. To start off with, we will introduce basic definitions about SAT taken from [45].

A **Boolean formula** is a logic expression defined over variables that take value "True" or "False" which are identified with "0" or "1".

A **truth assignment** to a set *V* of Boolean variables is a map  $\sigma: V \to \{0,1\}$ .

A satisfying assignment for F is a truth assignment  $\sigma$  such that F evaluates to 1 under  $\sigma$ .

**Conjunctive normal form** (CNF) of propositional formulas F is a conjunction (AND,  $\land$ ) of clauses, where each clause is a disjunction (OR,  $\lor$ ) of literals, and each literal is

either a variable or its negation (NOT,  $\neg$ ).

$$F = (a \vee \neg b) \wedge (\neg a \vee c \vee d) \tag{4.1}$$

Expression (4.1) shows the example of CNF. There CNF formula with four variables and two clauses is presented.

The Boolean SAT problem can be formulated as follows: given a CNF formula F, does F have a satisfying assignment? And often the problem includes finding of an actual satisfiability assignment.

We will consider first SAT-based two-valued ATPG. SAT formulas are based on two values: "0" and "1". In Figure 4.3 AND-gate with two inputs (a and b) and one output (s) is depicted. The SAT clause in CNF for this AND-gate is represented by (4.2). Indeed, for all possible assignments of a, b, s from the truth table (Table 4.1) f evaluates to 'True'.

Figure 4.3: AND-gate for 2-valued logic

$$f = (a+\neg s)(b+\neg s)(\neg a+\neg b+s) \tag{4.2}$$

| а | b | S |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 1 | 1 |

| 1 | 0 | 0 |

Table 4.1: Truth table for AND-gate

Using SAT-based two-valued ATPG we will be able to generate patterns only with two values "0" and "1". Whenever there is a freedom of assignment the value to the literal, the default value of "0" or "1" will be assigned. Since we aim at the least possible number of care bits in the pattern, we need to have patterns with a lot of don't care bits "X". Therefore, three-valued logic, "0", "1" and "X", is needed instead of two-valued logic.

For each of the primitive gates, the new SAT clauses were generated based on three-valued logic. To extend the logic, it was assumed that 'X' is represented by '00',

'0'- by '01', '1'- by '11', and the last combination is forbidden. To get the clauses, the truth table for each primitive gate was composed.

Figure 4.4: AND-gate for 3-value logic

Consider an AND-gate in Figure 4.4 with two inputs  $a_1a_2$  and  $b_1b_2$  and one output  $s_1s_2$ . The corresponding truth table is presented in Table 4.2.

| $a_1a_2$ | $b_1b_2$ | $s_1s_2$ |

|----------|----------|----------|

| 00 ('X') | 00 ('X') | 00 ('X') |

| 10 ('0') | 00 ('X') | 10 ('0') |

| 00 ('X') | 10 ('0') | 10 ('0') |

| 10 ('0') | 11 ('1') | 10 ('0') |

| 11 ('1') | 10 ('0') | 10 ('0') |

| 10 ('0') | 10 ('0') | 10 ('0') |

| 11 ('1') | 11 ('1') | 11 ('1') |

| 11 ('1') | 00 ('X') | 00 ('X') |

| 00 ('X') | 11 ('1') | 00 ('X') |

Table 4.2: Truth table for AND-gate for 3-value logic

Then a tool for Boolean logic optimization, analysis and synthesis is used to generate the SAT clauses for all primitive gates with subsequent minimization of the number of the clauses in conjunctive normal form. For the AND-gate the expression (4.3) is obtained.

$$(a_{2}+\neg s_{2})(b_{2}+\neg s_{2})(\neg a_{2}+\neg b_{2}+s_{2})(a_{1}+\neg b_{2}+\neg s_{1})(b_{1}+\neg b_{2})(a_{1}+\neg a_{2})(\neg a_{2}+b_{1}+\neg s_{1})$$

$$(a_{1}+b_{1}+\neg s_{1})(\neg a_{1}+a_{2}+s_{1})(\neg b_{1}+b_{2}+s_{1})(s_{1}+\neg s_{2})$$

$$(4.3)$$

The SAT-based ATPG process starts with computing of SAT clause in CNF for the whole circuit. This SAT-clause is composed of the SAT clauses for all gates in the circuit. After obtaining the SAT-based representation of the circuit, the fault is injected, and fault propagation paths are determined. Then a fault cone, the set of gates affected by fault, is copied. Then the outputs of fault-free cone z and copied faulty cone  $z_f$  are compared for the different inputs assignments. If  $z \oplus z_f = 1$ , or in other words, the compared outputs have different values, then the pattern tests the fault. General ATPG process was described in the subsection 2.1 of chapter 2 in more details.

SAT-based ATPG results in a set of patterns with minimum number of care bits. This is due to minimization algorithm applied in the process of pattern generation. The idea of finding the patterns with minimum number of care bits is based on the bisection search. This algorithm tries to decrease the number of care bits in the pattern till it is possible, and the valid pattern detecting the particular fault is found.

The relation between the circuit size and the SAT representation of the circuit is linear. So, the more gates are in the circuit, the more clauses are in the SAT representation of the circuit. However, the runtime of SAT-based ATPG is not linear. In this subsection we have introduced two- and three-valued ATPGs. For two-valued ATPG for AND-gate, three clauses are needed; in contrast, the three-valued ATPG has eleven clauses for AND-gate representation. Hence, three-valued SAT-based ATPG requires longer computational time and for some circuits it is infeasible.

The decision was made to use commercial ATPG in order to generate test patterns for larger circuits. Commercial ATPG does not require much time. On the other hand, it should be noted that commercial ATPG is a black box tool, so we are not aware of the internal structure and solving methods.

#### 4.2.2 Commercial ATPG

To start off with, we decided to generate test patterns for the whole list of hard-to-detect faults. We aimed at minimization of the number of care bits by introducing "X" values in ATPG process. The commercial tool was very fast in the process of pattern generation. The results are presented in chapter 6.

One of the basic features of commercial ATPG tools is a good compression mechanism. And this is clear since one usually wants to have the smallest set of test patterns generated to save memory. We presume that the commercial tool tends to compress the patterns internally, so it would take advantage of some "don't care" bits in the case of giving the whole list of faults. Since we aim at the least possible number of care bits, the decision was made to use commercial tool for generation of the patterns for each fault in a fault list, so that commercial tool would not have the possibility to merge the patterns.

This can be achieved by adding one fault at a time from the fault list, running ATPG, saving the current pattern and deleting the fault. This approach is depicted in Figure 4.5. The results are also presented in chapter 6.

Trying to contrast the results obtained by commercial ATPG and SAT-based ATPG, we can take a look at Figure 4.6 and Figure 4.7. The comparison can be made by scrutinizing the number of care bits in the pattern obtained for a particular fault in a fault list.

In Figure 4.6 and Figure 4.7, histograms for the circuit p45k and p100k are

depicted. Only the part of the fault list and corresponding patterns are shown. If there was no pattern generated for a particular fault, then there is a blank bar. On the x-axis we have the index of a fault in a fault list, and on the y-axis we have the number of care bits corresponding to the pattern which tests the particular fault designated by an index.

Figure 4.5: Process of generating patterns with commercial ATPG

Figure 4.6: Commercial vs. SAT-based ATPG for p45k

For the circuit p45k, SAT-based TPG has generated patterns with less number of care bits. Most of the times the difference in the number of care bits is one. Only in several cases this difference is five or fifteen bits. For the circuit p100k there is the same

number of care bits for both TPGs, but sometimes commercial ATPG generated patterns with more care bits.

Figure 4.7: Commercial vs. SAT-based ATPG for p100k

Judging by previously shown figures, we conclude that SAT-based ATPG generates patterns with less number of care bits, but it is not applicable to the large circuits. In the next chapter, we are considering the set covering heuristics for choosing polynomials for P-PET taking into account obtained pattern lists.

## **CHAPTER** 5

#### SET COVERING HEURISTICS

#### Contents

| 5.1 Shifting of the cones and removing redundant cones           | 39 |

|------------------------------------------------------------------|----|

| 5.2 Iterative polynomial selection                               | 39 |

| 5.2.1 General algorithm                                          | 40 |

| 5.2.1.1 Essential cone handling                                  | 42 |

| 5.2.1.2 Realization with minimal number of polynomials           | 43 |

| 5.2.1.3 Realization with more than minimal number of polynomials | 43 |

| 5.3 User-defined introduction of extra polynomial                | 45 |

| 5.4. Summary of the algorithm for polynomial selection           | 46 |

|                                                                  |    |

In this chapter we will concentrate on the algorithm for the selection of feedback polynomials for the test pattern generation of P-PET. In the beginning of the chapter, we will refresh the task formulation and provide the steps required to solve the problem. Then each step will be considered in details.

Let  $P_{MAX}$  be the set of primitive polynomials up to degree MAX, and  $K_{MAX}$  be the set of cones up to the size MAX. Let  $K_p = \{k \in K_{MAX}, p < k\}$  be the subset of  $K_{MAX}$ tested by polynomial p. We also have the pattern list pl containing the patterns with minimized number of care bits. The goal for us is formulated as follows: we aim to find the set of primitive polynomials  $P_s \subset P_{MAX}$  such that  $K_{MAX} = \bigcup_{p \in P_s} K_p$ , and the maximized number of covered patterns from pl. In other words, we want to encode maximized number of patterns from pl into characteristic polynomials which are used for P-PET pattern generation. This goal is subdivided into two sub-goals depending on the requirements. In the first sub-goal, we aim to have the minimum number of polynomials necessary to cover all the cones up to the size MAX. This formulation comes from the fact that additional polynomials will cause the test time to rise, and that polynomials need also to be stored on a chip. In this case, the degree of freedom of polynomials choice is exploited to select polynomials which are covering maximized number of patterns. In the second sub-goal, we aim to cover maximized number of patterns, and it is allowed to add extra polynomials. So, in the second stage, the resulting fault coverage is more important.

The procedure of selecting of the primitive polynomials is divided into three steps:

- 1. Shifting of the cones to the beginning of the scan chain

- 2. Reduction of the set  $K_{MAX}$  by removing redundant cones

- 3. Iterative selection of polynomials implemented as a set covering heuristics

The first two steps are preparatory. Then in the third step, set covering heuristics is developed in order to solve the problem efficiently.

# 5.1 Shifting of the cones and removing redundant cones

LFSR with the characteristic polynomial  $P(x) = \sum_{i=0}^{n} a_i * x^i$  generates the bit sequence c which can be calculated by (5.1) [9].

$$y_{m+n} = a_0 y_m + a_1 y_{m+1} + \dots + a_{n-1} y_{m+n-1}, \ m \ge 0$$

(5.1)

For each subsequence  $c=c_0$ , c,...,  $c_{n-1}$ , there is a sequence  $c'=c_{n-1}$ ,  $c_0$ ,...,  $c_{n-2}$  where c' is a cyclic shift of c. This means that the position of the cone is unimportant if the relative distances between the cone's inputs are not changed. Consequently, we shift all the cones to the beginning of the scan chain, while keeping the relative distance between their inputs [9].

A cone is considered as **redundant** if all input positions of the cone are contained in other cone. Therefore, we remove all redundant cones.

For example, suppose  $K_{MAX}$  contains two cones:  $k_1 = \{3, 5, 10\}$  and  $k_2 = \{2, 4, 9, 14\}$ . Firstly, we shift these cones to the beginning of the scan chain. After shifting, we will get:  $k_1 = \{0, 2, 7\}$  and  $k_2 = \{0, 2, 7, 10\}$ . Cone  $k_2$  contains  $k_1$ , or  $k_1 \subset k_2$ . So,  $k_1$  is redundant cone, and we remove it from  $K_{MAX}$ .

# 5.2 Iterative polynomial selection

In the first sub-goal formulated earlier in this chapter, we aim to maintain the minimum number of polynomials in the final set  $P_s$  necessary to cover all the cones up to the size MAX. So, the test time is not increased by addition of extra polynomials. In this task, we use the degree of freedom when selecting polynomials. For example, several polynomials cover the same number of cones from the set  $K_{MAX}$ . Then the polynomial which covers the maximum number of care bits is selected.

In the second sub-goal, we are more interested to have further maximized number of the patterns covered by selected polynomials. And we are allowed to increase the number of polynomials in the final set  $P_s$ .

In order to control the number of polynomials in the set  $P_s$  and the resulting number of patterns covered, we will use a cost function which will assign priorities to

the cones and to the patterns. These priorities will be taken into account in the process of polynomials selection.

We will start this subsection with consideration of the general algorithm proposed for the process of polynomial selection. Then we will concentrate on the application of the algorithm for solving both sub-goals. Further the user-defined extension of the algorithm will be provided. And we will conclude this chapter with a summary.

#### 5.2.1 General algorithm

The algorithm proposed is used for achieving both sub-goals. It is flexible since it is configured by means of the coefficients of the cost function. The cost function influences the polynomial selection by considering cones and patterns. To accomplish the first sub-goal, the cost function will give the whole priority to the cones. To reach the second sub-goal, different priorities will be assigned to the cones and to the patterns depending on the user requirements.

Assume that all cones of the circuit are shifted to the beginning of the scan chain, and all redundant cones are removed. So, we have the set of the cones *K* of the circuit.

The algorithm for polynomial selection is presented in Figure 5.1. The first step is to form the set of the cones  $K_{MAX}$  (5.2) consisting of the cones from the set K with the size up to MAX.

$$K_{MAX} = \{k \in K \mid |k| \le MAX\} \tag{5.2}$$