# In-Field Structural Methods for End-to-End Automotive Digital Diagnosis

Von der Fakultät für Informatik, Elektrotechnik und Informationstechnik der Universität Stuttgart zur Erlangung der Würde eines Doktors der Naturwissenschaften (Dr. rer. nat.) genehmigte Abhandlung

Vorgelegt von

#### Alejandro Cook

aus Barquisimeto / Venezuela

Hauptberichter: Prof. Dr. rer. nat. H.-J. Wunderlich

Mitberichter: Prof. Dr.-Ing. Jürgen Teich

Tag der mündlichen Prüfung: 16.07.2014

Institut fur Technische Informatik der Universittät Stuttgart

to my wife Luisa to my parents

# **Acknowledgments**

Many people have contributed in several ways to the successful conclusion of this work. I am glad to have the opportunity to thank those without whose support and encouragement this dissertation would not have been possible.

I thank Ulrich Abelein for his continuous support throughout project DIANA. I thank Prof. Hans-Joachim Wunderlich for the opportunity to work at his department, and for all the constructive feedback he provided me during this dissertation. My appreciation also goes to Rafał Baranowski, to my dad, and to my brother for proofreading this manuscript.

I am thankful to my colleagues at the University of Stuttgart with whom I had the pleasure to work for the last 5 years. A big thanks goes to the DIANA team: Dominik Ull, Laura Rodríguez Gómez, Melanie Elm and Stefan Holst. I am also very grateful to Rafał Baranowski, Claus Braun, Atefe Dalirsani, Nadereh Hatami, Michael Imhof, Anusha Kakarala, Michael Kochte, Chang Liu, Abdullah Mumtaz, Eric Schneider, and Alexander Schöll, for many insightful discussions. I owe a debt of gratitude to Mirjam Breitling, Helmut Häfner, and Lothar Hellmeier for their outstanding organizational and technical expertise.

To my wife Luisa Aristizábal I am more grateful than these lines could describe. Her love, patience, and encouragement have been the source of my energy during our adventures in Germany. I thank my parents for their unconditional support in all my endeavors, no matter how big or how small. I also thank my brother, who, as the perfectionist that he is, triggered my overachieving instincts at an early age.

Last but not least, I thank my dear friends Rubén Cervantes, Diana García and Cary Brown for all the laughs we once shared in Stuttgart.

Stuttgart, June 2014

Alejandro Cook

# **Summary**

The automotive domain has strongly relied on recent advances in semiconductor technology in order to offer customers a huge amount of appealing features of overwhelming complexity. As traditional functional tests are no longer sufficient to fulfill automotive diagnostic requirements, the analysis of automotive semiconductor failures has become a major quality concern. Semiconductor structural test solutions are already key technologies for the successful manufacturing of any integrated circuit. However, these techniques place stringent constraints on the test application process, which cannot be easily enforced outside the manufacturing environment to achieve a suitable automotive diagnostic solution.

This dissertation captures the requirements of a suitable automotive structural diagnostic approach for random digital circuits and provides cost-efficient solutions for the corresponding technical challenges. For this purpose, state-of-the-art methodologies for manufacturing test are enhanced in order to support the failure analysis process in the automotive domain throughout the complete system life-cycle.

The first contribution of this work is a conceptual architecture for the reuse of available on-chip test infrastructure necessary to conduct autonomous structural tests at system level. The presented methodology makes use of any available system resources in order to gain access to the same on-chip *design-for-test* structures originally devised to improve the effectiveness and efficiency of manufacturing tests.

The second contribution is a logic diagnostic procedure that analyzes highly compacted structural test responses and yet achieves excellent diagnostic accuracy. The presented algorithm is able to diagnose single and multiple arbitrary faults without the need for exhaustive simulation. Experimental results show the developed technique outperforms diagnostic solutions in the literature both in terms of accuracy and test response compaction ratio.

Finally, a cost-efficient on-chip diagnostic architecture is presented, which enables the autonomous collection of compacted test responses during built-in self-test (BIST). This architecture is fully compatible with traditional BIST procedures typically used for manufacturing test. Therefore, the proposed architecture may be used in combination with any technique for cost-effective autonomous on-chip test pattern generation. Thus, it efficiently provides accurate diagnostic capabilities while retaining the same

defect coverage in the generated pattern sequence.

The methods and algorithms in this dissertation enable the introduction of structural test and diagnostic solutions into the failure analysis process of the automotive industry. Experimental results show the performance of the presented methodology is comparable to that of state-of-the-art solutions employed for semiconductor manufacturing.

# Zusammenfassung

Die Fahrzeugtechnik nutzt die aktuellen Entwicklungen der Halbleiterindustrie, um Kunden eine enorme Anzahl ansprechender, komplexer Produkteigenschaften zu bieten. Da traditionelle, funktionale Testverfahren nicht mehr ausreichen, um den diagnostischen Anforderungen im Automobilbereich gerecht zu werden, wird die Analyse von Halbleiterdefekten zu einem wichtigen Anspekt der Qualitätssicherung. Strukturelle Testverfahren stellen bereits eine Schlüsseltechnologie für die erfolgreiche Herstellung integrierter Schaltungen dar. Da dieses Vorgehen jedoch strenge Vorgaben bezüglich der Testanwendung mit sich bringt, kann es nicht problemlos außerhalb der Chipherstellung zum Erreichen einer angemessenen diagnostischen Lösung im Automobilbereich eingesetzt werden.

Diese Dissertation beschreibt die Anforderungen eines geeigneten strukturellen Ansatzes für die Diagnose jeglicher digitaler Schaltungen, und bietet kostengünstige Lösungen für dazugehörige technischen Herausforderungen. Zu diesem Zweck werden herkömmliche Testmethoden aus dem Bereich der Herstellung derart angepasst, dass sie die Fehleranalyse über den gesamten Lebenszyklus des Systems unterstützen.

Der erste Beitrag dieser Arbeit ist ein Ansatz, der die verfügbaren Hardwareressourcen im System wiederverwendet, um die autonome Durchführung struktureller Tests zu ermöglichen. Die vorgestellte Testarchitektur greift hierzu auf existierende Test- und Diagnoseinfrastruktur des Chips zu, welche ursprünglich zur Verbesserung des Herstellungstests konzipiert wurde.

Der zweite Beitrag ist ein Verfahren zur Logik-Diagnose, welches trotz stark kompaktierter Testantworten dennoch eine hervorragende diagnostische Auflösung erreicht. Das vorgestellte Algorithmus ist in der Lage, sowohl Einzel- als auch Mehrfachfehler ohne vollständige Fehlersimulation zu diagnostizieren. Experimentelle Ergebnisse zeigen, dass die entwickelte Methode frühere Diagnosemethoden aus der Literatur bezüglich Genauigkeit und Kompaktierung von Testantworten übertrifft.

Schließlich wird eine kostengünstige Diagnosearchitektur vorgestellt, welche das autonome Sammeln kompaktierter Testantworten bei der Durchführung eingebauter Selbstests (Built-in Self-Test, BIST) ermöglicht. Diese Architektur ist vollständig kompatibel zu traditionellen Selbstestverfahren, wie sie typischerweise beim Herstellungstest eingesetzt werden. Der vorgeschlagene Ansatz kann mit jeder Methode zur kosten-

effektiven, autonomen On-Chip-Erzeugung von Testmustern kombiniert werden. So ermöglicht diese Methode hochgenaue diagnostische Fähigkeiten, während die Defektabdeckung der erzeugten Testmustersequenz erhalten bleibt.

Die Methoden und Algorithmen in dieser Dissertation ermöglichen die Einführung struktureller Test- und Diagnoseverfahren bei der Fehleranalyse im Bereich der Fahrzeugtechnik. Experimentelle Ergebnisse belegen, dass die Leistungsfähigkeit der vorgestellten Methoden mit in der Chipherstellung eingesetzten Verfahren vergleichbar ist.

# **Contents**

| Sı | umma  | ry                                                        | 7  |

|----|-------|-----------------------------------------------------------|----|

| Zι | ısamı | menfassung                                                | g  |

| 1  | Intro | oduction                                                  | 15 |

|    | 1.1   | Challenges in Automotive Semiconductor Test and Diagnosis | 16 |

|    | 1.2   | Semiconductor Failures in the Automotive Domain           | 18 |

|    |       | 1.2.1 Hazard Rate                                         | 20 |

|    | 1.3   | Failure Analysis in the Automotive Domain                 | 21 |

|    | 1.4   | Diagnostic Use-Cases                                      | 24 |

|    |       | 1.4.1 Workshop Test                                       | 24 |

|    |       | 1.4.2 Semiconductor Failure Analysis                      | 25 |

|    |       | 1.4.3 Power-Up/Down Test                                  | 25 |

|    |       | 1.4.4 Online Test                                         | 26 |

|    | 1.5   | Organization and Contributions                            | 27 |

| 2  | Stru  | ctural Test and Diagnosis                                 | 29 |

|    | 2.1   | Defects and Faults                                        | 29 |

|    | 2.2   | Fault Modeling                                            | 30 |

|    | 2.3   | Scan Design                                               | 31 |

|    | 2.4   | Access to On-Chip Test Infrastructure                     | 32 |

|    |       | 2.4.1 IEEE 1149.1 Standard                                | 33 |

|    |       | 2.4.2 IEEE P1687                                          | 34 |

|    |       | 2.4.3 IEEE 1500 Standard                                  | 35 |

|    | 2.5   | Logic Built-In Self-Test                                  | 35 |

|    |       | 2.5.1 Test Pattern Generation                             | 37 |

|    |       | 2.5.2 Test Response Compaction                            | 41 |

## Contents

|   | 2.6   | 6 Logic Diagnosis                       |                                                                   |    |  |

|---|-------|-----------------------------------------|-------------------------------------------------------------------|----|--|

|   |       | 2.6.1                                   | Inject-and-Validate                                               | 45 |  |

|   |       | 2.6.2                                   | Back-Tracing                                                      | 46 |  |

|   | 2.7   | Summ                                    | ary and Outlook                                                   | 47 |  |

| 3 | State | e-Of-Th                                 | e-Art in In-Field Test and Diagnosis                              | 49 |  |

|   | 3.1   | Systen                                  | n-Level Functional Diagnosis                                      | 50 |  |

|   | 3.2   | Systen                                  | n-Level Structural Diagnosis                                      | 51 |  |

|   |       | 3.2.1                                   | Software-Based Self-Test (SBST)                                   | 51 |  |

|   |       | 3.2.2                                   | In-System Structural Tests                                        | 52 |  |

|   | 3.3   | Logic I                                 | Diagnosis for BIST                                                | 54 |  |

|   |       | 3.3.1                                   | Indirect Diagnosis                                                | 55 |  |

|   |       | 3.3.2                                   | Direct Diagnosis                                                  | 57 |  |

|   | 3.4   | Summ                                    | ary and Outlook                                                   | 59 |  |

| 4 | Effic | ient Ac                                 | cess to On-Chip Test Infrastructure                               | 61 |  |

|   | 4.1   | Non-Ir                                  | ntrusive Automotive Structural Test                               | 61 |  |

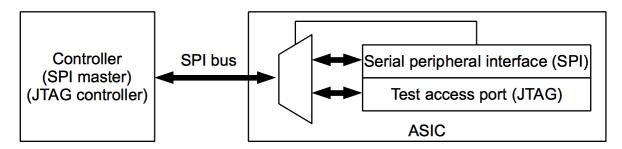

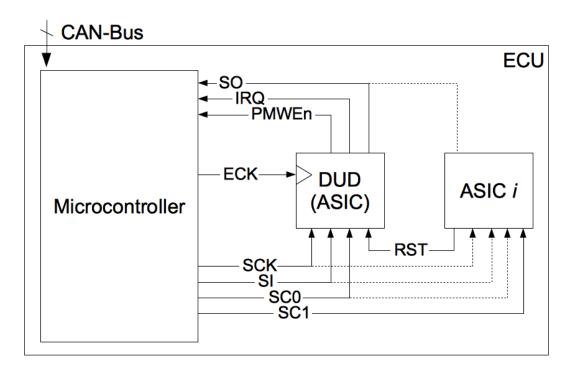

|   |       | 4.1.1                                   | Test Access                                                       | 62 |  |

|   |       | 4.1.2                                   | Test Application Process                                          | 62 |  |

|   | 4.2   | Case S                                  | tudy: Workshop Test                                               | 64 |  |

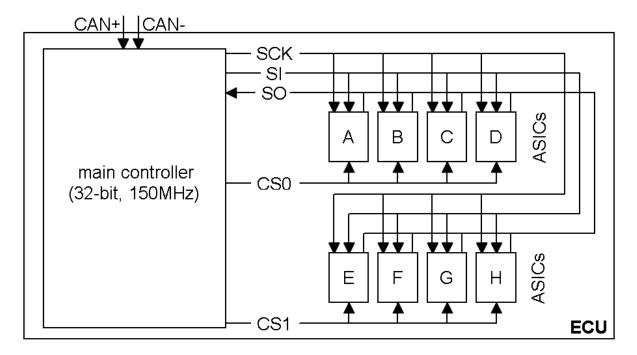

|   |       | 4.2.1                                   | ECU Architecture                                                  | 65 |  |

|   |       | 4.2.2                                   | Manufacturing Scan-Test                                           | 66 |  |

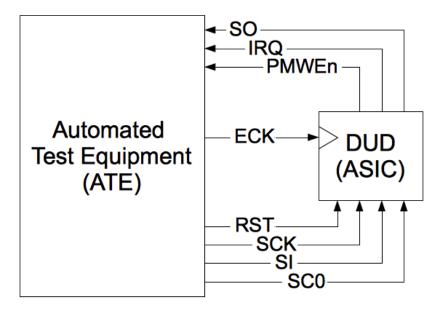

|   |       | 4.2.3                                   | Implementation Setup                                              | 67 |  |

|   |       | 4.2.4                                   | Test Application Process                                          | 67 |  |

|   |       | 4.2.5                                   | Results                                                           | 69 |  |

|   | 4.3   | Summ                                    | ary and Outlook                                                   | 69 |  |

| 5 | Logi  | ic Diagr                                | nosis with Compacted Test Responses                               | 71 |  |

|   | 5.1   | Logic I                                 | Diagnosis and Failure Analysis                                    | 71 |  |

|   | 5.2   | Direct                                  | Diagnosis of Arbitrary Faults with Test Signatures                | 73 |  |

|   | 5.3   | 5.3 Generation of Fault Candidate Lists |                                                                   |    |  |

|   | 5.4   | Logic I                                 | Diagnosis for Stringent Storage and Tester Bandwidth Requirements | 76 |  |

|   |       | 5.4.1                                   | Diagnosis with Intermediate Signatures                            | 76 |  |

|   | 5.5   | Logic I                                 | Diagnosis for Increased Defect Density                            | 82 |  |

|   |       | 5.5.1                                   | The Disturbance Function for Fault Pairs                          | 82 |  |

|   |       | 5.5.2                                   | Direct Diagnosis of Multiple Faults                               | 84 |  |

|    |       | 5.5.3   | Explaining Non-SLAT Signatures                  | . 85  |

|----|-------|---------|-------------------------------------------------|-------|

|    |       | 5.5.4   | Diagnostic Procedure                            | . 88  |

|    |       | 5.5.5   | Aliasing Probability                            | . 94  |

|    | 5.6   | Auton   | notive Use-Case: Semiconductor Failure Analysis | . 95  |

|    | 5.7   | Summ    | nary and Outlook                                | . 96  |

| 6  | Test  | Archite | ecture for Built-In Diagnosis                   | 99    |

|    | 6.1   | Gener   | ic Diagnostic Architecture                      | . 99  |

|    | 6.2   | Efficie | ent Storage of Response Data                    | . 101 |

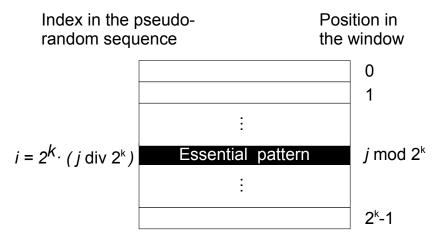

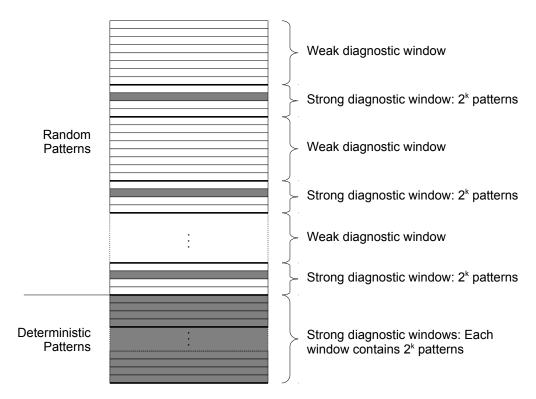

|    | 6.3   | Diagn   | ostic Architecture for Mixed-Mode BIST          | . 103 |

|    |       | 6.3.1   | Test Generation                                 | . 103 |

|    |       | 6.3.2   | Partitioning                                    | . 104 |

|    |       | 6.3.3   | Diagnosis                                       | . 106 |

|    | 6.4   | Auton   | notive Use-Case: Power-Up/Down Test             | . 107 |

|    |       | 6.4.1   | BIST Application under Functional Constraints   | . 108 |

|    | 6.5   | Summ    | nary and Outlook                                | . 110 |

| 7  | Res   | ults    |                                                 | 113   |

|    | 7.1   | Diagn   | ostic Setup                                     | . 113 |

|    |       | 7.1.1   | Benchmark Circuits                              | . 114 |

|    | 7.2   | Logic 1 | Diagnosis with Compacted Test Responses         | . 115 |

|    |       | 7.2.1   | Single Faults                                   | . 115 |

|    |       | 7.2.2   | Multiple Faults                                 | . 119 |

|    | 7.3   | Test A  | rchitecture for Built-In Diagnosis              | . 127 |

|    | 7.4   | Hardw   | vare Costs                                      | . 128 |

|    |       |         | Diagnostic Accuracy                             |       |

|    | 7.5   | Summ    | nary and Outlook                                | . 133 |

| 8  | Con   | clusion | ns and Future Work                              | 135   |

|    | 8.1   | Furthe  | er Challenges in the Automotive Domain          | . 137 |

|    | 8.2   | Furthe  | er Research Opportunities                       | . 138 |

| Bi | bliog | raphy   |                                                 | 139   |

| Α  | Add   | itional | Result Tables                                   | 161   |

|    | A.1   | Diagn   | osis of Single Faults                           | . 161 |

|    | A.2   | Diagno  | osis of Multiple Faults                         | . 162 |

## Contents

| A.3                        | Built-In Diagnosis       | . 169 |

|----------------------------|--------------------------|-------|

| Glossaı                    | ry                       | 173   |

| Index                      |                          | 176   |

| Publications of the Author |                          |       |

| Curricu                    | llum Vitae of the Author | 181   |

Automotive systems nowadays feature increasingly complex electric and electronic components. This trend is in strong contrast with the traditional perspective, where automotive vehicles are categorized, for the most part, as mechanical systems [Furst10]. Such a dramatic shift has driven the role of semiconductors into the spotlight of the automotive industry. In fact, most of the industry's innovations in the last decade have been enabled, either directly or indirectly, by the use of semiconductors [Abelein12]. Today a premium vehicle contains over 100 distributed electronic control units (ECUs) [Kim11] and, as semiconductor technology provides higher integration levels, even today's most demanding features will become common practice in later vehicle generations.

As semiconductors play a central role in the automotive industry, especially for the processing of digital information, very tight quality standards are usually enforced during chip manufacturing. However, the integrity of an automotive system can still be affected by subtle issues, which are not detected during manufacturing tests (test escapes), latent hardware faults which become active after system assembly, harsh environmental conditions, or degradation [Chen13, Sun13].

The automotive industry traditionally relies on *functional tests* to detect any hardware issue in the field. This kind of tests verifies the integrity of the system by comparing the system's behavior to its specification. This is achieved, for example, by means of concurrent test routines and power-up tests that evaluate functional system properties, like plausibility checks or field bus interconnection checks. Unfortunately, these techniques may not suffice to account for complex semiconductor failure behavior, since they do not fully cover the complete system functionality and only verify a few corner-cases in the specification.

For instance, in a distributed automotive subsystem, consisting of several interacting ECUs, functional tests may help to disclose many system malfunctions. However, their

structural fault coverage is hard to measure, and usually amounts roughly to 50% [Maxwell00]. As a consequence, automotive semiconductor failure analysis is today a very elaborate and time-consuming process.

Structural tests identify faulty components in a device according to its internal building blocks and their interconnection. For example, they may check for unintended connections or *bridges* between neighboring signals in the circuit layout. In contrast to functional tests, which can only provide a pass/fail test outcome, structural tests offer the opportunity to distinguish fault locations. These diagnostic capabilities can complement traditional functional testing in order to meet the high quality demands of the automotive domain.

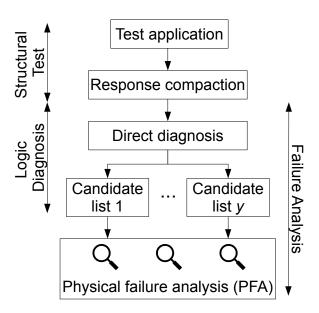

This dissertation presents structural techniques for the diagnosis of complex embedded systems, like those typically found in the automotive industry. These methods enable the application of structural tests in an assembled system and analyze the obtained failure response data to locate faulty semiconductor components. The presented methodology assists semiconductor failure analysis activities for continuous improvement of system quality, which, for the automotive domain, range from workshop tests, where the lowest replaceable unit is identified, to detailed semiconductor analysis, where diagnostic results direct physical failure analysis (PFA) to the most likely locations in the chip responsible for the observed erroneous behavior.

This chapter will first describe the challenges of a suitable structural diagnostic strategy. Then, semiconductor failures are analyzed in the context of automotive systems. After this, the benefits of structural test in the automotive failure analysis flow are detailed. In the following section, typical application scenarios, so-called diagnostic use-cases, are presented, which reflect elicited industrial requirements. Finally, this chapter provides a short overview of the rest of this dissertation.

# 1.1. Challenges in Automotive Semiconductor Test and Diagnosis

The goal of structural diagnostic approach for semiconductors is to enable the adoption of corrective measures that improve overall system quality and reduce service and repair costs in case of semiconductor failures. For this purpose structural test

and diagnosis are required throughout the complete system life-cycle. Structural tests capture relevant information about the hardware integrity of a device, while structural diagnosis carries out the corresponding analysis in order to identify one or more faulty hardware components. Although semiconductor test and diagnosis are already mature, indispensable disciplines for the successful realization of any semiconductor device, available structural test and diagnostic methods need to be extended in order to account for the following domain properties.

Firstly, the capabilities of a structural test and diagnostic solution strongly depend on the resources available to collect structural information from a system component under test. Thus, the semiconductor test application process needs to support the characteristics of the testing environment, which defines the availability of test equipment, its usability, and the amount of time that can be devoted to test.

Secondly, diagnostic results need to support a wide range of diagnostic objectives. In this regard, the identification of a faulty component at the right granularity level is one key aspect to enable efficient corrective and preventive quality measures. For example, in some situations it may be sufficient to identify a faulty board, while in others it may be required to distinguish faulty chip locations in an integrated circuit (IC).

The resulting requirements can only be fulfilled if systems are equipped with structural self-test and diagnostic capabilities. Systems-on-chip (SOCs) commonly used to-day integrate lots of different specialized cores containing logic, memory, analog, and mixed-signal resources. This dissertation focuses on an efficient test/diagnostic solution for logic cores. In comparison to memory cores, logic cores do not have a regular structure, which makes their test and diagnostic procedures much more complex.

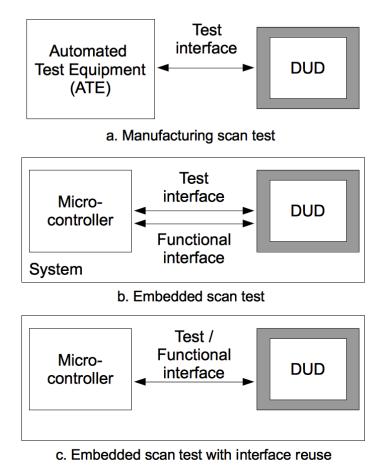

The main technical challenges for a suitable solution for structural diagnosis are: (1) the efficient access to on-chip test infrastructure, (2) the diagnosis of logic cores with highly compacted test responses and (3) the design of a cost-effective on-chip architecture for built-in diagnosis.

• Access to on-chip test infrastructure

ICs are equipped with design-for-test (DfT) infrastructure to improve the effectiveness and efficiency of manufacturing tests. These internal structures are driven and controlled by expensive automated test equipment (ATE) especially designed for the semiconductor industry. In order to gain access to DfT infrastructure for system diagnosis, efficient approaches are necessary to make use of

any available system functionality to manage the activation and application of structural tests.

- Diagnosis of logic cores with highly compacted test responses

The full diagnostic potential of structural diagnosis cannot be fully exploited with a simple pass/fail test criterion. For this reason, logic diagnosis is performed to analyze the collected response data of a faulty IC and locate and characterize the source of the erroneous behavior in the chip structure. Generally, the test response data gathered from the ATE suffice to accurately characterize arbitrary defect behavior [Holst12]. Unfortunately, the total amount of information in the response data of a single IC may surpass the available storage capacity of the entire system. Consequently, the compaction of test response data becomes mandatory and, therefore, logic diagnosis algorithms need to be extended accordingly so that they still provide enough insight into the problems affecting the manufacturing process.

- Design of a cost-efficient on-chip architecture for built-in diagnosis

The efficient on-chip generation of diagnostic data calls for a specialized test architecture to (a) generate suitable diagnostic stimuli and (b) compact and store obtained test responses. The hardware resources required for both test and diagnosis must be carefully optimized so that they make the least impact on the overall system cost.

Finally, safety and security play an important role for automotive systems. Safety requirements must be fulfilled in order to minimize the risk of passenger injury, while security guidelines need to be in place to prevent the tampering with the ECU, and protect sensitive information belonging to the companies involved in the failure analysis process. Safety and security considerations are out of the scope of this dissertation

### 1.2. Semiconductor Failures in the Automotive Domain

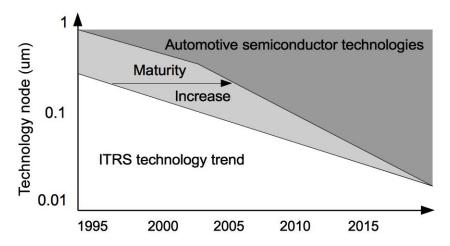

The introduction of semiconductors in passenger vehicles started already more than two decades ago. As Figure 1.1 shows, in those early days only mature semiconductor technologies found their way into automotive systems. As market trends demand a staggering number of features in current vehicle generations, today's automotive systems make use of the latest manufacturing technology, which, as described in the

International Technology Roadmap for Semiconductors (ITRS) [ITR11], is more likely to exhibit operational malfunctions.

Figure 1.1.: Automotive semiconductor technology trend [Abelein13]

Malfunctions in ICs are due to physical imperfections or *defects* in the semiconductor fabrication process. Semiconductor test and diagnosis identify, locate and characterize the root cause of failures in manufactured ICs in order to help analyze the production process and adopt suitable measures to improve quality and reduce costs. This process is called *yield learning* and is performed throughout the complete chip manufacturing cycle, i.e. from first silicon to volume production. Consequently, semiconductor test and diagnosis play a key role for the successful realization of any IC and amount to the largest part of total manufacturing costs.

The automotive market segment must, therefore, account for two conflicting goals: On the one hand, stringent quality requirements demand that almost no faulty ICs be shipped and integrated into a system. On the other hand, as the automotive industry is very sensitive to costs, the price of a chip must be kept sufficiently low. A suitable compromise in this situation is very hard to achieve and, as a result, some marginal integrated circuits, which are prone to malfunctions in the field, may be inadvertently shipped to customers. In the next subsections, the most common causes of such semi-conductor failures are summarized.

#### 1.2.1. Hazard Rate

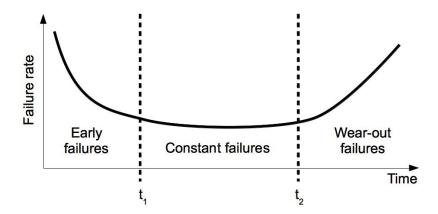

The hazard rate measures the rate at which a product is likely to fail over time. This rate has already been extensively studied in the context of reliability engineering [Yang07]. Figure 1.2 shows the typical course of failures in time (FIT) a product line suffers during its complete lifetime. The figure shows three distinct regions: For  $t < t_1$  a relatively large number of early failures are expected and their failure rate monotonically decreases. This is mostly caused by marginal devices, which cannot stand operationl stress. During  $t_1 < t < t_2$  the failure rate remains more or less constant, while for  $t > t_2$  the product suffers from wearout mechanisms and failure rate grows steadily.

Figure 1.2.: The "bathtub" curve function [Yang07]

In the case of ICs, the failure rate can be attributed either to *random* or *systematic* defects. Random defects are the result of spurious effects during manufacturing, which cannot be precisely modeled or quantified beforehand. In contrast, systematic defects can be influenced by tuning the fabrication process or by making changes in the device design. In this case, product quality [Williams81] can be improved by adjusting the manufacturing test procedure according to the observed failure mechanism. Therefore, a suitable end-to-end semiconductor test and diagnostic strategy spanning the whole system's lifecycle can provide valuable insight to optimize chip production.

Early life failures are usually due either to test escapes or latent defects. On the one hand, test escapes are defects for which no suitable manufacturing test was applied and no erroneous response was observed. On the other hand, latent defects only become active after some service time. Traditionally, these defects are identified in *burn-in* tests [McPherson06], where the chip is exercised under stress, like elevated

temperature, increased voltage, high humidity, etc., for a long period of time. Burn-in tests, however, are very expensive to conduct, and are not guaranteed to uncover all latent defects. In any case, manufacturing variations in deep sub-micron technologies pose additional challenges when identifying an optimal test strategy.

Wearout failures are due to transistor degradation effects a chip experiences after prolonged operation periods. Different wearout mechanisms, like electromigration, oxide wearout and breakdown, hot carrier injection (HCI) and negative bias temperature instability (NBTI) have received increased attention in the context of reliability analysis [Segura05].

# 1.3. Failure Analysis in the Automotive Domain

Traditionally, automotive failure analysis is conducted by means of functional tests performed at different stages during the lifetime of a vehicle. The diagnostic capabilities of such tests are limited, as they can only perform data measurements, conduct plausibility checks and, to some degree, verify the physical connections between ECU components. As the amount of semiconductor devices in the car increases, these tests are no longer sufficient to provide a reasonable estimation of the integrity of semiconductor devices.

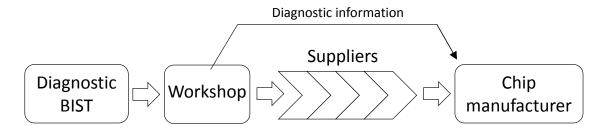

Functional tests are nowadays carried out in the field during the regular operation of a vehicle. If a problem is detected, a corresponding diagnostic trouble code [J19] is stored in the ECU memory and reported to the driver with a visual signal on the dashboard. The analysis of the reported failure begins at the workshop, where error information gathered during the operation of the system is collected. Then, the analysis and processing of this information takes place in different companies with different diagnostic strategies.

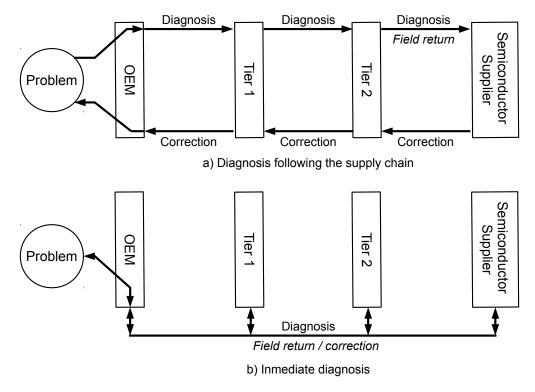

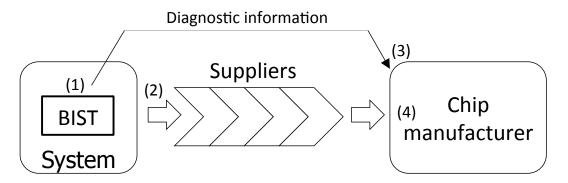

For repair purposes in the workshop, it is only necessary to identify the faulty ECU, which is replaced on the spot. The failure information is analyzed by the original equipment manufacturer (OEM) and the affected ECUs are sent to the first suppliers in the chain or *tier 1 suppliers*, who conduct another battery of tests in order to identify the root cause of the problem. As illustrated in Figure 1.3(a) this procedure may be repeated by several companies in the supply chain until, in case of a semiconductor failure, the problem is reported to the semiconductor provider. For subsequent analysis

at the logic level, the chip has to be removed from the ECU and tested in isolation.

Figure 1.3.: Automotive semiconductor diagnosis

This traditional semiconductor diagnostic flow has two main drawbacks: firstly, it requires a given supplier in the chain to wait for the diagnostic information from the previous supplier before performing its own diagnostic procedure. Secondly, for detailed semiconductor diagnosis a chip has to be removed from its enclosing system. The desoldering process exposes the ECU to heat and physical stress, which may render the IC useless for further examination. Additionally, even when a chip is successfully detached from its board, subsequent structural tests may not reveal the presence of a fault. This is known as the "no trouble found (NTF)" syndrome [Conroy05], which is due to the fact that test conditions at the chip manufacturer are different from those of the chip's operating environment in the ECU.

In the proposed diagnostic flow shown in Figure 1.3(b), ICs are equipped with DfT infrastructure, whose access mechanisms are made available to the OEM. This makes it possible to perform structural diagnosis early in the failure analysis flow and gather detailed diagnostic information from chips under operating conditions very similar to those they experience during regular operation.

Structural diagnosis is the process of identifying a faulty component in a vehicle. For a hardware component under diagnosis  $C_{ud}$ , a structural test set  $T = [t_1, t_2, \cdots, t_n]$  comprising n tests is applied, and the corresponding test responses  $C_{ud}(T) = [r_1, r_2, \cdots, r_m]$  are gathered from the vehicle. A structural model C of each hardware component describes its internal elements and their interconnections. The same test set C is applied to this component representation and fault-free responses C(T) are obtained. Structural diagnosis analyzes  $C_{ud}(T)$  and C(T) and identifies a faulty hardware element.

In some diagnostic situations it is sufficient to identify a defective ECU. As structural tests are performed separately for each ECU, a straight-forward comparison between the expected test responses C(T) and the observed responses  $C_{ud}(T)$  can already achieve this goal. However, for other use-cases, where the defect location in the chip has to be derived, a more detailed analysis of the structural differences between C and  $C_{ud}$  is mandatory to find the root cause of the observed erroneous behavior.

Structural diagnosis offers benefits for the OEM, the chip manufacturer as well as for suppliers in-between. Structural tests help OEMs assess the hardware integrity of the ICs in the vehicle. Such tests are generated according to a fault model and, therefore, OEMs can precisely quantify test effectiveness. This capability has already become a requirement in the prevailing automotive safety standard for passenger vehicles [ISOc, IEC].

The application of structural tests automatically enables component diagnosis at system and ECU level. That is, they unequivocally identify a single faulty chip so that its enclosing ECU can be replaced and further analyzed. Finally, and maybe most importantly, the gathered diagnostic information reduces the number of NTF cases, since the test application is more likely to capture the observed failure mechanism. Moreover, a systematic semiconductor problem can be more efficiently handled once the collected diagnostic information is delivered to the chip manufacturer, who analyzes any systematic yield problem and adopts any suitable countermeasures during chip fabrication and testing. In this way, the time and effort devoted to failure analysis in the traditional diagnostic approach is greatly shortened, the number of future faulty vehicles is drastically reduced, and product quality is improved.

Similarly, chip manufacturers can factor in the diagnostic data collected in the field and improve their existing diagnostic procedures. Such detailed structural diagnostic information of all faulty chips is extremely valuable as the chip manufacturer optimizes yield [Keim06, Blanton12].

Finally, all the suppliers benefit from the developed flow, since a faulty chip is uniquely identified, which again speeds up diagnostic activities by identifying hardware problems and distinguishing faulty chips as early as possible.

# 1.4. Diagnostic Use-Cases

The various requirements and constraints at each step of the automotive failure analysis process have been categorized into four diagnostic use-cases, namely, *semiconductor failure analysis*, *workshop test*, *power-up/down test*, *online test*. They reflect current industrial needs in terms of diagnostic resolution, test requirements and application time, available test equipment, and safety/security.

#### 1.4.1. Workshop Test

In workshop test it is most important to identify a faulty ECU to be replaced. The objective is to fix any malfunction as soon as possible so that vehicle operation is no longer compromised. As the performance of a workshop is directly visible to the end user, the effectiveness and efficiency of workshop tests play an important role for customer perception. For example, several visits to the workshop to correct the same problem can severely damage customer loyalty.

The application of structural tests, or the collection of structural test results stored in the vehicle during its operation, can greatly improve workshop performance. As structural tests can unequivocally identify a faulty hardware component, they can efficiently distinguish which ECUs need to be replaced to restore correct system operation. Furthermore, structural tests in the workshop can also reduce service and repair costs, as fault-free units are rarely discarded.

During workshop test there is no direct access to the pins of a hardware component, so tests have to be performed with the tools and interfaces commonly used in the automotive domain. Also, the test time per ECU has to be within the range of minutes. Since workshop test is usually performed by third-party companies, warranty and security limitations have to be enforced. This means that no sensitive information should be disclosed for the application of the test and the state of the ECU after the test has to comply with the corresponding warranty agreement.

#### 1.4.2. Semiconductor Failure Analysis

Semiconductor failure analysis is performed for all field returns after a faulty ECU is identified. This includes, but is not limited to, the faulty ECUs identified during workshop test. All field returns are analyzed further in order to establish the nature of the observed problem and to determine which company needs to conduct subsequent failure analysis.

As a consequence, this use-case spans a wide array of activities carried out by the OEM, as well as tier 1 and 2 suppliers, in order to better understand hardware issues and take appropriate preventive actions in the production of the next batch of vehicles. However, as the faulty ECU needs to go through several test procedures, an important constraint in this use-case is that no applied test should render the ECU unsuitable for additional testing. This implies, for example, that a faulty chip cannot be removed from its board to be tested separately.

Structural tests help all the involved parties identify a faulty chip and accelerate system and board diagnosis. Furthermore, the collection of structural diagnostic information of each integrated circuit in the ECU provides semiconductor manufacturers with valuable information for chip quality improvement. For this purpose, the collected diagnostic data should convey sufficient information to enable the detailed analysis of the most likely faulty locations in the chip. This diagnostic step requires only the handover of the gathered diagnostic data between the company applying the test and the semiconductor provider.

In this use-case the test application process is simpler than that of workshop test, since dedicated test interfaces may be available in the ECU and generic automotive test equipment may be used. However, the required diagnostic granularity in this use-case makes the analysis of the collected data much more elaborate.

Finally, there are no stringent requirements concerning the maximum amount of time devoted to test and diagnosis.

## 1.4.3. Power-Up/Down Test

Power-up and power-down tests take place before system initialization when power is first applied to the ECU and before system shut down, respectively. The application

of structural tests during ECU power-up/down serves two different purposes. On the one hand, they identify a faulty IC and direct the driver to the workshop, where the corresponding ECU can be replaced and further analyzed. On the other hand, they gather diagnostic information under realistic operating conditions. This offers the opportunity to accurately capture the underlying defect mechanism affecting chips and enables semiconductor manufacturers to optimize the analysis of any potential systematic fabrication problem.

The diagnostic benefits of power-up/down tests bring new challenges: As tests are conducted autonomously and any produced diagnostic data has to be stored on-chip, the diagnostic procedure has to be optimized to reduce storage costs. Consequently, any suitable diagnostic procedure has to support larger compaction ratios than those commonly used during traditional semiconductor failure analysis during IC manufacturing.

In order to ensure the safe application of power-up/down tests, additional constraints have to be met so that they do not interfere with the functional behavior of the system. As a rule of thumb in the industry, it is estimated that the time budget for power-up test is roughly 5 ms, while for power-down it amounts to 5 seconds. Furthermore, no external equipment is available during test.

#### 1.4.4. Online Test

Online structural tests are performed during the regular operation of the system. Therefore, as they may interfere with the system's functional tasks, their execution alongside regular applications has to be thoroughly analyzed. As a consequence, online structural tests are subject to stringent safety constraints.

The main purpose of online structural tests is to bring the system to a safe state in case of any malfunction. The required diagnostic granularity is, therefore, the ECU level. However, a more detailed diagnostic outcome is also desirable to support subsequent diagnostic activities in the workshop or during semiconductor failure analysis. As tests are conducted during vehicle operation, online tests offer a unique opportunity to capture in-field errors and further alleviate the NTF problem.

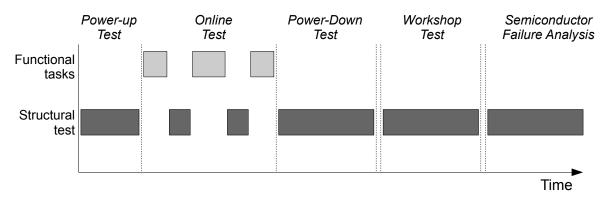

Figure 1.4 depicts the application of structural tests for the diagnostic use-cases in chronological order. Note how structural tests and functional tasks are interleaved

during online test.

Figure 1.4.: Diagnostic use-cases and test application

# 1.5. Organization and Contributions

This chapter has so far described semiconductor failure analysis problems in the automotive domain. The challenges tackled in this dissertation have been identified and the benefits of a structural diagnostic solution have been analyzed in the context of the automotive industry. Industrial requirements for a comprehensive diagnostic solution have been explained and categorized into diagnostic use-cases.

In the remainder of this dissertation, structural diagnostic methods and algorithms are presented that offer end-to-end diagnostic capabilities throughout the complete failure analysis process of complex systems.

The rest of this dissertation is organized as follows: the next chapter presents the foundations of structural test and diagnosis for random digital logic. The information described in that section comprises the fundamental concepts and techniques for the development of a suitable semiconductor diagnostic strategy.

Chapter 3 presents relevant related work in the area of system test and diagnosis of complex electronic systems.

Chapters 4 to 6 describe the developed structural diagnostic solutions for the analysis of semiconductor failures in complex embedded systems. The applicability to the presented diagnostic use-cases in the automotive domain is discussed in these chapters where appropriate.

Chapter 4 details a conceptual system architecture for efficient access to on-chip test infrastructure during system-level test. The components and operation of this architecture are explained and an industrial case-study is presented, where a viable diagnostic solution is realized.

Chapter 5 presents an approach to logic diagnosis using highly compacted test signatures. The performance of the developed diagnostic algorithm can be tuned to the number of faults and the volume of test response data expected in various diagnostic applications.

Chapter 6 describes a novel architecture for autonomous test and diagnosis of logic circuits. The presented diagnostic solution strongly reduces the amount of test data to be stored on-chip, both for the generation of test patterns and for the compaction of test responses.

Chapter 7 analyzes the performance of the presented diagnostic solutions. The algorithms of chapter 5 are evaluated by means of the achieved diagnostic accuracy, while the diagnostic architecture of chapter 6 is evaluated in terms both of diagnostic accuracy and hardware costs.

Finally, chapter 8 provides a summary of this work and a few concluding remarks about the contribution of this dissertation, which may pave the way for further research in this field.

# 2. Structural Test and Diagnosis

Structural test and diagnosis play a fundamental role in chip manufacturing. Therefore, a lot of research effort has been already devoted to realize effective and cost-efficient test and diagnostic solutions. In the following sections, the fundamental ideas behind structural testing are briefly presented. These concepts and techniques provide the foundations for the contributions of this dissertation.

#### 2.1. Defects and Faults

A defect is any distortion or undesired physical property in a manufactured silicon chip. A defect may have a fixed location in the chip (defect site) or it may be distributed among multiple defect sites. The focus of this dissertation is on defects in a defined location in the chip. Such defects are also referred to as spot defects. The nature of a defect is tightly coupled to the underlying defect mechanism, that is, the physical process that originates defects in the manufacturing process. Understanding the characteristics of defect mechanisms affecting chip fabrication is the most important goal semiconductor manufacturers pursue during failure analysis, as this information allows continuous improvement of yield and product quality.

Faults are defect representations that capture the most important defect properties and observable behavior. A fault models an alteration in the function of a circuit without regard to the physical characteristics of the chip. Therefore, faults offer a useful abstraction for the efficient development of test and diagnostic algorithms without considering exact physical device properties.

# 2.2. Fault Modeling

A fault model specifies the characteristics of the faults assumed to reflect the behavior of a physical problem in the chip. One of the most widely used fault models is the *stuck-at* model [Eldred59], where a faulty signal has its value fixed either to logic 1 (*stuck-at-1*) or to logic 0 (*stuck-at-0*). Stuck-at faults are *static* faults. That is, their behavior is fully specified by the current state of the circuit. Conversely, *dynamic* faults are also influenced by any circuit state that took place in the past. For example *gross delay faults* [Krstic98], also known as *transition delay faults*, assume that the delay of a gate is large enough so that a transition in its output is not observed in any of the circuit's outputs. For such a fault to occur, the logic state of the gate's output has to change its value in two consecutive clock cycles. Other less restrictive models account for the fact that the delay of a single gate may not be enough to make every propagation path fail. These faults are known as *small delay faults* [Park88] and their importance is increasing due to narrow timing margins and variations in newer manufacturing technologies.

More complex fault models have also been devised to resemble defects more closely. Several fault models describe *bridging faults* [Wunderlich10]. They model the various effects the unintended connection of signal lines may have on one another. Similarly, *crosstalk faults* describe capacitive couplings between neighboring lines, which are prone to experiencing additional delay or unexpected glitches [Chen97].

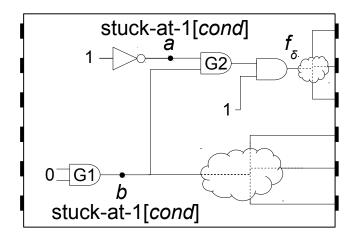

In order to analyze complex defect mechanisms, the *conditional stuck-at (CSA)* fault model [Holst12] offers a powerful generalization method to describe arbitrary faults. The representation of a CSA is:

#### stuck-at[condition]

A fault in this model behaves as a stuck-at fault when its activation condition evaluates to true. Alternatively, the corresponding signal line remains fault-free if the activation condition is not satisfied. That is, depending on the activation condition, a line may behave as a stuck-at-1 or stuck-at-0 fault for some patterns, or as a fault-free line for other patterns that would detect an *unconditional* stuck-at fault on this line. For instance, stuck-at-0-v[v] is a stuck-at-0 on signal line v, stuck-at-1- $v[\bar{v}]$  a stuck-at-1 on v, while stuck-at-0- $v[\bar{v}_0 \land v_1]$  describes a slow-to-rise transition delay fault. Similarly, CSA descriptions of more complex faults can also be easily derived [Holst12].

# 2.3. Scan Design

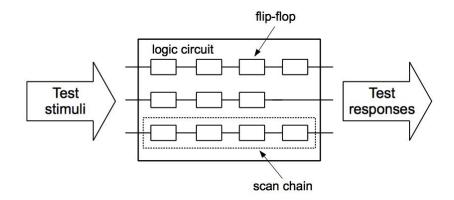

The testability of a logic core is determined by two main metrics: *controllability* and *observability*. Scan design [Eichelberger77] is one fundamental technique to improve the testability of any logic design and make structural tests more effective and efficient. As Figure 2.1 shows, the idea behind scan design is to introduce a piece of design-fortest (DfT) infrastructure to connect internal state elements, like latches or flip-flops, into one or more shift registers or *scan chains*, which can be controlled and observed externally without regard to the their surrounding logic resources.

During structural tests any desired logic value can be shifted into a scan chain. Then, one or a few *capture* clock cycles are applied to the circuit in regular mode and, finally, the captured logic values can be shifted out of the scan chain so that the test result can be evaluated.

Figure 2.1.: Principle of scan design

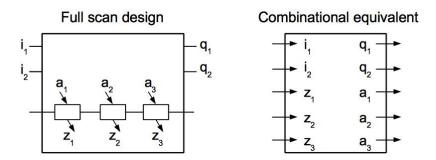

The inputs of scannable state elements are known as pseudo-primary inputs (PPIs) and their outputs as pseudo-primary outputs (PPOs). If each state element in a circuit is part of a scan chain, the circuit is said to be a *full scan design*. The benefit of full scan is that, as shown in Figure 2.2, the circuit can be represented with an equivalent combinational circuit where the pseudo-primary inputs and pseudo-primary outputs can be regarded as regular inputs and outputs, respectively. Furthermore, as long as the added DfT infrastructure is fault-free, any test and diagnostic algorithm for combinational circuits may also be used for sequential circuits without modification.

In the remainder of this dissertation, circuits are assumed to be full scan designs.

Figure 2.2.: Full scan design and equivalent combinational representation

# 2.4. Access to On-Chip Test Infrastructure

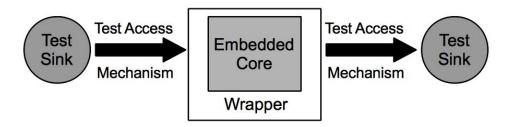

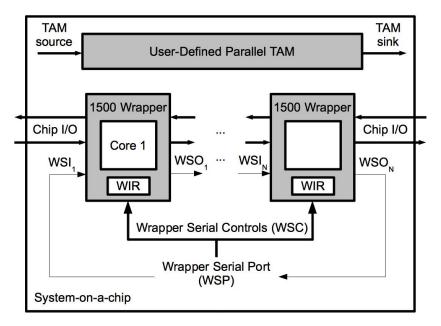

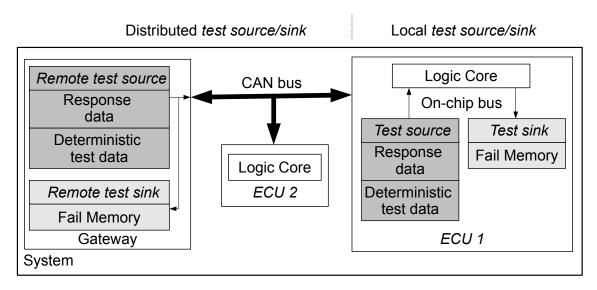

The design of today's complex systems-on-chip (SOCs) involves the integration of specialized intellectual property (IP) blocks into a single chip. These IP blocks are designed and verified once and reused for several designs. SOC designers usually acquire off-the-shelf IP cores in order to realize increasingly complex functionality in a relatively short amount of time. However, special DfT resources are needed so that these cores can also be tested efficiently once integrated into a chip. The conceptual architecture for modular core test of SOCs is shown in Figure 2.3 [Zorian98]. It comprises three main components:

- *Test source and sink*. The *test source* generates test patterns to be applied to the logic core, while the *test sink* receives the test responses and compares them to their expected values. The test source and sink may be located either on-chip or off-chip, within the system or in a remote location.

- *Test access mechanism (TAM)*. The TAM transports test data. It provides the communication means between the embedded core and the *test source* and *test sink*.

- *Core test wrapper*. The core test wrapper provides an interface that enables the communication between the embedded core and its environment. It isolates a core so that it can be tested on its own, without regard to the rest of the on-chip resources. Finally, the test core wrapper also connects the embedded core to the available TAM.

The challenges to architect an efficient modular test solution for SOCs have originated important standardization efforts [JTA, IEE, Stollon11] and sparked research methodologies for test scheduling optimization [Wang06a]. In the following subsections, the

Figure 2.3.: Conceptual SOC test architecture [Zorian98]

most relevant standardization efforts are summarized, which offer potential to ease test integration.

#### 2.4.1. IEEE 1149.1 Standard

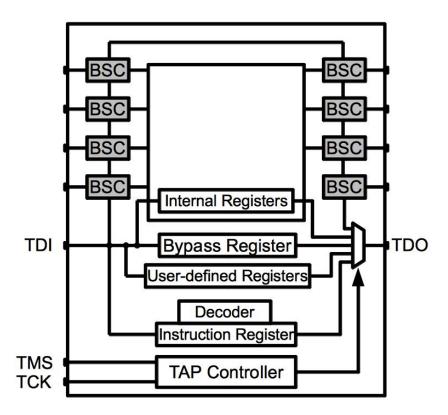

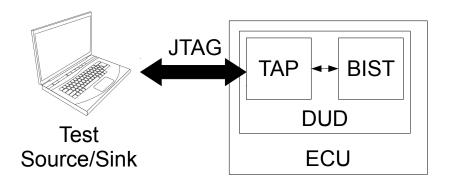

The IEEE 1149.1 standard [JTA] or *joint test action group (JTAG)* was originally devised for testing the interconnection between several integrated circuits (ICs) on a printed circuit board (PCB). This technique, also known as *boundary scan*, connects all chip's input/output (IO) pins into a single shift register, so they can be easily controlled and observed. Since its conception, the IEEE 1149.1 has also been widely used as a generic interface to gain access to internal circuit structures for debug and test.

The minimal realization of this interface consists of four mandatory IO pins, namely, test clock (TCK), test mode select (TMS), test data input (TDI) and test data output (TDO). As Figure 2.4 shows, the IEEE 1149.1 standard includes a test access port (TAP) controller, which implements a standardized finite state machine in order to access the boundary scan cells or other internal registers that realize additional built-in features in the chip. The instruction register configures the state of the device to perform the desired operation. The provided functionality is further controlled with the corresponding data register.

*User-defined registers* offer additional services not covered by the standard, while the *bypass register* connects the TDO to the TDI pin through a one-bit shift register in order to provide faster access to other daisy-chained devices connected to the same IEEE 1149.1 interface.

Figure 2.4.: IEEE 1149.1 architecture [JTA]

#### 2.4.2. IEEE P1687

The complexity of today's systems-on-chip has lead to the extensive use of on-chip instrumentation for test, debug, diagnosis, power management, and on-chip measurements. The upcoming IEEE P1687 standard [Stollon11], also known as *internal joint test action group (IJTAG)*, aims at providing a common description of on-chip embedded features as well as standardized communication protocols to interact with embedded instruments. The IEEE P1687 proposal is an extension of the IEEE 1149.1 standard to make use of the TAP controller to manage the operation of on-chip instruments.

The complexity in the access to embedded on-chip instruments that comply with the IEEE P1687 has justified recent research efforts for instrument access verification [Zadegan11, Baranowski12], optimization [Larsson12, Baranowski13a] and protection [Baranowski13b].

#### 2.4.3. IEEE 1500 Standard

Complex integrated circuits place additional requirements on the test application process well beyond the capabilities of the IEEE 1149.1 standard. Such designs make use of hierarchical IP blocks from different core providers, which require very efficient test access mechanisms for test integration. As Figure 2.5 shows, the IEEE 1500 standard [IEE] provides a test wrapper for the IO terminals of each core and exposes an interface with which the test application can be controlled. Such common interface for core-based test specifies the interaction between logic cores in order to facilitate test reuse.

The IEEE 1500 wrappers consists of a mandatory wrapper serial port (WSP) and an optional parallel TAM. The WSP consists of the wrapper serial input (WSI) and the wrapper serial output (WSO) and several wrapper serial control signals. Similar to the IEEE 1149.1 standard, the IEEE 1500 wrapper defines a wrapper instruction register (WIR), which determines the instruction to be executed in the core. This register can select predefined functionality, for example, to bypass the entire core or to configure wrapper boundary cells into a shift register. However, the WSP does not make use of a TAP controller and the input signals of the wrapper's interface are applied directly to the core. The IEEE 1500 test wrapper also supports an optional parallel TAM in order to increase the efficiency of SOC testing.

The IEEE 1500 standard defines the interface between the core wrapper and the TAM, while the design of the TAM itself is left open for SOC integrators.

# 2.5. Logic Built-In Self-Test

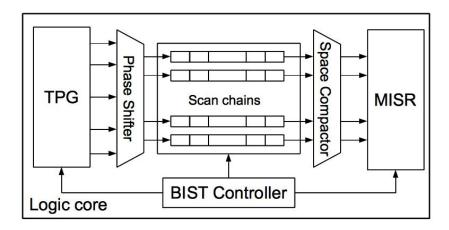

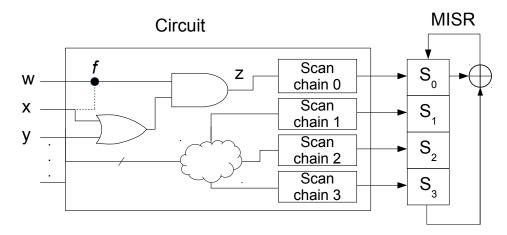

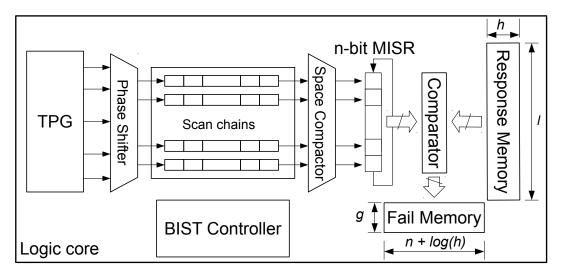

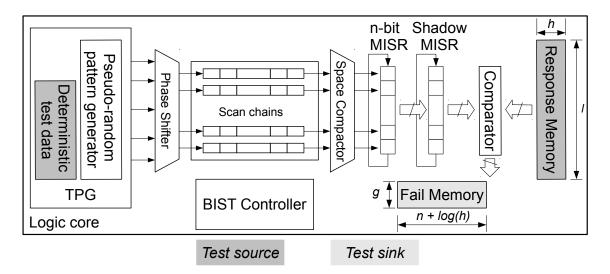

Logic built-in self-test (BIST), or LBIST, integrates DfT resources for autonomous test pattern generation and on-chip response compaction [Wunderlich98].

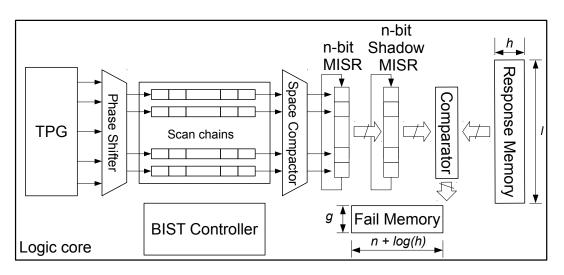

The most widely used LBIST architecture is shown in Figure 2.6, commonly referred to as the *STUMPS* architecture (self-testing unit using MISR and parallel sequence generator) [Bardell82]. A test pattern generator (TPG) produces inexpensive pseudo-random test patterns (PRPs). As most designs cannot be sufficiently tested with random patterns, most logic BIST solutions employ one of two approaches. The design can be modified by means of *test point insertion* so that PRPs are more likely to exercise a

#### 2. Structural Test and Diagnosis

Figure 2.5.: Overview of the IEEE 1500 standard [IEE]

larger portion of the chip. Alternatively, deterministic patterns can be generated for the remaining undetected faults after the application of inexpensive patterns. These patterns are encoded and stored on-chip, and later reconstructed for test application. This test application procedure is known as *mixed-mode BIST* [Hakmi07, Hakmi09, Hellebrand92, Hellebrand98, Könemann91, Könemann01, Rajski04, Volkerink03].

The test patterns produced by the TPG are usually fed into parallel scan chains by means of a *phase shifter*. The phase shifter removes linear dependencies in the produced test sequence, which negatively affect achievable fault coverage [Rajski00].

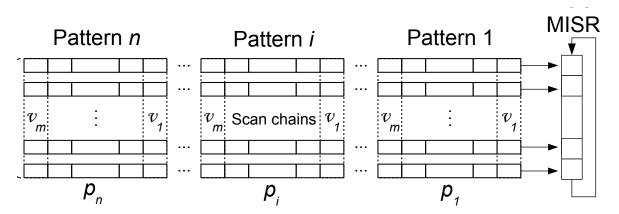

After the application of one or more capture cycles, test responses in the scan chains are shifted out and compacted in space (*space compactor*) [Mitra04] and then compacted in time by means of a multiple-input signature register (MISR). During MISR compaction, the following test pattern is simultaneously shifted into the scan chains.

A logic built-in self-test (LBIST) test session usually compacts the whole test application into a single test *signature*, which is later compared to the expected good signature. As test results are accumulated over time, any source of undefined values ("X" values) may compromise the test outcome. The most common sources for "X" values are, for example, analog blocks, memories and non-scannable storage elements, combinational feedback loops, asynchronous set/reset signals, tristate buses, false paths, among others [Wang06a]. Therefore, any LBIST solution requires careful considera-

tion to mask out any undefined value before it propagates to the test signature [Hetherington99, Tang06, Czysz10].

A LBIST controller manages the test application process by generating clocks, scan enable signals and control signals for the TPG and MISR.

Figure 2.6.: STUMPS architecture

As LBIST solutions can apply structural tests without the need of external equipment, they are well-suited for safety-critical or mission-critical operations, like those usually found in the automotive, telecommunications, networking and health care domains, where autonomous in-system self-tests are advantageous to improve system reliability and conduct remote diagnostics [Vo06, Wang06a, Qian09].

In the next sub-sections, the most fundamental LBIST techniques for test pattern generation and response compaction are analyzed in some detail.

## 2.5.1. Test Pattern Generation

Test pattern generation for LBIST is most commonly accomplished by means of *linear* feedback shift registers (LFSRs). LFSRs are one of the fundamental building blocks for pseudo-random testing, pseudo-exhaustive testing, and on-chip deterministic pattern decoding [Rajski04].

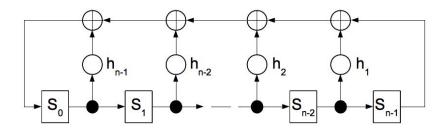

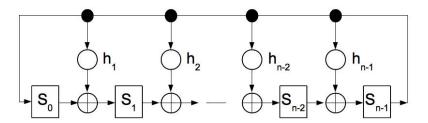

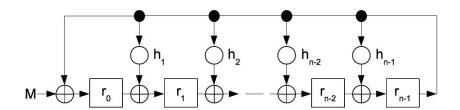

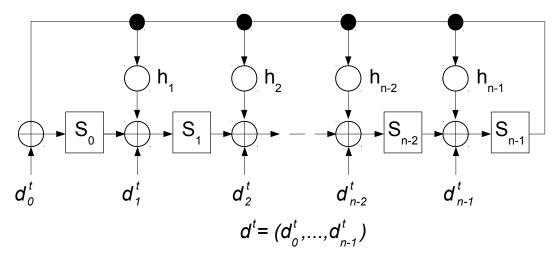

LFSRs consist of D flip-flops and a linear feedback network [Wang06a]. Figure 2.7 shows the *standard LFSR*, where the XOR gates are placed in the external feedback path. Conversely, the *modular LFSR*, shown in Figure 2.8, has XOR gates placed between two adjacent flip-flops.

# 2. Structural Test and Diagnosis

Figure 2.7.: *n*-stage standard LFSR

Figure 2.8.: *n*-stage modular LFSR

The structure of an n-stage LFSR is characterized by a generator polynomial f(x) of degree n.

$$f(x) = 1 + h_1 x + h_2 x^2 + \dots + h_{n-1} x^{n-1} + x^n$$

The coefficients  $h_i \in \{0,1\}$  of f(x) specify the presence or absence of a feedback path between flip-flop i and flip-flop i-1.

The operation of both standard LFSRs and modular LFSR can be described by a Galois field of order 2 (GF(2)). The state of an LFSR in the next clock cycle S(t+1) can be expressed in terms of the current LFSR state S(t). For a standard LFSR this transition function is [Bushnell00]:

$$S(t+1) = T_{Standard} \cdot S(t)$$

where  $T_{Standard}$  is:

$$T_{Standard} = \begin{bmatrix} 0 & 1 & 0 & \cdots & 0 & 0 \\ 0 & 0 & 1 & \cdots & 0 & 0 \\ \vdots & \vdots & \vdots & \ddots & \vdots & \vdots \\ 0 & 0 & 0 & \cdots & 0 & 1 \\ 1 & h_1 & h_2 & \cdots & h_{n-2} & h_{n-1} \end{bmatrix}$$

(2.1)

Similarly, for a modular LFSR the transition function is [Bushnell00]:

$$S(t+1) = T_{Modular} \cdot S(t)$$

and  $T_{Modular}$  is:

$$T_{Modular} = \begin{bmatrix} 0 & 0 & 0 & \cdots & 0 & 1 \\ 1 & 0 & 0 & \cdots & 0 & h_1 \\ \vdots & \vdots & \vdots & \ddots & \vdots & \vdots \\ 0 & 0 & 0 & \cdots & 0 & h_{n-2} \\ 0 & 0 & 0 & \cdots & 1 & h_{n-1} \end{bmatrix}$$

$$(2.2)$$

A *primitive polynomial* is a generator polynomial, which produces all possible states of an n-stage LFSR with the exception of the all-zero state. Such an LFSR with a primitive polynomial reaches  $2^n - 1$  states and is known as *maximum-length LFSR*. A primitive polynomial p(x) divides the polynomial  $1 + x^k$  for  $k = 2^n - 1$  but not for any other value smaller than k [Wang06a].

# **Pseudo-Random Testing**

Inexpensive pseudo-random patterns can be generated on chip and applied to the circuit-under-test (CUT) [Bardell87]. Test pattern generators for pseudo-random testing are usually based on maximum-length LFSRs. They can produce test sequences with uniformly distributed 1's and 0's. That is, the probability of generating either a 1 or a 0 in a test pattern is in both cases 0.5. Pseudo-random patterns may not achieve maximum fault coverage since they are unlikely to generate a test for *random-pattern resistant faults*. For example, a ten-input AND-gate requires all inputs to be simultaneously 1 in order to test for a stuck-at-0 at the gate output. Such a test pattern has low occurrence probability with a pseudo-random test pattern generator.

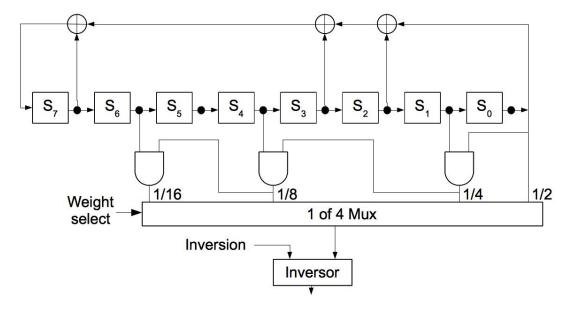

In order to improve fault coverage in pseudo-random testing, a *weighted LFSR* can be employed. A weighted LFSR extends an LFSR with combinational logic to bias the probability of producing a 1 or a 0. This can be easily achieved with the circuit of Figure 2.9, where k LFSR outputs feed a k-input AND-gate, producing a 1 with a probability of  $(0.5)^k$ . The desired output probability is chosen with the help of the *weight*

## 2. Structural Test and Diagnosis

select and inversion signals. Good results have been reported for output probability of a multiple of 0.25 [Chin84] and 0.125 [Wunderlich87].

Figure 2.9.: Weighted pseudo-random pattern generator [Bushnell00]

## **Exhaustive Testing**

Exhaustive testing applies all  $2^n$  different test patterns to an n-input combinational circuit [Barzilai83]. For this purpose, an n-stage maximum length LFSR can be used. Exhaustive testing achieves improved *defect coverage* since it relaxes the fault model assumptions for test generation. However, for large circuits the application of such a large number of test patterns becomes impractical [Bushnell00].

In order to reduce the size of the pattern set, *pseudo-exhaustive testing* [McCluskey84, Wang86, Hellebrand90] applies patterns to test the output functions of the circuit exhaustively. As each circuit's output depends only on a subset of the circuit's inputs, the number of required patterns is drastically reduced in comparison to regular exhaustive testing. For each output  $oldsymbol{o}\in O$  the test set  $T_o$  enumerates all possible input combinations in the *input cone* I(o) of  $oldsymbol{o}$ . That is, all inputs for which there is a topological circuit path to  $oldsymbol{o}$ . Therefore, the number of patterns to test the function of output  $oldsymbol{o}$  is  $2^{|I(o)|}$ . If the circuit's outputs are tested sequentially, the total number of patterns in the pattern set is  $\sum_{oldsymbol{o}\in O} 2^{|I(o)|}$ .

More recently, partial pseudo-exhaustive test (P-PET) [Mumtaz11] has been proposed to optimize pseudo-exhaustive test generation. In P-PET, only outputs with input cone |I(o)| < b are tested exhaustively, while the rest of the input cones are filled with pseudo-random patterns. To generate a P-PET sequence for a given bound b, a programmable LFSR [Hellebrand92] switches between several generator polynomials stored on chip, each one exercising a subset of inputs  $I_b = \Big\{I(o) \Big| \ |I(o)| \le b\Big\}$ , so that each input set in  $I_b$  receives all possible input combinations.

#### **Mixed-Mode BIST**

Non-exhaustive test pattern generation may suffer from insufficient fault coverage due to random-pattern resistant faults. In order to enhance fault coverage, test points can be inserted into the design [Krishnamurthy87, Touba96, Iyengar89]. They consist of control and observation points, which improve the fault detection capabilities of pseudo-random and pseudo-exhaustive pattern sequences. However, design modifications are sometimes not possible like, for example, for hard cores or macros, or have undesirable consequences like, hardware overhead and timing penalties.

Mixed-mode BIST is another approach to improve fault coverage that does not require any modifications to the target circuit. This technique generates deterministic patterns for random-pattern resistant faults and encodes them for efficient on-chip application [Hakmi07,Hakmi09,Hellebrand92,Hellebrand98,Könemann91,Könemann01,Rajski04,Volkerink03]. The decoding of the deterministic patterns for test application usually takes advantage of the available LFSR for pseudo-random or pseudo-exhaustive pattern generation. The deterministic test data are stored in the *seed memory*, which may be located either on-chip [Hakmi07, Hakmi09, Hellebrand92, Hellebrand98] or off-chip [Könemann91, Könemann01, Rajski04, Volkerink03].

# 2.5.2. Test Response Compaction

Test responses in a LBIST session account for such a large amount of information that they cannot be efficiently stored on-chip. Therefore, the output test data volume needs to be reduced at the expense of some information loss. This procedure is known as *test response compaction*. Usually, the responses of the complete test set are compacted into a single *signature* that represents a statistical property of the CUT. In order to identify

## 2. Structural Test and Diagnosis

a faulty chip, the produced test signature is compared to the known good signature.

Any technique used for test response compaction needs to ensure with sufficient confidence that the faulty and fault-free signatures are different. Otherwise, a faulty circuit can no longer be distinguished. In this case, the faulty test response is considered an *alias* of the correct response.

# **Signature Analysis**

Signature analysis is a technique for test response compaction based on *cyclic redundancy checking* [Peterson72]. The technique is realized using an LFSR to compact the output values in the scan chains [Wang06a]. In this subsection, the most common hardware structures for signature analysis are introduced. Then, the *aliasing probability* for these structures is derived. That is, the probability that a fault produces an error in the output response sequence, but the resulting signature is indistinguishable from the correct signature.

## • Serial-input signature register (SISR)

A single circuit output or scan chain can be compacted by means of an LFSR with an additional XOR input. Figure 2.10 shows such a n-stage serial-input signature register (SISR). The circuit's output response  $M = \{m_0, m_1, m_2, \cdots, m_{L-1}\}$  consists of L bits comprising the complete BIST session.

Figure 2.10.: *n*-stage single-input signature register (SISR)

*M* is represented by the polynomial:

$$M(x) = m_0 + m_1 x + m_2 x^2 + \dots + m_{L-1} x^{L-1}$$

After the L-bit output response is shifted in and compacted, the state of the SISR

$R = \{r_0, r_1, r_2, \cdots, r_{n-1}\}$  is given by:

$$r(x) = r_0 + r_1 x + r_2 x^2 + \dots + r_{n-1} x^{n-1}$$

The SISR compactor performs polynomial division between M(x) and f(x), where f(x) is the SISR characteristic polynomial. This operation is expressed by the formula:

$$M(x) = q(x)f(x) + r(x)$$

where the final SISR state or signature is the *polynomial remainder* r(x) if the SISR is implemented as a modular LFSR. For the standard LFSR, the polynomial remainder can be identified with a different state assignment [Bushnell00].

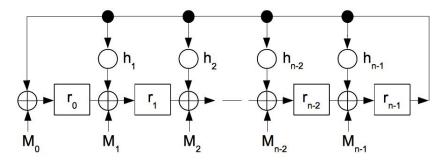

# • Multiple-input signature register (MISR)

In order to compact multiple outputs or scan chains simultaneously, a multiple-input signature register (MISR) can be used. A n-stage MISR compacts up to n output sequences of length L. Figure 2.11 shows such a MISR based on a modular LFSR, where the feedback signals and the corresponding output sequences are XOR-ed in each clock cycle.

Figure 2.11.: *n*-stage multiple-input signature register (MISR)

An *n*-input MISR can be modeled as a single input SISR, whose *effective input* sequence  $M_{eff}(x)$  is given by the expression:

$$M_{eff}(x) = M_0(x) + xM_1(x) + x^2M_2(x) + \dots + x^{n-2}M_{n-2}(x) + x^{n-1}M_{n-1}(x)$$

As a consequence, MISR compaction also performs polynomial division between  $M_{eff}(x)$  and the characteristic polynomial f(x):

$$M_{eff}(x) = q(x)f(x) + r(x)$$

## 2. Structural Test and Diagnosis

# • Aliasing probability

The probability that the correct output response and any faulty output response produce the same signature after compaction is known as the *aliasing probability*. The bounds on the aliasing probability  $P_A$  of an n-stage LFSR compactor can be calculated in terms of the error probability p of a single circuit output [Williams88]. If  $0 then <math>p^n \le P_A < (1-p)^n$ . Alternatively, if  $0.5 \le p \le 1$ , then  $(1-p)^n \le P_A \le p^n$ . Therefore, if the error probabilities are equally likely, the aliasing probability amounts to  $P_A = 2^{-n}$ , without regard to the initial state of the LFSR.

In the more general case when the error probability  $p \neq 0.5$ , the aliasing probability  $P_A$  also converges to  $2^{-n}$ . However, primitive characteristic polynomials reach this bound for shorter input sequences than non-primitive ones and offer the better choice for response compaction [Bushnell00].

In case the circuit's outputs  $o_j$  for  $j = \{1, 2, 3, \dots, n\}$  in an n-stage MISR have unique error probabilities, the aliasing probability is also  $P_A = 2^{-n}$ , as long as the outputs  $o_j$  are independent and their error probabilities  $p_j$  are not correlated [Williams88].

Under the same assumptions of statistically independent error probabilities, an intuitive way to determine the aliasing probability of an n-stage MISR is to consider the ratio between the total number of response sequences generating the fault-free n-bit signature, out of which one is the correct test response, and the total amount of response sequences. For a test sequence of length L and m circuit outputs or scan chains, where  $L>n\geq m\geq 2$ , the aliasing probability is [Wang06a]:

$$P_A = \frac{2^{mL-n} - 1}{2^{mL} - 1}$$

For  $L \gg n$ ,  $P_A \approx 2^{-n}$ .

The assumption that the outputs are independent usually does not hold in practice. However, output dependencies have only little impact on signature analysis [Bushnell00].

# 2.6. Logic Diagnosis

A comprehensive review of logic diagnosis for combinational circuits was presented in [Holst12]. In the following, only those approaches are discussed which are most relevant for the remaining chapters of this work, namely, the *inject-and-validate* and the *back-tracing* diagnostic paradigms.

# 2.6.1. Inject-and-Validate

The inject-and-validate paradigm relies on fault simulation to assess the degree to which a fault can *explain* the observed defect behavior. In contrast to prior work [Richman85], which make use of a *fault dictionary* to account for all possible defect mechanisms, inject-and-validate approaches do not assume that a fault model can perfectly describe the underlying failure behavior, but rather analyze the similarities between fault simulation and the observed test responses in order to infer the most likely fault locations or *candidates*.

One of the first such diagnostic approaches [Waicukauski89] identifies the stuck-at faults in the circuit, which are able to explain the biggest number of failing patterns. That is, for every fault  $f \in F$ , where F is the set of stuck-at faults in circuit C, each test pattern  $t \in T$  is simulated and compared to the observed circuit response  $C_{ud}$ . Let expl(T, f) be the subset of test patterns for which f explains the observed faulty response  $C^f(t)$ :

$$\operatorname{expl}(\mathsf{T},f) = \left\{ t \in \mathsf{T} \,\middle|\, \mathsf{C}^f(t) = \mathsf{C}_{\mathsf{ud}}(t) \neq \mathsf{C}(t) \right\}$$

The most likely fault candidates are:

$$\Big\{f \in \mathsf{F} \, \Big| \, | \exp \mathsf{I}(\mathsf{T}, f) \, | \, = \max \{ \, | \exp \mathsf{I}(\mathsf{T}, g) \, | \, \Big| \, g \in \mathsf{F} \} \Big\}$$

Later extensions of this diagnostic approach include the single location at a time (SLAT) method [Bartenstein01, Huisman04]. A test pattern  $t \in T$  has the SLAT property if there exists a fault  $f \in F$  that produces exactly the same test response as that of the circuit-under diagnosis  $C_{ud}$ :  $\exists f \in F$  with  $\exp(\{t\}, f) \neq \emptyset$ . The result of SLAT diagnosis is a set of *multiplets*, where a multiplet is a minimal subset of faults M able

## 2. Structural Test and Diagnosis

to account for all observed SLAT patterns and each fault  $f \in M$  explains at least one SLAT pattern.

Closely related to the SLAT property, the work in [Huang97] introduced the idea of *curable vectors* for design debug. A curable vector is a failing response that can be corrected by flipping a single signal line. This idea was first utilized for logic diagnosis roughly at the same time the SLAT approach was first presented [Huang01].

Several diagnostic approaches have extended the SLAT approach in order to take advantage of any diagnostic information in non-SLAT patterns [Lavo02, Wang06b, Zou06b, Liu07a]. They introduce new matching and scoring methods to improve diagnostic results. Diagnostic fault models have also been considered to account for complex failure mechanisms which are partly or totally explained by the composition of several simple faults [Millman90, Venkataraman00]. The SLAT technique has also been used to identify initial suspect lines, which are then analyzed according to specific fault models [Zou06a, Liu07b].

Most recently, the work in [Holst12] presents a generalization of the SLAT paradigm, which is able to extract failure information from both SLAT and non-SLAT patterns, even when test responses are highly compacted. Some of the main ideas behind these algorithms have also been used to deal with multiple interacting faults [Tang10, Ye11].

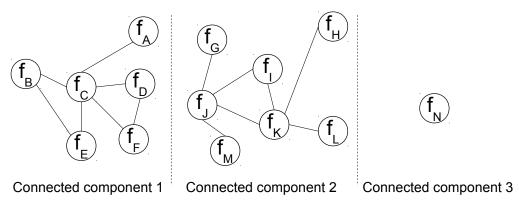

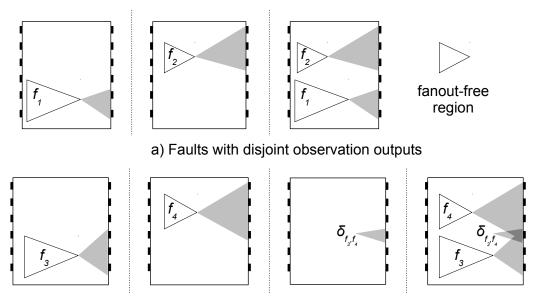

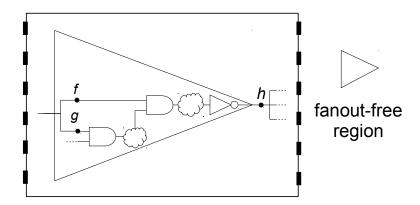

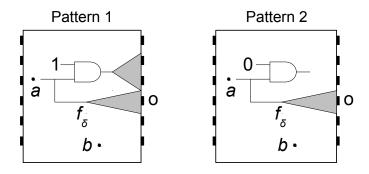

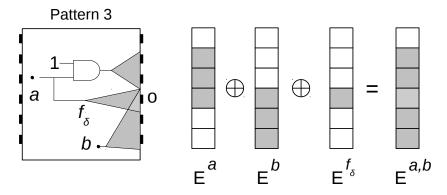

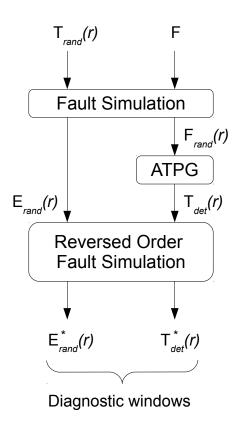

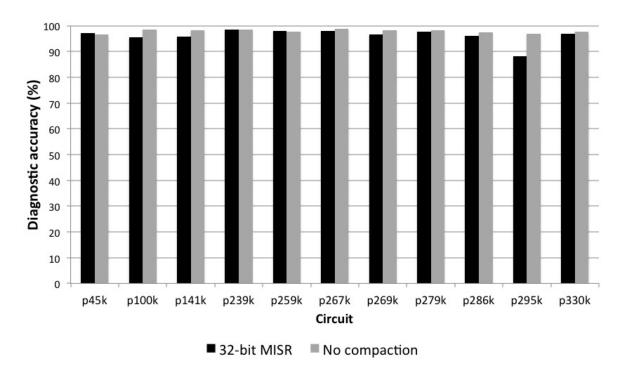

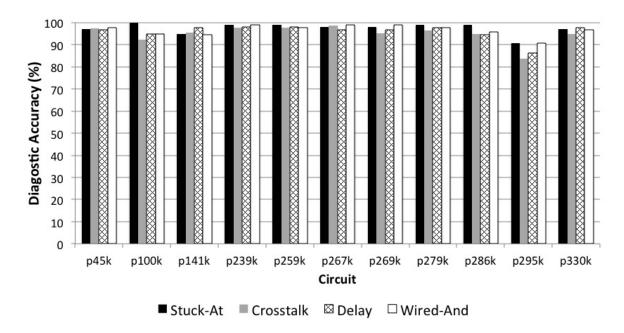

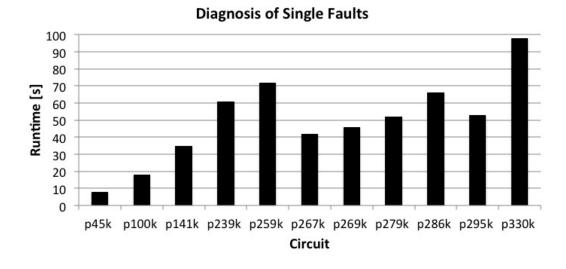

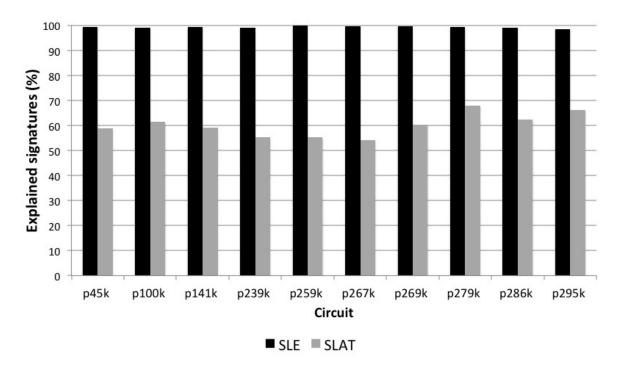

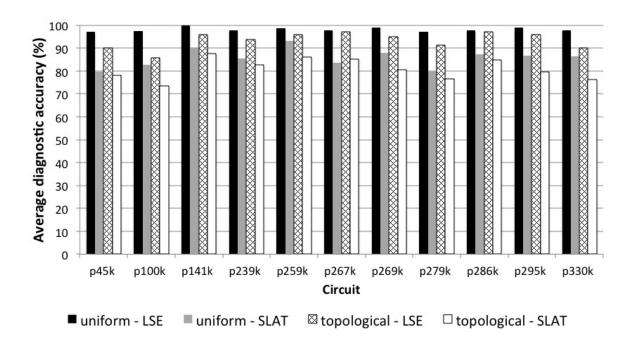

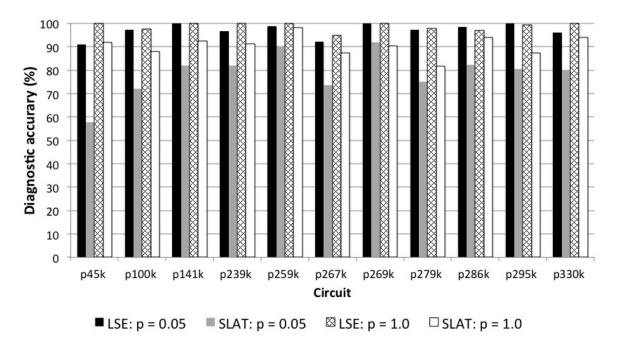

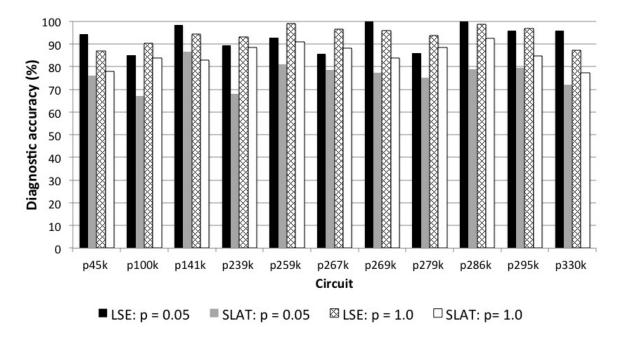

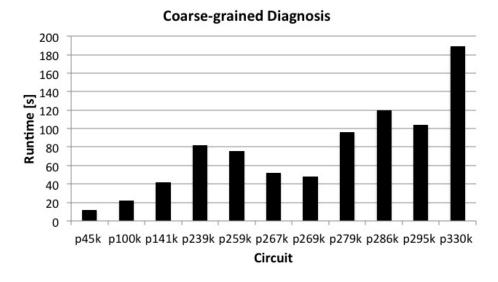

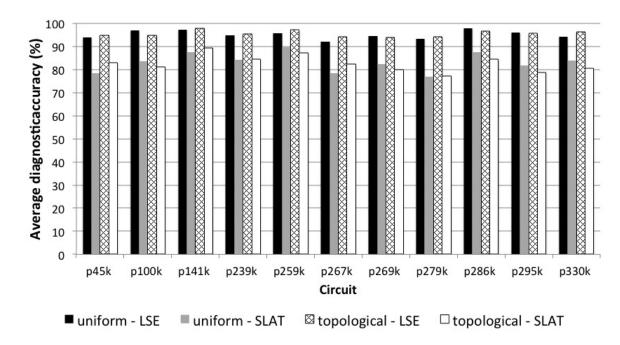

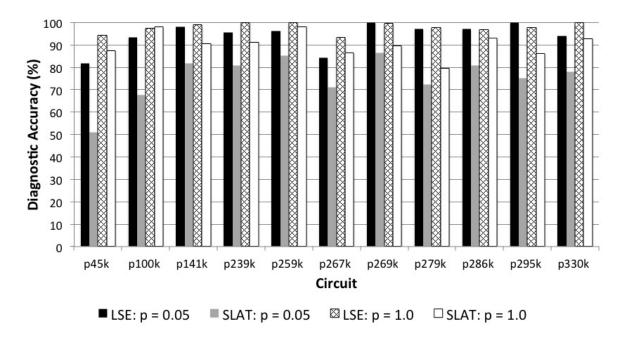

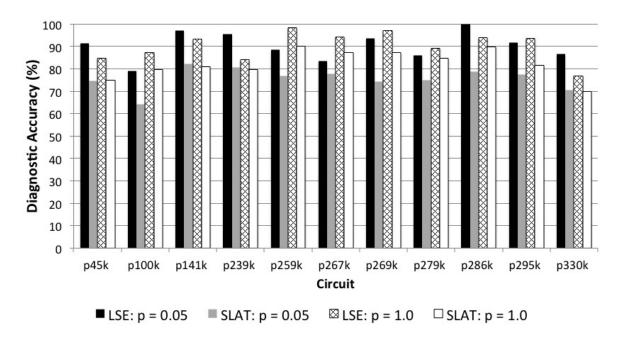

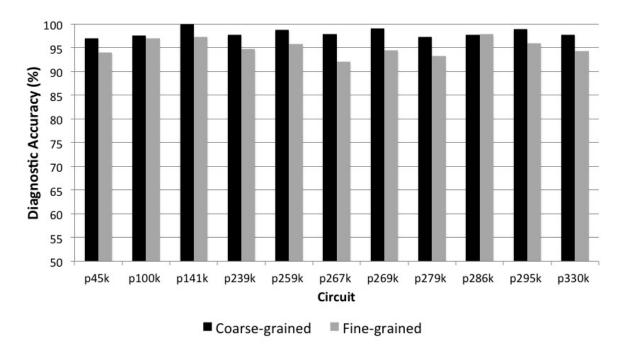

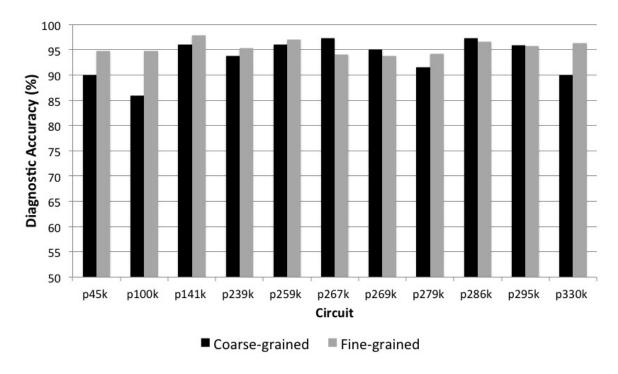

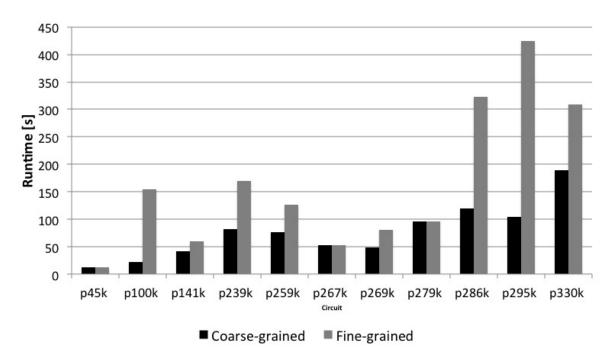

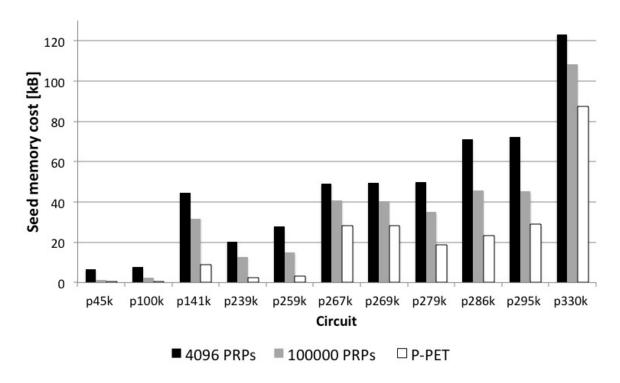

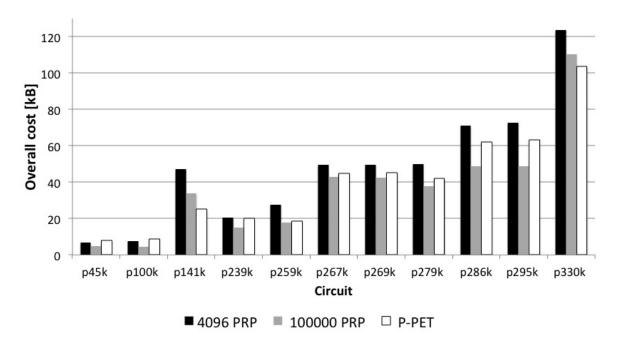

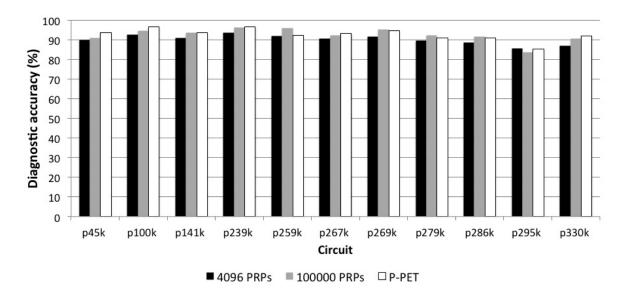

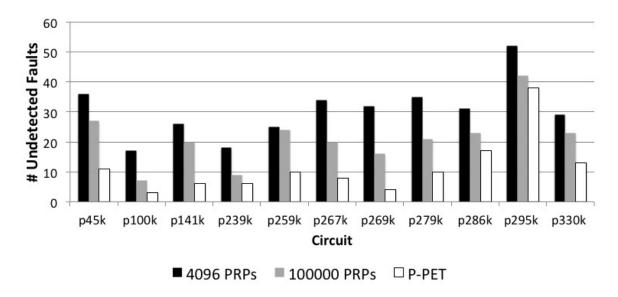

# 2.6.2. Back-Tracing