Institute of Computer Architecture and Computer Engineering

> University of Stuttgart Pfaffenwaldring 47 D-70569 Stuttgart

Master Thesis Nr. 00731-001

## Realistic gate model for efficient timing analysis of very deep submicron CMOS circuits

Deepthi Murali

| Course of Study:   | Master of Science in Information Technology             |

|--------------------|---------------------------------------------------------|

|                    |                                                         |

| Examiner:          | Prof. Dr. rer. nat. habil. Hans-Joachim Wunderlich      |

| Supervisor:        | DiplInf. Marcus Wagner                                  |

|                    | DiplInf. Eric Schneider<br>Dr. rer. nat. Michael Kochte |

|                    |                                                         |

|                    |                                                         |

| Commenced:         | 2015-09-14                                              |

| Completed:         | 2016-03-15                                              |

|                    |                                                         |

| CR-Classification: | B.8.2, C.4, J.6                                         |

|                    |                                                         |

### Erklärung:

Ich versichere, nach bestem Wissen und Gewissen, dass diese Arbeit kein Material und keine Quellen enthält, die bereits für das Erlangen eines akademischen Grades unter meinem Namen oder anderen Namen an einer weiteren Universität bzw. Hochschuleinrichtung veröffentlicht wurde, außer Quellen die als solche gekennzeichnet sind. Zusätzlich versichere ich, dass keine Teile dieser Arbeit in meinem Name in Zukunft eingereicht werden, um einen akademischen Grad an einer anderen Universität oder Hochschuleinrichtung zu erlangen ohne der Zustimmung der Universität Stuttgart.

Unterschrift: Stuttgart, den

Declaration:

I certify that this work contains no material which has been accepted for the award of any other degree or diploma in my name, in any university or other tertiary institution and, to the best of my knowledge and belief, contains no material previously published or written by another person, except where due reference has been made in the text. In addition, I certify that no part of this work will, in the future, be used in a submission in my name for any other degree or diploma in any university or other tertiary institution without the prior approval of the University of Stuttgart.

Signature: Stuttgart,

# Acknowledgement

I would like to take the opportunity to thank a number of people as I am presenting the results of my Master Thesis.

I would first like to thank Prof. Dr. Hans-Joachim Wunderlich for providing me the opportunity to do research at the institute. The regular meetings and feedback provided by him were very crucial to the completion of this thesis. Next, I would like to express my heartfelt gratitude to my supervisors Mr. Marcus Wagner, Mr. Eric Schneider and Mr. Michael Kochte. They took sincere efforts to keep me motivated so that I achieve all the goals of my thesis. Without their advice and guidance, I would have definitely been lost and I am very happy to have got them as my supervisors. I am also thankful to all other staff of the institute for their friendly attitude as it made me really comfortable to work at the institute.

I would specially like to thank the System Administrators, Mr. Helmut Häfner and Mr. Lothar Hellmeier, as they provided immediate help with all technical issues which were extremely important during the course of the thesis.

Last but not the least, I would like to thank my family and friends for extending their support throughout the duration of my thesis. Without their support, it would have been very difficult to go through all the good and bad times of my Thesis.

# Abstract

The continuously shrinking technology has made it possible for designers to incorporate more functionality with better performance at a much higher density in Integrated Circuits(ICs). Fast and accurate timing simulation of such large circuit designs using ever more complex transistor models has become a challenging problem. In modern circuits, the gate delay is severely affected by process variations, environmental variations and cross talk. Moreover, technology scaling has also resulted in significant increase in interconnect parasitics (including resistors and capacitors) which can dramatically reduce the performance of a circuit.

For the circuit design validation and delay test evaluation, the industry has long relied on fast gate-level timing simulators like ModelSim to validate the designs. However, with continued scaling and steadily increasing circuit performance requirements, gate level simulators can no longer provide acceptable simulation accuracy. On the other hand, circuit level SPICE simulation provides acceptable accuracy but at a very large computational cost. To provide a suitable trade-off between the accuracy of the SPICE simulation and the speed of the gate level simulation, this thesis proposes a realistic gate model which can be used for the fast and accurate timing simulation of circuits to analyze their timing behaviour.

In this thesis, a heterogeneous gate model that combines a simple gate model like Non-Linear Delay Model (NLDMs) and an advanced current source model (CSM) using a classifier is proposed. The simple gate model allows fast timing simulation and gives acceptable accuracy in many cases while the advanced gate model always provides more accurate and reliable results, but at a much higher computational cost. The classifier is designed to choose the advanced gate model depending on special cases (eg, multiple input switching) where the simple gate model gives inappropriate results. This heterogeneous gate model is further applied to develop a circuit simulator that enables fast and accurate post-layout and delay fault simulation.

# Contents

| A        | cknov    | wledge   | ment                                                                                                                    | i             |

|----------|----------|----------|-------------------------------------------------------------------------------------------------------------------------|---------------|

| Al       | Abstract |          |                                                                                                                         | iii           |

| 1        | 1.1      |          | ation and Goals of this Work                                                                                            | <b>2</b><br>2 |

|          | 1.2      | Organ    | ization of the Thesis                                                                                                   | 3             |

| <b>2</b> | Fun      | damen    | ntals of VLSI Circuit Modelling and Simulation                                                                          | 4             |

|          | 2.1      |          | ical Description of VLSI circuit                                                                                        | 4             |

|          |          | 2.1.1    | Elementary Devices                                                                                                      | 4             |

|          |          | 2.1.2    | Voltage and Current sources                                                                                             | 5             |

|          | 2.2      | MOSF     | $ETs \dots \dots$ | 7             |

|          |          | 2.2.1    | Physical Structure                                                                                                      | 8             |

|          |          | 2.2.2    | Device Operation                                                                                                        | 8             |

|          | 2.3      |          | Ε                                                                                                                       | 9             |

|          | 2.4      | Descri   | ption of a Spice Netlist                                                                                                | 9             |

|          |          | 2.4.1    | DC, AC and Transient Analyses in SPICE                                                                                  | 10            |

|          |          | 2.4.2    | Limitations of SPICE                                                                                                    |               |

|          | 2.5      |          | g Simulation in Design Flow of VLSI Circuit                                                                             | 11            |

|          |          | 2.5.1    | Functional simulation and pre-layout simulation                                                                         | 14            |

|          |          | 2.5.2    | Postlayout Simulation                                                                                                   | 15            |

|          |          | 2.5.3    | Definitions related to Circuit Timing                                                                                   | 17            |

| 3        | Stat     | te of th | ne Art in Circuit Timing Simulation                                                                                     | 19            |

| 0        | 3.1      |          | g Model - Gate and interconnect model                                                                                   | 19            |

|          | 3.2      |          | ent abstraction of simulators                                                                                           | 20            |

|          |          | 3.2.1    | Gate-Level Simulation                                                                                                   | 20            |

|          |          | 3.2.2    | Switch-level Simulation                                                                                                 | 22            |

|          |          | 3.2.3    | Transistor level Simulation                                                                                             |               |

|          |          | 3.2.4    | Circuit level Simulation                                                                                                | 24            |

|          | 3.3      | Interco  | onnect Modelling                                                                                                        | 24            |

|          |          | 3.3.1    | Lumped C model $\ldots$                | 25            |

|          |          | 3.3.2    | Lumped RC Model                                                                                                         | 26            |

| <b>4</b> | Des      | ign of   | a Heterogeneous Gate Model                                                                                              | <b>28</b>     |

|          | 4.1      | -        | Description                                                                                                             | 28            |

|          |     | 4.1.1 Overview                                                     | 28 |

|----------|-----|--------------------------------------------------------------------|----|

|          |     | 4.1.2 Impact of Multiple Input Switching on Gate Delay             | 29 |

|          |     | 4.1.3 Definition of Classifier                                     | 30 |

|          | 4.2 | Input and Output Waveform Model                                    | 33 |

|          | 4.3 | Simple Gate Model                                                  | 34 |

|          | 4.4 | Advanced Gate Model for a CMOS Inverter                            | 36 |

|          |     | 4.4.1 Important Cell Characteristics of a CMOS Inverter            | 36 |

|          |     | 4.4.2 Description of Current Source Model                          | 38 |

|          |     | 4.4.3 Current Source Model Characterisation                        | 39 |

|          | 4.5 | Advanced Gate Model for 2-input CMOS gate                          | 42 |

| <b>5</b> | App | plication to Circuit Simulation                                    | 44 |

|          | 5.1 | Circuit Simulation Algorithm                                       | 44 |

|          |     | 5.1.1 Traversal of Circuit Netlist                                 | 44 |

|          |     | 5.1.2 Summary of Heterogeneous Gate Model Simulation               | 45 |

|          | 5.2 | Computation of Gate Output Voltage Waveform                        | 46 |

|          |     | 5.2.1 Output Voltage Transition using Simple Gate Model            | 46 |

|          |     | 5.2.2 Output Voltage Transition using Advanced Gate Model          | 46 |

|          | 5.3 | Simulation of VLSI Interconnect Parasitic Elements                 | 47 |

|          |     | 5.3.1 Approximation using Lumped C Model                           | 47 |

|          |     | 5.3.2 Exact simulation of RC interconnects for advanced gate model | 47 |

|          | 5.4 | Using SPICE simulation as Advanced Algorithm                       | 50 |

| 6        | Exp | perimental Results                                                 | 51 |

|          | 6.1 |                                                                    | 51 |

|          |     | 6.1.1 Small Circuits for Gate Model Evaluation                     | 51 |

|          |     | 6.1.2 Medium Sized Circuits for Simulation Scalability Evaluation  | 53 |

|          | 6.2 | Input Vector-Pairs used for Simulation                             | 54 |

|          | 6.3 | Reference Simulations                                              | 54 |

|          |     | 6.3.1 Using Circuit-Level Simulator HSPICE                         | 54 |

|          |     | 6.3.2 Using Gate-Level Simulator HDLSIM                            | 55 |

|          | 6.4 | Circuit Simulation Results                                         | 55 |

|          |     | 6.4.1 Results without Interconnect Parasitic Capacitances          | 56 |

|          | ~ ~ | 6.4.2 Results with Interconnect Parasitic Capacitances             | 56 |

|          | 6.5 | Simulation Results using SPICE as Advanced Algorithm               | 57 |

|          | 6.6 | Summary of results                                                 | 57 |

| 7        |     | nclusion and Future Work                                           | 59 |

|          | 7.1 | Conclusion                                                         | 59 |

|          | 7.2 | Future Work                                                        | 59 |

# List of Figures

| 2.1  | Symbol of a resistor                                                               | 4  |

|------|------------------------------------------------------------------------------------|----|

| 2.2  | (a)Symbol of a non-polarised capacitor (b)Symbol of a polarised capacitor          | 5  |

| 2.3  | Symbol of a variable capacitor                                                     | 5  |

| 2.4  | Symbol of a DC voltage source with a dc voltage of $V_{dc}$                        | 6  |

| 2.5  | Symbol of a DC current source with a dc current of $I_{dc}$                        | 6  |

| 2.6  | Symbol of a dependent current source $I(v)$ $\hdots$                               | 6  |

| 2.7  | Symbol of ground in a circuit                                                      | 7  |

| 2.8  | (a)n-channel enhancement MOSFET (b) p-channel enhancement MOS-                     |    |

|      | FET (c)n-channel depletion MOSFET (d) p-channel Depletion MOSFET                   | 7  |

| 2.9  | Structure of a n-channel MOSFET                                                    | 8  |

| 2.10 | Transient Analysis of RC circuit in SPICE                                          | 10 |

| 2.11 | Y chart representation of IC design flow                                           | 12 |

| 2.12 | Design Flow of ICs and simulation steps involved                                   | 13 |

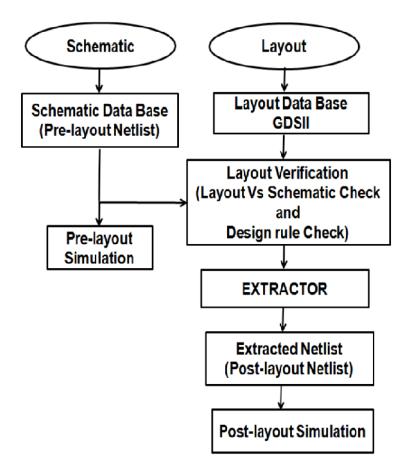

|      | Pre and post layout Simulation Steps                                               | 14 |

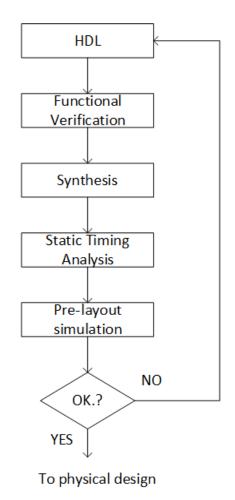

|      | Steps of Logic phase of Design                                                     | 15 |

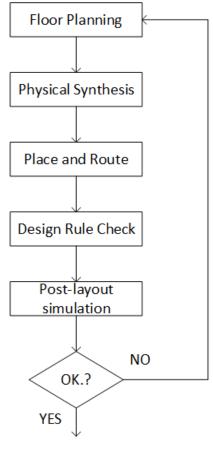

|      | Steps of physical phase of Design                                                  | 16 |

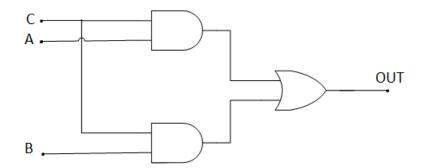

|      | Combinational Circuit                                                              | 17 |

|      | Sequential Circuit with a Flip-Flop                                                | 17 |

| 2.18 | Input and output waveform of an Inverter                                           | 18 |

| 3.1  | Block Diagram of a timing model                                                    | 19 |

| 3.2  | Relative accuracy and runtime of the timing simulation with gate and in-           |    |

|      | terconnect models of different abstraction levels                                  | 20 |

| 3.3  | NLDM measurement points                                                            | 21 |

| 3.4  | Resistive Switch Representation                                                    | 23 |

| 3.5  | RC network reduction using Lumped C model                                          | 26 |

| 3.6  | RC network reduction using Lumped RC model                                         | 26 |

| 4.1  | Proposed heterogeneous gate model for efficient timing simulation                  | 29 |

| 4.2  | CMOS NOR gate                                                                      | 30 |

| 4.3  | Block diagram of the efficient classifier                                          | 31 |

| 4.4  | Fall propagation delay $d_R^Z$ of 2-input NOR gate as a function of $\delta^{A,B}$ |    |

| 4.5  | (a) Propagation delay vs. Rise time of input signal A (b) Propagation              |    |

|      | delay vs. Fall time of input signal A                                              | 32 |

| 4.6  | Output transition time vs. Transition time of input signal A                       | 33 |

| 4.7  | (a) gate delay vs. RSAT (b) output transition time vs. RSAT                        | 33 |

| 4.8  | Example of a PWL Waveform                                                          | 34 |

|      |                                                                                    |    |

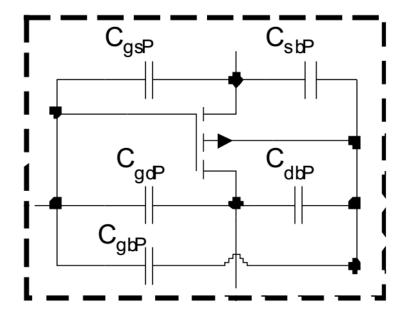

| 4.9  | p-MOSFET parasitics                                                                  | 37 |

|------|--------------------------------------------------------------------------------------|----|

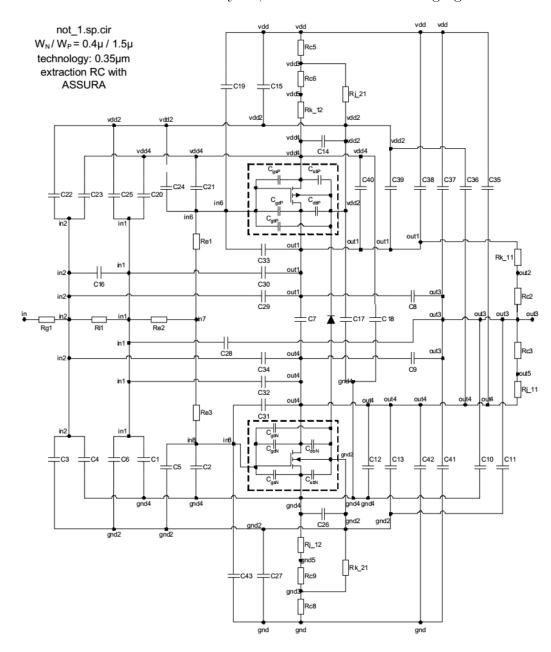

| 4.10 | Schematic of inverter gate after layout extraction                                   | 38 |

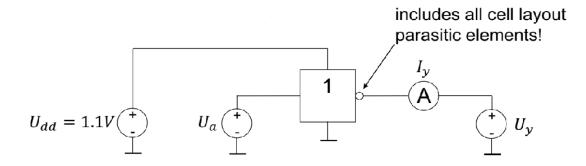

| 4.11 | Gate model for single input switching                                                | 39 |

| 4.12 | Current characterization for INV_X1 gate                                             | 40 |

| 4.13 | Setup to extract the miller capacitance $\mathrm{C}_m$                               | 41 |

| 4.14 | Setup to extract the output capacitance $C_o$ of the inverter $\ldots \ldots \ldots$ | 42 |

| 4.15 | Gate model for 2-input CMOS gate with MIS                                            | 43 |

| 5.1  | Flowchart of circuit simulation based on heterogeneous gate model                    | 45 |

| 5.2  | RC interconnect representation between a driving gate output and a re-               |    |

|      | ceiving gate input (not shown)                                                       | 48 |

| 5.3  | Simplified gate model for advanced algorithm                                         | 48 |

| 5.4  | Gate model for NOR2 gate with interconnects and NanGate Cells as loads               | 50 |

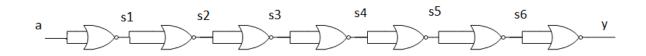

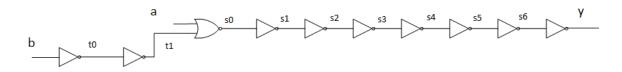

| 6.1  | Inverter chain (inv_chain)                                                           | 52 |

| 6.2  | Chain of 2-input NOR gates (nor2_chain)                                              |    |

| 6.3  | Chain of 2-input NOR gate and inverter gate (nor2_inv_chain)                         | 53 |

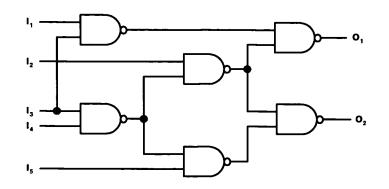

| 6.4  | Circuit netlist of ISCAS85 c17 circuit                                               | 53 |

|      |                                                                                      |    |

# List of Tables

| 6.1 | ISCAS85 circuit characteristics                                                            | 53 |

|-----|--------------------------------------------------------------------------------------------|----|

| 6.2 | Average simulation results for circuits without interconnects                              | 56 |

| 6.3 | Average simulation results with CSM as advanced gate model                                 | 56 |

| 6.4 | Average simulation results with ngspice shared library as advanced gate                    |    |

|     | $\mathrm{model}  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  $ | 57 |

# Chapter 1

# Introduction

## 1.1 Motivation and Goals of this Work

The design optimizations, validation and delay test methodologies of modern day Integrated Circuits (ICs) require accurate and fast timing analysis techniques. With the steadily increasing performance requirements of modern circuits, even the smallest inaccuracy in the delay prediction can be catastrophic - for both asynchronous and synchronous circuits. Ideally, the circuit would be simulated in the most detailed level possible viz, the circuit level simulation. The most commonly used tool for circuit level timing simulation is SPICE. However, this is extremely slow. For example, to evaluate the effectiveness of delay tests, it is necessary to perform accurate timing simulation of a large number of input vector pairs.

Conventionally, the industry relied on certain gate-level simulation tools like ModelSim, for the validation of the new design and for delay test evaluation. For this, it used the delay information from the Standard Delay Format (SDF) files. However, with the continued down-scaling of technology, the delay of a logic gate has become severely affected by various new factors like cross-talk, noise, process-variations, etc. Another important effect that dominates the delay of the circuit is the impact of interconnect parasitics, which increases dramatically with growing technology generations [1]. Therefore, the very simple and abstract gate models used by gate-level timing simulation have become very inaccurate. A new gate models on transistor level must be designed that incorporate all these factors in order to give fast and accurate simulation results.

Moreover, with continuous technology scaling, circuits have become more prone to defects, e.g. a wire with an extremely large resistance or a very small resistance between neighbouring wires, which were supposed to be completely isolated. To detect such a fault, we apply a vector pair to the circuit and check if the time of the last transition at the output is smaller than the clock cycle time. This is referred to as delay fault simulation. When there are large number of vector pairs, numerous SPICE simulations of the circuit are required to be carried out and these have to be extremely fast. However, circuit simulation program like SPICE use very complex and accurate MOSFET models like BSIM4 that has hundreds of transistor parameters and hence, this method of simulation proves to be computationally very expensive. Added to this, SPICE simulation also results in the use of a lot of CPU time and memory.

The gate model used by a circuit simulator is of critical importance as it determines the speed and the accuracy of the simulation. A gate model is basically a mathematical model that is composed of several transistor parameters and a number of equations representing the relationship between these parameters. In SPICE, these equations are used to evaluate the voltage/current at any given node. This complex modelling of gates in SPICE had a number of restrictions which included [2]:

- No approximations made to the device models

- Global convergence to the solution at every time instant

This meant that a lot of time is utilized even in the latent circuit parts resulting in exorbitantly large simulation time especially for large circuits. Thus, high levels of integration along with the shrinking technology demanded the need for a much simpler gate model which could simulate circuits much beyond the capacity limits of conventional SPICE simulators. This led to compromising the accuracy of SPICE simulations and to come up with efficient gate models with much accelerated simulation results.

Traditionally used gate models like Non-Linear Delay Models (NLDMs) are very fast but these are inaccurate due to the crude representation of the input and output signal waveforms. Also, as the effect of interconnect resistance and capacitance increases, the NLDM models do not provide good accuracy as they consider the load of a gate to be purely capacitive. Therefore, more complex models like Current Source Model (CSM) are developed which provide better accuracy by capturing and modelling the non-linear output current of the gate.

This thesis aims at developing a realistic gate model for fast post-layout simulation of circuits and to explore the various trade-off possible between the simulation accuracy, simulation speed and scalability. The proposed gate model is developed by combining a simple but fast gate model and an advanced but a slower (and more complex) gate model into one. This exploits the speed provided by the simple gate model and the accuracy provided by the advanced gate model.

## 1.2 Organization of the Thesis

The reminder of this thesis is organized into the following chapters.

Chapter 2 gives a brief description of the relevant concepts and definitions which will aid in the better understanding of the thesis.

The first part of Chapter 3 gives a wide insight into the different types of gate models in general as the aim of this thesis is to develop a gate model. It also analyses the advantages and the limitation of the various gate models and thus helps in the choosing of the simple and the advanced gate models which are later required to develop the proposed heterogeneous model. The latter part of this chapter analyses the various interconnect model that are used to model the interconnect resistance and capacitances. Chapter 4 focuses on the detailed description of the design of the proposed heterogeneous gate model. It explains the various design details of the simple and advanced gate model and their implementation.

Chapter 5 explains how the proposed gate model in this thesis can be applied for the fast and accurate simulation of circuits. This chapter also discusses the method to simulate the interconnects in a circuit.

Chapter 6 explains the experimental setup used for this thesis. The first part of this chapter gives a detail description of the circuits chosen for validation of the designed gate model. The next part explains the details of the reference reference simulation with a fast gate-level and a very accurate circuit-level simulator. The next part involves the experimental setup used for the circuit simulator using the proposed gate model. The final part of this chapter discusses the simulation results of the implemented circuit simulator.

Finally, Chapter 7 discusses the possible future work and concludes the thesis.

## Chapter 2

# Fundamentals of VLSI Circuit Modelling and Simulation

This chapter mainly focusses on the relevant concepts and definitions which are essential for the better understanding of the ideas presented in this thesis.

## 2.1 Electrical Description of VLSI circuit

### 2.1.1 Elementary Devices

#### Resistor

A resistor is a device which impedes the flow of current through a circuit. The symbol of a resistor is as shown below:

Figure 2.1: Symbol of a resistor

The unit for measuring resistance in **OHM** (represented by the Greek symbol  $\Omega$ ). Resistors have a linear current-voltage relationship [3] as stated by *Ohm's* law,

$$V = IR \tag{2.1}$$

where,

V is the voltage across the resistor,

I is the current flowing through the resistor.

#### Capacitor

A capacitor is a device that stores energy in the form of an electric field [4]. The most common type of capacitors are the parallel plate capacitors, which is made of 2 parallel plates separated by a dielectric material. When a power source forces the electric charge into the plates of the capacitor, the capacitor stores energy, resulting in a voltage V across it. The quantity capacitance is defined as the measure of electric charge (Q) required to build 1 unit of voltage (V) across the plates of the capacitor and it is given by :

$$C = \frac{Q}{V} \tag{2.2}$$

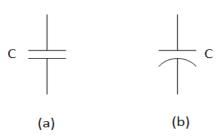

Capacitors may be polarised or non-polarised. Non-polarised capacitor is the one that has no implicit polarity and it can be connected either way in a circuit. A polarised capacitor is the one that has implicit polarity, i.e, it can be connected only in one way in a circuit.

The unit of capacitance is Farad and the symbol of a non-polarised and polarised capacitor is as shown below:

Figure 2.2: (a)Symbol of a non-polarised capacitor (b)Symbol of a polarised capacitor

A variable capacitor or a voltage controlled capacitor is the one whose capacitance can be controlled with the voltage applied across its terminals. Symbol of a variable capacitor is as shown:

Figure 2.3: Symbol of a variable capacitor

## 2.1.2 Voltage and Current sources

There exists mainly 2 kinds of energy sources in electronics - voltage source and current sources.

### DC Voltage source

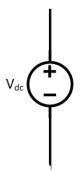

An ideal independent voltage source provides the same voltage across its terminals irrespective of the current through its terminals. Such a voltage source may produce a constant dc output voltage.

The symbol of a DC voltage source is as shown below:

Figure 2.4: Symbol of a DC voltage source with a dc voltage of  $\rm V_{dc}$

### **DC** Current Source

An ideal DC current source produces a constant dc current across its terminals no matter the voltage required across its terminals. The symbol of such a current source is as shown below:

Figure 2.5: Symbol of a DC current source with a dc current of  $I_{\rm dc}$

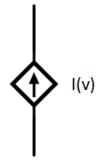

### Voltage controlled DC-current source

A voltage controlled dc current source is the one that produces a DC current at its terminals as a function of a voltage in the circuit. These type of current sources are referred to as dependent current sources. The symbol of such a source is as shown below:

Figure 2.6: Symbol of a dependent current source I(v)

### Ground

The *ground* is nothing but a circuit node to which all the voltages in a circuit are referenced to. The commonly used circuit symbols to represent the ground node are :

Figure 2.7: Symbol of ground in a circuit

## 2.2 MOSFETs

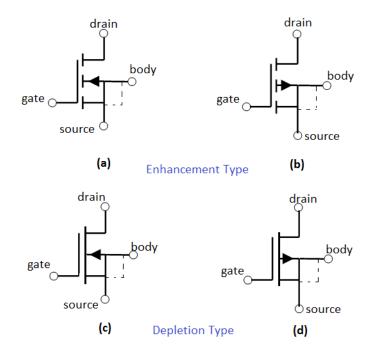

Metal Oxide Semiconductor Field Effect Transistor(MOSFET) is a type of voltage controlled Field Effect transistor. A MOSFET is a three terminal device with gate, source and drain and both the n-channel(NMOS) and p-channel(PMOS) MOSFETs are available. MOSFET devices exists in 2 mains forms :

- Depletion Type In this type of MOSFETs, a Gate-Source voltage ( $V_{GS}$ ) is required to turn "OFF" the device, i.e, these MOSFETs are similar to a "Normally Closed" switch.

- Enhancement Type These type of MOSFETs require a Gate-Source voltage (V<sub>GS</sub>) to turn the device "ON", i.e, similar to a "Normally Open" switch.

The symbol of NMOS and PMOS transistors are as shown below:

Figure 2.8: (a)n-channel enhancement MOSFET (b) p-channel enhancement MOSFET (c)n-channel depletion MOSFET (d) p-channel Depletion MOSFET

## 2.2.1 Physical Structure

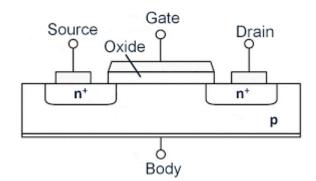

The MOSFET structure shown in fig 2.9 is fabricated on a p-type substrate which is marked as the Body. The source and the drain regions are created by two heavily doped n-type regions. A thin layer of an insulator (usually silicon dioxide,  $SiO_2$ ) is grown on the substrate, in the areas between the source and the drain [5]. A metal layer is then deposited on the oxide layer to form the gate terminal. Metal contacts are also made at the source, drain and the substrate (also called bulk or body) to bring out 4 terminals in total.

Figure 2.9: Structure of a n-channel MOSFET [6]

The substrate is generally connected to the source terminal. This is because, the substrate forms pn junctions with the source and the drain regions and normally, these junctions

are kept reverse biased. Since, the drain terminal is at a higher potential when compared to the source, these junctions can be cut-off by connecting substrate to the source. Hence, the substrate has no effect on the operation of the MOSFET and hence the reason why MOSFET is treated as a three terminal device.

## 2.2.2 Device Operation

Depending on whether the MOSFET is a depletion type or an enhancement type, the voltage applied to the gate controls the flow of current between the drain and the source. In general, conduction in a MOSFET happens when a conducting channel is formed between the drain and source regions. For an n-channel MOSFET, the channel is formed by negatively charged electrons and for a p-channel MOSFET the holes form the conducting channel.

In case of an enhancement type MOSFET, the conducting channel is very lightly doped. So, when there is no voltage applied to the gate terminal, the channel is non-conducting and hence it is in normally "OFF" state. This can be thought of as 2 back-to-back diodes that do not conduct even when a voltage (V<sub>DS</sub>) is applied between the drain and the source, as the path resistance between them is of the orders of  $10^{12}$  ohm [5]. For an n-channel enhancement MOSFET, when a positive voltage is applied at the gate terminal with respect to the source terminals (V<sub>GS</sub>), negatively charged electrons are attracted towards the gate, hence enhancing the channel thickness. At a point when V<sub>GS</sub> is greater than the **threshold voltage** V<sub>th</sub>, the channel becomes conducting with sufficient number of charge carriers. When a small positive drain-source voltage V<sub>DS</sub> is applied, current I<sub>d</sub> starts flowing through the channel formed between the source and drain and hence the MOSFET becomes conducting. The conductance of the channel increases with the excess gate voltage (V<sub>GS</sub> - V<sub>th</sub>) which is also known as the **overdrive voltage**.

When the drain source voltage  $V_{DS}$  is increased further, keeping the  $V_{GS}$  a constant, drain current  $I_d$  increases. The voltage  $V_{DS}$  appears as a voltage drop across the source and drain terminals, and therefore the voltage between the gate and the points across the channel varies from  $V_{GS}$  at source terminal to  $(V_{GS}-V_{DS})$  at the drain terminal. Thus, the voltage across the length of the channel and the depth of the channel varies. The channel is deeper at the source end and narrows down towards the drain terminal. So, with increasing  $V_{DS}$ ,  $I_d$  increases. At a particular value of  $V_{DS}$ , called the **pinch off voltage**, the channel depth at the drain end decreases to almost zero. Increasing  $V_{DS}$ beyond this point has no much effect on the shape of the channel and thus the drain current  $I_d$  saturates.

For a p-channel MOSFET, the reverse is true. When  $V_{GS}$  is 0, the device is "OFF". When a negative  $V_{GS}$  is applied to the gate terminal, the holes are accumulated in the channel and the device turns "ON", while a positive  $V_{GS}$  will turn the device "OFF".

The depletion mode MOSFET device is a less common type, which is normally "ON" when there is no gate voltage applied. For a n-channel depletion MOSFET, positive  $V_{GS}$  increases the gate current while a negative gate voltage  $-V_{GS}$  depletes the majority charge carriers which are electrons and hence the drain current decreases and eventually the device turns "OFF". Similarly, for a p-channel MOSFET, the opposite holds true.

The enhancement MOSFETs are the mostly used in integrated circuits (ICs) to produce the CMOS logic gates. This is mainly because of their low "ON" resistance and extremely high "OFF" resistance and their infinitely high input resistance which makes them excellent electronic switches. CMOS stands for Complementary MOS which consists of both PMOS and NMOS within its design.

## 2.3 SPICE

Simulation Program with Integrated Circuit Emphasis (SPICE) is a general purpose analog electronic circuit simulator [7]. It is a circuit simulation program used in IC designing in order to check for the integrity of a design and to predict the behaviour of a circuit.

As SPICE tools provided the best possible accuracy of results, they were mainly useful in the following areas :

- Validation of timing of critical paths in circuits

- Characterization of cell libraries

- Modelling and simulation of precision analog components

**SPICE** simulators are essential for the evaluation, analysis and optimization of any integrated circuit (IC) design [8, 9]. The inputs to a SPICE simulators includes a description of the circuit in the form of a netlist, a set of device models which which define the electrical behaviour of the various electronic devices used and a set of input signals.

Generally, a SPICE simulation has three main steps [10] :

- Generating the required input netlist file,

- Running the SPICE simulation,

- Measurement and analyses of the simulation results.

## 2.4 Description of a Spice Netlist

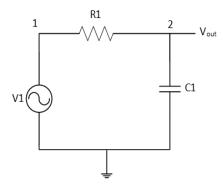

A SPICE netlist file contains a description of an electronic circuit and consists of a number of statements defining each circuit element present in the circuit. For example, consider a RC circuit with a voltage source at the input which is as shown in the figure below:

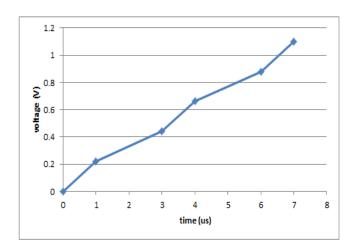

Figure 2.10: Transient Analysis of RC circuit in SPICE

Here the circuit netlist can be written as :

```

*Spice Netlist of a simple RC circuit

V1 1 0 ac 1 sin(0Voff 1Vpeak 2KHZ)

R1 1 2 30

C1 2 0 100u

.TRAN 5us 500us

.print tran v(1) v(2)

.end

```

The first line is always interpreted as a comment. **R1** and **C1** are the description of the Resistor and the Capacitor elements of the circuit. The resistor is between nodes 1 and 2 and has a value of 30 ohm, whereas the capacitor is connected between the nodes 2 and 0 and has a value of 100uF. **V1** is the AC voltage source which provides a sine wave of DC offset 0 V, a peak amplitude of 1 V and a frequency of 2kHz. The .TRAN statement is a SPICE command, which requests a transient analysis over a specified duration with a specified time-step. In this example, the duration is  $500\mu s$  and the time-step is  $5\mu s$ . This is explained in detail in the following section. **.print** is another SPICE command used to print the voltages at any particular node. In this example, the voltages at nodes 1 and 2 are printed. **.end** marks the end of the netlist.

## 2.4.1 DC, AC and Transient Analyses in SPICE

Any circuit analysis of a SPICE simulator is fundamentally based on constructing and solving the circuit equations using some complex numerical techniques [11]. The most simple analysis in SPICE is the DC analysis or the operating-point analysis. The DC analysis is also an integral part in various other types of analyses. The energy storage elements like capacitors and inductors are not considered in a DC analysis. In case they exist in the circuit description netlist, they are opened or shorted, respectively. Following this, a set of equations are formulated. Any circuit obeys 3 set of equations : Kirchoff's Current Law (KCL), Kirchoff's Voltage Law (KVL), Branch Constitutive Relation (BCR). KCL states that the sum of currents at any circuit node is zero at any instant of time. KVL states that the voltage across any branch in a circuit is equivalent to the difference between the node voltages. BCR is the equation for any electronic device which governs its equation, e.g, Ohm's law for a resistor.

Depending on the method of equation formulation in SPICE, a set of non-linear algebraic equations are formed and solved. For example, in Sparse Tableau Analysis (STA), all the formulated equations are solved simultaneously while the sparsity of the equations are exploited to the maximum. In Modified Nodal Analysis (MNA), the KVL and BCR equations are substituted in the KCL equations to form n equations in n node voltages, hence a compact set of equations are obtained. The system of equations are first linearized using the Newton's method, and then LU factorization is employed to solve the system of linear equations. The Jacobian of the system matrix for applying the Newton's method is computed and LU is factored at each iteration until the convergence is reached.

A transient analysis in a SPICE simulator determines a circuit's behaviour in the time domain. The first step of a transient analysis is the DC operating point analysis which is carried out to determine the initial conditions. Energy storage elements like capacitors and inductors present in the circuit will provide ordinary differential equations to the system of circuit equations. Thus, for a transient analysis, the SPICE simulator is required to solve a set of non-linear differential algebraic equations (DAEs). The conversion of DAEs to a set of non-linear algebraic equations is the first step in a transient analysis. This is done by integrating the DAEs in time domain. The advancement of time for integration is done by a small interval called the time step and the voltages across the inductor and the currents through capacitors are integrated using one of the several numerical integration algorithms. The most popular integration algorithms available in SPICE are Trapezoidal Rule, Backward Euler and the Gear's variable order integration. This results in a set of non-linear algebraic equations which are solved as in a DC analysis. Afterwards, the simulation proceeds by computing the next time step until the required simulation time has been reached.

## 2.4.2 Limitations of SPICE

With accuracy being given the highest priority, SPICE simulators have a number of restrictions which include the following:

- No device model approximation

- Global convergence to the solution at every time point

- Consistent time discretization for all circuit elements

These restrictions "imply" that at every time point, a system of equations representing the entire circuit is constructed. Accurate transient simulation requires very small time steps, even for large latent circuit parts. In other words, a SPICE simulator must simulate a large number of time steps and in each time step, a huge system of linear equations must be accurately solved. Hence, the speed, accuracy and reliability of the SPICE simulators is constantly challenged and the main contribution of this comes from the cost of evaluating even more complex equation based semiconductor device models (e.g. BSIM4 with hundreds of parameters) and the computational cost of linear solvers.

## 2.5 Timing Simulation in Design Flow of VLSI Circuit

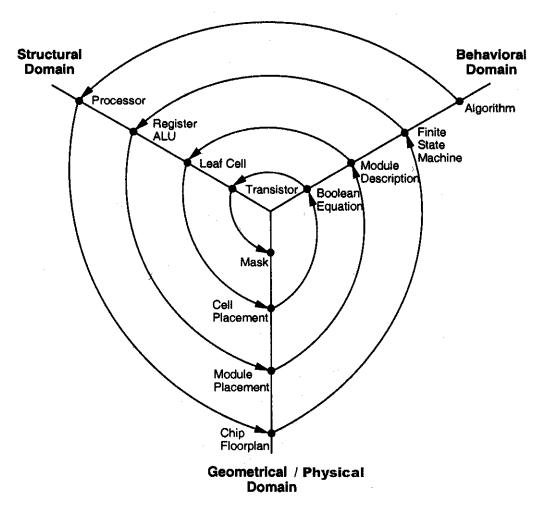

The design of a VLSI Circuit ideally starts with a specification at very high abstraction level and each design step results in a circuit description at lower abstraction level, which is shown below:

Figure 2.11: Y chart representation of IC design flow [12]

The above chart described the design flow in 3 major domains:

- Behavioural domain

- Structural domain

- Geometrical/ Physical domain

The design flow starts from the highest level and then proceeds to the lower levels (shown by arrows in the figure) [12].

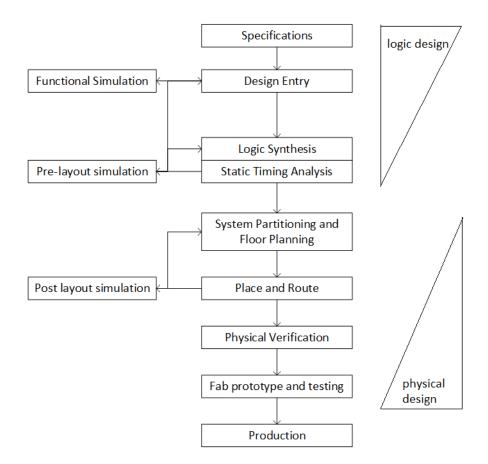

The more simplified design flow of an IC basically consists of 3 main phases :

• Logic Design

- Physical Design

- Testing

The basic design flow of an IC along with the simulation steps is as shown below :

Figure 2.12: Design Flow of ICs and simulation steps involved (adapted from [13])

In the above figure, the logic design phase usually consists of the functional simulation and the pre-layout simulation where as the physical design consists of the post-layout simulation. Finally, the testing phase aims to detect any physical faults present in the design, by making use of automatic test pattern generation (ATPG) tool to generate test vectors for verifying the design.

In general, the major steps involved in a pre and post layout timing simulation [14] of a circuit is as shown in the figure below:

Figure 2.13: Pre and post layout Simulation Steps [14]

Once the design is completed, the schematic and the layout of the design is obtained. Initially, the design is validated by conducting tests like design rule check and layout vs. schematic test. These tests mainly test for the functionality of the circuit and it does not give the actual timing behaviour of the circuit. They do not consider the effect of parasitics as well.

Next step is the parasitic extraction of the design, which is used for the actual analysis of the circuit. The parasitic information of the circuit is used to represent the accurate electrical circuit model such that simulation of the circuit gives very accurate results considering the exact amount of extra delay caused by the parasitic resistances and capacitances. These include, the violations like set-up and hold times, glitches, etc.

In the following subsections, the details about pre- and post- layout simulations shall be explained.

## 2.5.1 Functional simulation and pre-layout simulation

The logic design phase with functional and prelayout simulation processes involved is as shown in the figure below:

Figure 2.14: Steps of Logic phase of Design [13]

The first step of the design process after the design is finalized is the functional verification of the design. This only checks the functionality of the design. It does not provide any information about the timing of a circuit. As a next step, the prelayout netlist of the circuit is extracted to perform the pre-layout simulation. The Pre-layout simulations allow the circuit to be verified at a particular frequency, including the gate delays of the circuit. It allows the designers to identify and eliminate signal integrity, crosstalk and other electromagnetic compatibility (EMC) issues. This method is the most cost-effective way to design a circuit in relatively few iterations, as it occurs much early in the design process.

### 2.5.2 Postlayout Simulation

As the technology is scaling to the leading edge nodes of 28nm and below, ever more complex transistor models with hundreds of parameters are required for the accurate and reliable timing simulation of new circuit designs. These parasitic elements are now found to dominate the timing behaviour of the circuit. Furthermore, the impact of the interconnect parasitic elements on the circuit timing has increased dramatically. So it is required to accurately simulate circuits with the interconnect parasitic resistance and capacitances, but in an efficient manner.

The steps of a typical physical design of IC involving postlayout simulation process are as shown in figure below:

Figure 2.15: Steps of physical phase of Design [13]

The placement and routing process defines the exact location of the cells in a circuit. This also includes connecting cells with the interconnect material. This is followed by design rule check (DRC) which checks for rules against place and route so as to avoid any interference, cross-talk, etc [13]. Finally, post layout simulations are performed to test that the design meets the given timing requirements.

The more parasitic capacitances and resistances present in a circuit, the larger is the run time and memory requirements of the simulation [14]. Moreover, the parasitic extraction from the entire layout of the chip with all the connecting nets can result in an exorbitantly large netlist size. This may also affect the efficiency of the simulation, while possibly

contributing very little to the overall accuracy of the simulation results.

Also, as the resistance effect of the interconnects can no longer be ignored, the designers have moved from "C" to "RC" model for post-layout simulation.

Another considerable challenge is the presence of process variation effects. This introduces the need to simulate circuits for various process corners and this in turn increases the simulation run time and increases memory requirements.

### 2.5.3 Definitions related to Circuit Timing

#### 2.5.3.1 Combinational Circuits and sequential circuits

A circuit is called a **combinational circuit** if it has combinational devices like logic gates (AND, OR, etc), MUXs and has no memory elements like Flip-flops, Registers etc [15]. The figure below shows an example of a combinational circuit.

Figure 2.16: Combinational Circuit

If a circuit contains memory elements also in addition to logic gates, then such a circuit is called a **Sequential Circuit**. Example of such a circuit is as shown below:

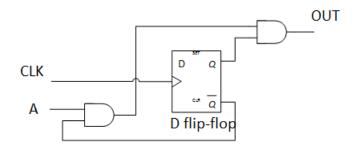

Figure 2.17: Sequential Circuit with a Flip-Flop

It is important to differentiate between the combinational and sequential circuits for timing analysis because combinational circuit timing analysis primarily deals with propagation delay of the logic gates and interconnect in the circuit only. For sequential circuit timing analysis, there are various other timing characteristics that should be satisfied which includes the setup time, hold time, and minimum clock period.

In this thesis, only combinational circuits are considered for timing analysis.

### 2.5.3.2 Delay Definitions

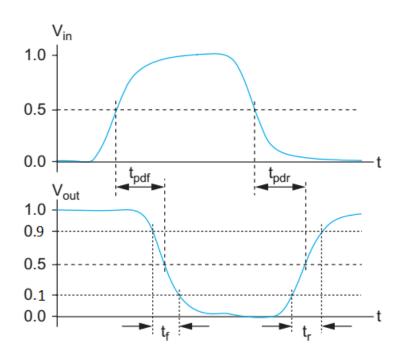

Any logic gate has some delay associated with it to transfer the voltage change at an input to the output of the gate. An ideal gate does not have any such delay, but in reality, all gates have some delay between a significant change of the gate input voltage and a significant change of the gate output voltage. This delay associated with a gate is called the **propagation delay** (or simply **gate delay**) of the gate. Consider an inverter having the following input and output waveform (with supply voltage  $V_{dd} = 1V$ ) as shown in [16] the figure below :

Figure 2.18: Input and output waveform of an Inverter [16]

Some common delay definitions with respect to the above are described below [17]:

### $t_{pdr}$ : Rise Propagation Delay

The Rise propagate delay is defined as the delay between 50% point of the input to the 50% point of the rising output of the gate.

### $t_{\rm pdf}$ : Fall Propagation Delay

The Fall propagate delay is defined as the delay between 50% point of the input to the 50% point of the falling output of the gate.

### $t_{pd}$ : Average Propagation Delay

The average propagation delay is defined as the average of the  $t_{pdr}$  and  $t_{pdf}$ . i.e,

$$t_{\rm pd} = \frac{(t_{\rm pdr} + t_{\rm pdf})}{2} \tag{2.3}$$

The transition time is the time between two neighboring  $0.1V_{dd}$  and  $0.9V_{dd}$  voltage crossing points. Depending on the sign of the voltage change, it is also called rise time or fall time.

### $t_r$ : Rise Time

The rise time is usually defined as the time taken for a rising transition to increase from the lower threshold to the upper threshold, usually  $0.1V_{dd}$  to  $0.9V_{dd}$  respectively, where,  $V_{dd}$  is the supply voltage.

### $t_f$ : Fall Time

The fall time is usually defined as the time taken for a falling transition to decrease from an upper threshold to the lower threshold, usually  $0.9V_{dd}$  to  $0.1V_{dd}$ , where  $V_{dd}$  is the supply voltage.

## Chapter 3

# State of the Art in Circuit Timing Simulation

## 3.1 Timing Model - Gate and interconnect model

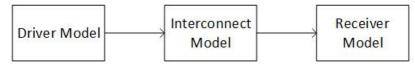

Timing models typically consist of the driver model, interconnect model and the receiver model (Fig 3.1). The driver and receiver model, together referred to as the gate model, require characterization using circuit simulators, while the interconnect model can be extracted from a layout. A timing model can be represented as follows:

Figure 3.1: Block Diagram of a timing model

The accuracy and runtime of the timing simulation is determined by the accuracy and the computational cost required to evaluate the circuit model. The circuit model is a netlist of gate and interconnect models. To find a suitable trade-off between runtime and accuracy, gate and interconnect models at different abstraction levels have been proposed.

On a broad level, simulators are generally classified into the following categories:

- Gate level simulator

- Switch level simulator

- Transistor-level

- Circuit level simulator

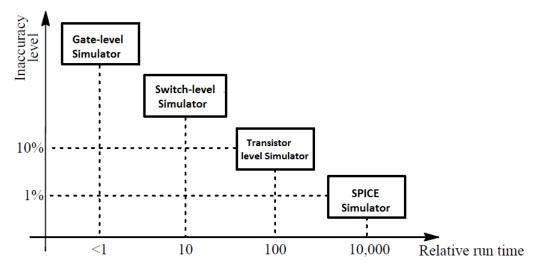

The figure below depicts the accuracy-runtime variation of the above mentioned type of simulators as compared to SPICE simulators (which is a circuit level simulator) which can be treated as "Exact" Simulators.

Figure 3.2: Relative accuracy and runtime of the timing simulation with gate and interconnect models of different abstraction levels, adapted from [11]

## **3.2** Different abstraction of simulators

In general, switch-level and gate-level simulators in the above figure sacrifice accuracy in order to achieve huge speed-up. These are mainly used for the functional simulation of the circuits, completely ignoring the timing information. "Exact" Simulators refers to those where the circuits are simulated with SPICE like tools which use complex device models (e.g BSIM4), which demands extremely large computation requirements. Hence, this type of simulation becomes practically impossible for very large circuits. Transistor-level simulator is the category of simulators which are used to determine the timing results of a circuit with a reduced accuracy than "Exact" simulators, but at a much faster speed.

### 3.2.1 Gate-Level Simulation

In gate-level simulators [18], the circuit to be simulated is modelled as a number of logic gates connected together. Each logic gate has a delay model that represents the delay of the gate, which is the time a transition at the input of the gate needs to propagate to the output of the gate. The simulation algorithm consists of a simple event driven mechanism. Gates whose inputs are exclusively connected to primary inputs are evaluated first and their outputs are updated at the appropriate time in future. Following these, once the outputs of the gates in the first logic level are updated, the fanout gates are simulated and their corresponding outputs are updated. Thus events are repeatedly scheduled and evaluated until the circuit is simulated for the required number of cycles. This kind of logic simulation forms the most integral part of any IC designing process.

#### 3.2.1.1 Non Linear Delay Models (NLDMs)

Most of the cell libraries comprise of table models which specify the delay and timing checks for various timing arcs of the cell. These table models are usually referred to as Non Linear Delay Models (NLDMs). The NLDMs are the traditionally used delay models. These models are look-up table (LUT) based models which store the gate delay and the output transition time in 2 look-up tables for various input transition times  $(t_{in})$  and output load capacitance  $C_{out}$  as the entries. The delay information is usually obtained from the Liberty (.lib) file, also called as the timing library file. However, if customised cell library is required for some particular parameter values, then the cells can be characterised by using tools like HSpice or similar tools.

The gate delay and output transition time are characterised using a circuit simulator with appropriate input stimulus to cause the output transition. These look-up tables are later used with linear interpolation technique to obtain the gate delay and output transition time while simulating the gates in a circuit.

The accuracy of the timing analysis depends on the accuracy of the cell characterisation. The delay and the output transition time LUTs constructed for NLDMs usually consist of fixed number of entries , e.g, 5 X 5 , 7 X 7 tables of  $(t_{in}, C_{out})$  pairs [19]. The value of timing information for other  $(t_{in}, C_{out})$  pair is obtained by interpolation of the nearest neighbours.

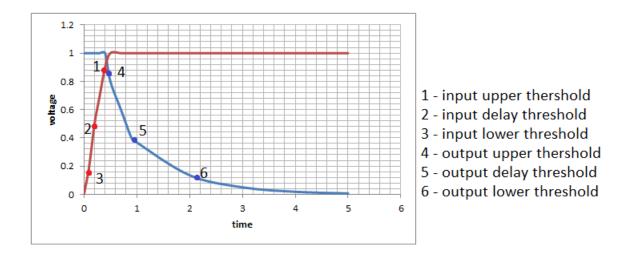

Figure 3.3: NLDM measurement points, adapted from [20]

The above picture shows the input/output measurement points. It is seen that in NLDM, only 3 cross over points are determined, 0%, 50% and the 100% points (marked as lower, delay and upper threshold in the input and the output waveforms). The gate delay is modelled as the difference between the 50% points of the input and the output waveform and the output transition time is the difference between the 0% and the 100% points of the output waveform [20].

#### 3.2.1.2 Disadvantage of NLDMs

Once the characterisation data is available, NLDMs offer extremely fast timing analysis. However, these timing models have a disadvantage that they are insufficient to reflect the non-linearities of the circuit at lower geometry. Another shortcoming of the NLDMs is that it fails to capture the effect of miller capacitance effects between the input and output nodes. This effect dominates the delay calculation for small impedance nets. Also, NLDMs fail to capture the effect of multiple input transitions at the input of a gate. Hence, the timing analysis with this model becomes very crude in cases of multiple input switching (MIS).

#### 3.2.1.3 CCS and ECSM Timing Model

To account for the inaccurate results provided by NLDMs, several other models like the ECSM and the CCS were developed. Effective Current Source Model (ECSM) is essentially based on current source modelling. It stores the various voltage sample values as a function of time.

The composite current source (CCS) provides all the necessary tools and guidelines for the accurate library characterization and validation. The CCS is the first in the EDA industry to deliver a complete open-source current based modeling solution for timing, noise and power [21]. Along with the various available parsers, characterization tools, validation tools and guidelines, these provide an open source Liberty modelling format which enables efficient characterization for cell library creators.

Some facts about the CCS include [22]:

- 1. Uses a current source for modelling the driver

- 2. Stores the gate output current as a function of time. It stores data specifically targeted at characterizing a cell's timing, noise, and power behaviour.

- 3. CCS consists of more data points as opposed to NLDM which captures only three cross-over points. Hence, CCS requires more memory than NLDMs.

- 4. The receiver model for the CCS consists of a 2-segment capacitor in order to model the Miller Effect

- 5. CCS provides much better accuracy than NLDMs

- 6. CCS enables both temperature and voltage scaling of detailed cell behaviour.

- 7. CCS addresses the existing and emerging design requirements including the physical effects of nanometer designs as well as the needs of design strategies such as multiple-voltage domains

The timing model of a cell with CCS or ECSM consists of a driver model and a receiver model along with the interconnect Model. The driver model consists of a time and voltage dependent current source in addition to the cell parasitics, and a cell output current is characterised for a given output load and input waveform The advantages of such a model are :

- Current source models are known to be very efficient in modelling the non-linear switching activity of transistors and hence prove to be very accurate.

- It is known to be better than traditional NLDM gate models in handling the complex interconnects which is prevalent in the currently existing low-power nanometer designs.

- This model provides high accuracy even when the drive resistance is much lower than the interconnect impedance as it has much more detailed information on drive resistance.

One disadvantage of these CCS and ECSM is that the characterisation is dependent on the input signal and the output load capacitance. Also, another drawback is the computation overhead caused by these models. Hence, substantial research is being made to develop these models with high accuracy and to keep the computation overhead minimal.

## 3.2.2 Switch-level Simulation

Switch level simulation is applied exclusively to digital circuits. Here each transistor is modelled as a voltage controlled resistive switch which is either on or off [23]. Each transistor is assigned a fixed conductance or resistance to describe the current driving capability of the transistor. This type of simulation is repeated for different values of the signals at the primary input. This type of simulation is efficient because its MOSFET model is very simple and very large circuits can be simulated. However, there are a few fundamental limitations linked to this simple modelling of MOSFET. Firstly, it gives very little timing information and secondly certain analog situations like charge-sharing, glitches, etc are worst handled.

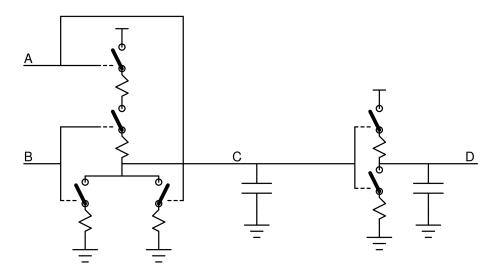

An example of a resistive switch representation of a NOR gate followed by an Inverter gate is as shown in figure below:

Figure 3.4: Resistive Switch Representation [24]

The very first switch level timing simulator was the MOTIS [25]. This simulator used Look-up tables to store the I-V characteristics of transistors. The charging current of the load capacitance was determined from these tables to evaluate the change of voltage at the output of the component connected block (CCB).

Following these, there were numerous simulators that were developed which approximated the device and circuit quantities by piecewise approximate functions. These included the E-LOGIC simulators [26] which used the method of nodal analysis, but considered the voltage to be discretized into different "levels". The various times at which the discrete voltage levels are reached at output node is found and simulation is done in an event-driven manner. To speed up the simulation process more, the MOS transistor models were further simplified and were considered as current-limited switches for very fast event-driven simulation.

## 3.2.3 Transistor level Simulation

The more complex and time-consuming type of simulators are the transistor-level simulators which model the transistors in a logic gate by describing their non-linear current and voltage equations. Thus, these simulators have much more complex gate models that provide more accurate results but these models are much simpler when compared to gate models of SPICE tools, and hence they provide faster than SPICE results. This is seen in the fig 3.2 shown above.

Some simulators based on transistor-level models include ACES and SAMSON. In ACES [27], the I-V characteristics of the transistors were stored as PWL functions, and the voltage waveform was obtained by performing explicit integration with adaptive time steps to achieve an accurate and efficient simulation. SAMSON [28] was essentially a mixed logic simulator, that used event-driven algorithms to exploit latency. This simulator provided much more accurate results than the previous ones.

#### 3.2.3.1 Current Source Models(CSM)

In an attempt to solve the accuracy of gate model in presence of process variations, noise and voltage fluctuations, Current Source Models were developed [29].

The traditionally available NLDMs are used to abstract the delay and output transition times of cells which are later used for the timing analysis. However at geometries 90nm and below, many new effects cannot be modelled properly. Some of these challenges include :

- Miller Effect

- Multiple Input Switching (MIS)

- High Impedance interconnect

- Dynamic IR drop

- Temperature Inversion

• Process Variations

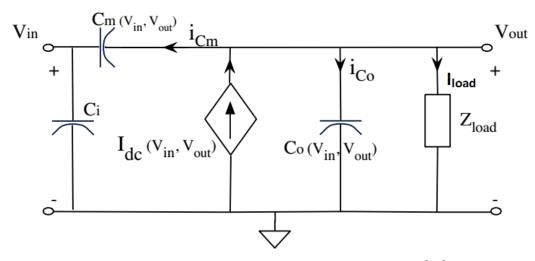

The very first CSM which was called as Blade [30], was developed using a voltage controlled current source, a capacitance and the time shift of the output voltage waveform. Since CSM is an active research topic, various models have been developed over the past years [31–34]. In [34], the logic gate was modelled to consist of a nonlinear current source, an input and output voltage dependent capacitors and a miller capacitor connected between the input and the output nodes. This model could not handle situations where a fast ramp signal is applied at the gate input a small capacitive load is present at the gate output. Thus, this work was extended to include a calibration capacitance in [35]. This was later adapted in paper to provide high accuracy even in case of multi-stage circuits [36].

## 3.2.4 Circuit level Simulation

Conventionally used simulators for postlayout simulation included traditional true spice simulators, that gave very accurate results. But as the circuit size grew and the parasitic effects of technology increased, these simulators demanded unimaginable runtime and memory. The memory and the CPU time requirements demanded by these exact simulators for simulating even moderately-sized circuits (having say 50,000 transistors) turn out to be unacceptable. This gave rise to a much accelerated class of fast spice simulators which provides an optimised run-time.

In general, these simulators sacrifice the accuracy of timing simulation (ideally in the range of 10% relative to exact simulators) to reduce the computational cost.

The properties of these fast-spice simulators include:

- 1. Use of approximate MOSFET models

- 2. Reduction of parasitic resistance and capacitance network to speed up the simulation process

- 3. Applies partition algorithms and uses partition matrix to perform hierarchical simulation

- 4. They seek to simplify the repeated evaluation of the non-linear analytic device models. Thus, sacrificing the accuracy of simulation for speed.

- 5. Employ the use of "event-driven" algorithms which incur computation only when there is activity in the circuit and only in those portions of the circuit where there is any activity and hence exploits the latency of the circuit.

- 6. Speedup over the SPICE simulators by using more simplified linearization or integration techniques.

- 7. Simulators are built using gate models that partition the circuit into "channel connected components" which are essentially sub-circuits consisting of transistors which are drain-source channel connected. The boundary of these channel connected components are either the gates of transistors, primary input of the circuits, primary outputs of circuits, power supply or ground.

These fast-spice simulators provide IC designers additional timing estimation methods which prove to be an integral part of the design methodology. They form the basis for timing and power estimation methods in the design of ICs and they have become an integral part of any design process of ASICs, memory, etc.

## 3.3 Interconnect Modelling

In the past history of Integrated Circuits, the interconnect wires were considered only in certain special cases or when some high-precision analysis is performed. But, as the device dimensions are constantly reducing and the speed of the circuits are aimed to be increased, the parasitic effects of the wire interconnects can no more be neglected [37]. This is further aggravated by the fact that the improving technology has enabled the manufacturing of larger die sizes economically feasible, which in turn means an increased average length of the interconnect wires and hence the increased parasitic effects of these wires. Thus, it is becoming an essential need to consider and simulate the wire interconnects as well in addition to simulating the various gates in the circuits. In other words, with continuous scaling, the delay contributed by the interconnects or the wires is becoming a significant contributor in the total delay of the circuit.

An ideal wire is the one that has no parasitic elements like parasitic resistances or parasitic capacitances associated with it and hence it has no effect on the electrical properties of the circuit [37]. Such ideal wires are considered to be equi-potential in the sense that a voltage applied to one end of the wire propagates immediately to the other end even if separated by a distance. This is the most simplistic model of a wire and it is usually considered in the early stages of design when it is more important to analyse the behaviour of the transistors. However, with constantly shrinking technology, and for the accurate simulation of circuits, it is important to consider more complex model for the wires so as to analyse their effect on the electrical properties of the circuit.

To study the effects of interconnects on the simulation of a circuit, it is important to accurately approximate the actual behaviour of the wire as a function of its parameters. These are called as interconnect models which may vary from being very simple to very complex depending on the accuracy requirements.

The basic idea of interconnect modelling is to produce a reduced order model of the interconnect networks which captures the original interconnect behaviour up to a particular frequency. Reduced order models of large RC networks can be plugged into any timing simulator and simulated more efficiently with the non-linear drivers and receivers.

Some examples of the interconnect models are:

- Lumped C model

- Lumped RC model

- Distributed RC model [37]

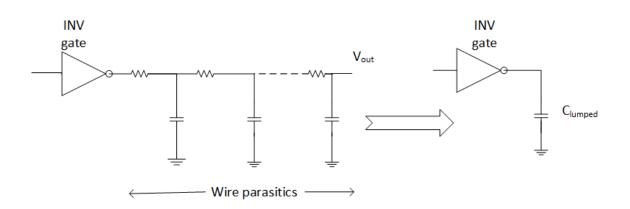

#### 3.3.1 Lumped C model

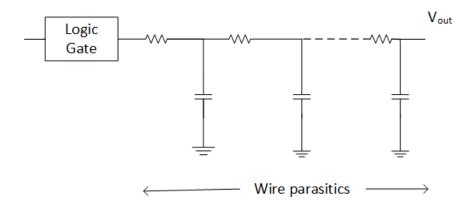

The simulation of interconnects for the simple gate model is done by reducing the RC interconnect network into a lumped C model. This means that the entire RC network of the interconnect wire is represented by using a single capacitance as shown in figure below:

Figure 3.5: RC network reduction using Lumped C model, adapted from [37]

The lumped C model considers only the dominating capacitive parasitics of a wire and assumes the resistive components to be negligibly small. The distributive capacitances of a wire are lumped together into a single capacitance as shown in the figure above. This model still represents the wire as a equipotential region and it only changes the capacitive loading effect on the driving gate. This wire model is quite simple and yet effective and it is the most commonly used wire model in the analysis of ICs.

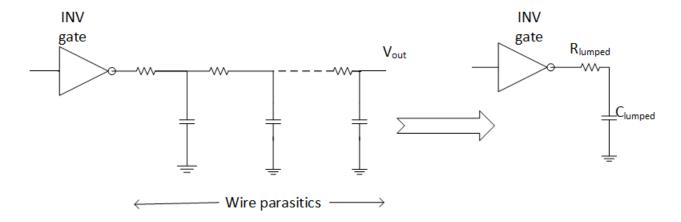

#### 3.3.2 Lumped RC Model

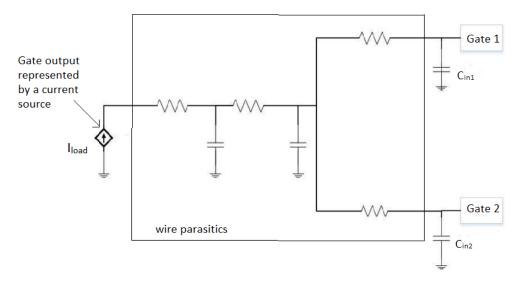

For very small on-chip wires of the sizes of few mm length, the resistance effect is quite significant. The equipotential assumption assumed in the simple lumped C model is not adequate anymore and hence a RC model is adopted.

The simplest way to model the interconnect resistances and capacitances using the lumped RC model is to lump all resistors of the net into 1 resistor and to lump all capacitances to 1 capacitance. Thus, the model can be represented as follows:

Figure 3.6: RC network reduction using Lumped RC model, adapted from [37]

The  $R_{\rm lumped}$  and  $C_{\rm lumped}$  represent the overall lumped resistance and capacitance of the interconnect.

## Chapter 4

# Design of a Heterogeneous Gate Model

This chapter presents the proposed heterogeneous gate model for fast and accurate timing simulation. An abstract description of the model is presented in section 4.1. The following section 4.2 shows the waveform model, which defines the inputs and the output of this model during simulation. The section 4.3 defines the simple gate model and the sections 4.4 and 4.5 describe the details of the advanced gate model of the proposed heterogeneous gate model.

In this thesis, we shall consider only the 2-input NOR gate and the inverter gate for all the following sections that follow. This ensures that all circuits used for the validation of this model are synthesized using these 2 gates only.

## 4.1 Model Description

The proposed heterogeneous gate model combines a very fast gate-level model designed for single input switching with a complex but very accurate transistor-level model.

#### 4.1.1 Overview

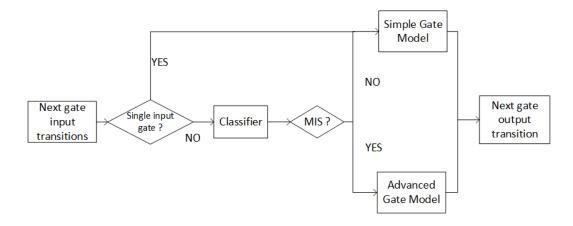

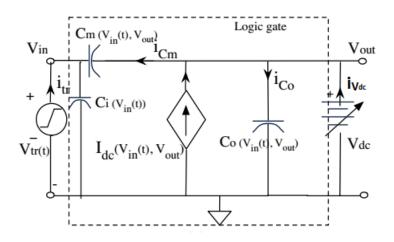

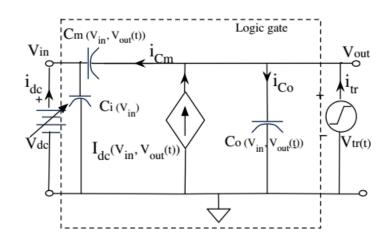

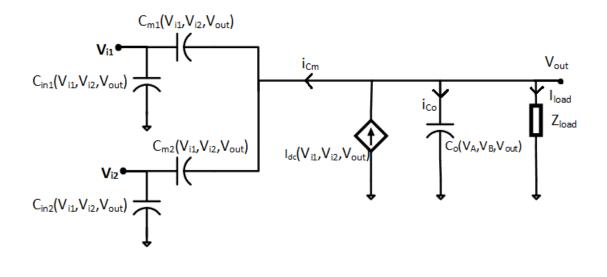

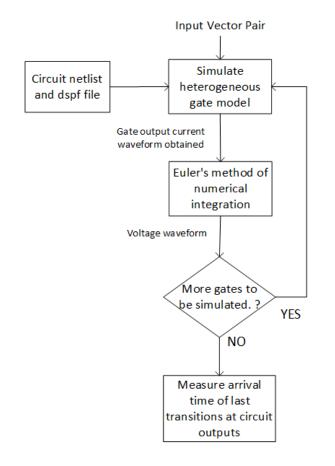

The heterogeneous gate model proposed in this thesis uses a simple gate model for single input gates (Inverter Gate) and in case of a multiple input gate, it uses a classifier to determine whether a multiple input switching (MIS) case is detected at the gate input. In case of MIS scenario being detected, the advanced gate model based on current source model (CSM) is simulated to compute the next gate output transition as this model considers the effect of MIS, which the simple gate model fails to capture. Thus, the heterogeneous gate model consists of a simple gate model based on NLDM, an advanced gate model based on CSM and a classifier to choose between the 2 when a MIS case occurs. Note that this gate model takes the voltage waveform at the gate inputs and the gate output as the input and produces the gate output current waveform as result.

The idea of the proposed heterogeneous gate model can be represented as shown in the figure below:

Figure 4.1: Proposed heterogeneous gate model for efficient timing simulation

The purpose of combining gate models of different abstraction levels is to explore the trade off between the speed of simulation using the simple gate model and the accuracy achieved using the advanced gate model. The classifier thus plays an important role in achieving this trade-off between the speed and accuracy of simulation.

The primary idea of using the classifier for a multi-input gate lies in the fact that although NLDM provides very fast computation results, these results are inaccurate, especially in cases where multiple input switching occurs. The timing libraries used by the NLDMs have the pin-to-pin delays of each gate characterized for single input switching case only. The impact of simultaneous switching of the gate inputs can cause significant errors in the timing estimates of the gate [38]. Since this effect of multiple input switching is not captured in NLDMs, another advanced gate simulation algorithm is used in such cases compute the next gate output transition more accurately.

## 4.1.2 Impact of Multiple Input Switching on Gate Delay

Given that the simple gate model calculates the next gate output transition much faster when compared to the advanced gate model, it is most desirable to simulate all gates using the simple model except for those cases, where simultaneous switching of the gate inputs occurs. To avoid the application of the advanced gate model in cases where the simple gate model provides sufficient accuracy, it is necessary to design the classifier in such a way that it chooses the time consuming advanced gate model only when it is necessary.

For any basic logic gate, we can define the *Controlling* and the *Non-Controlling* values. The controlling value completely determine the value at the output of the gate. Hence, the input transition can either be *Controlling* to *Non-Controlling* (CTN) or *Non-Controlling* to *Controlling* (NTC) depending on its effect at the output of the gate. For example,

for a NOR gate, the *Controlling* value is 1 and the *Non-Controlling* value is 0. Thus, a falling transition is a CTN transition, while a rising transition is a NTC transition.

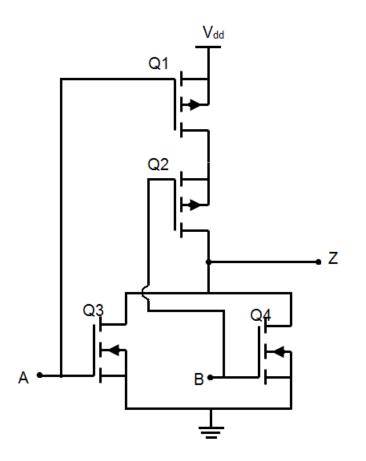

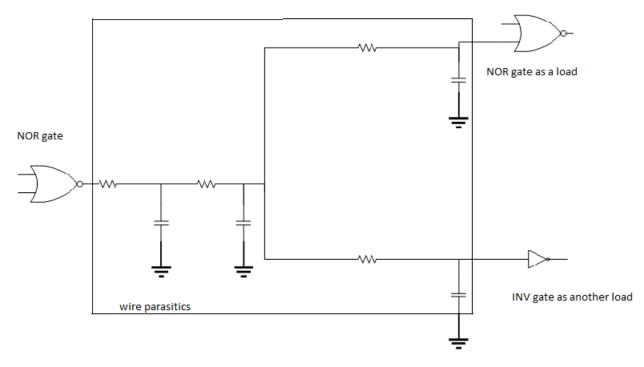

Consider the cmos 2-input NOR gate as shown below:

Figure 4.2: CMOS NOR gate

In the above diagram of a NOR gate, Q1 and Q2 are p-channel MOSFET transistors and Q3 and Q4 are p-channel MOSFET transistors. The inputs of the NOR gate are denoted by A and B and the output of the gate is denoted by Z.

When only one gate input (A or B) has a transition and the other input remains at the non-controlling value, the delay of the gate is called the single input switching (SIS) delay. This delay can be determined quite accurately using a simple gate model like NLDM.

When both A and B have NTC (rising) transitions, both the n-channel MOSFET (Q3 and Q4) are conducting in parallel. Therefore, the gate is discharged with twice the current. In this case, the output arrival time is determined by the earliest arriving signal. Similarly, when both inputs A and B have a CTN (falling) input transitions, then the current starts flowing only when both the p-channel MOSFET are conducting. Therefore, the latest arriving signal determines the arrival time at the gate output.

When multiple inputs of the gate switch, it is necessary to consider whether they switch in the same direction or not. If multiple inputs switch in opposite directions, they either do not propagate a signal to the output or they produce a glitch at the output of the gate. Hence, it is more important to consider those multiple input transitions which happen in the same direction.

#### 4.1.3 Definition of Classifier

When the gate to be simulated is a multi-input gate, initially the transitions at the input of the gate are analysed to determine whether they cause a transition at the output of the gate. If a transition occurs at the gate output due to a transition at one of the gate inputs while the other gate inputs remain stable during that time, then the gate output transition is computed according to the simple gate model.

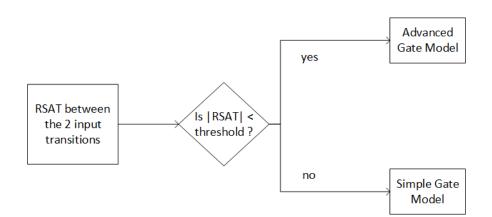

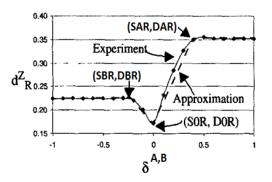

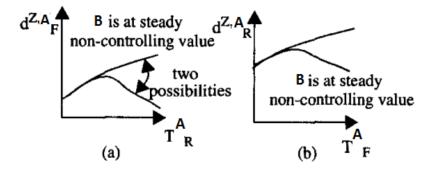

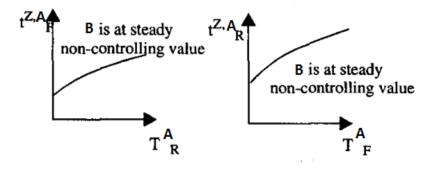

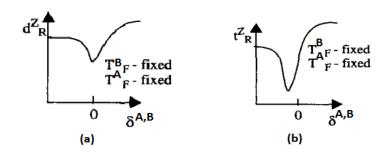

However, if a gate output transition is caused due to the combined effect of multiple gate inputs switching almost simultaneously, the simple gate model cannot provide sufficient accuracy and the classifier has to choose the advanced gate model for the computation of this output transition. From the above section, it can be seen that the most important parameter that determines the MIS effect on the gate delay is the relative arrival time between the 2 input transitions. Hence the classifier must consider this parameter to determine MIS scenario.